- •Contents

- •Preface

- •Related Documents

- •Typographic and Syntax Conventions

- •Creating HDL Modules for CDBA Cellviews

- •Creating HDL Data as You Save CDBA Cellviews

- •Creating HDL Data from Pre-existing CDBA Cellviews

- •Quick-Start Tutorial

- •The Circuit

- •AMS Designer Tools

- •Setting Up the Tutorial

- •Running from a Script

- •Running within the AMS Environment

- •Opening the Command Interpreter Window

- •Netlisting and Compiling

- •Elaborating and Simulating the Design

- •Summary

- •Setting Up the AMS Environment

- •Overview

- •The hdl.var File

- •The ams.env Files

- •AMS Designer Supports Design Management

- •Specifying the Text Editor to Use

- •Specifying Fonts for the Cadence Hierarchy Editor

- •Preparing to Use AMS Designer from the Hierarchy Editor

- •Netlisting

- •Netlisting Modes Supported by the AMS Netlister

- •Automatic Netlisting of a Cellview

- •Netlist Updating and Netlisting of Entire Designs

- •Netlisting from the UNIX Command Line

- •Library Netlisting

- •Netlisting of Cells in Response to Changes in CDF

- •Preparing Existing Analog Primitive Libraries for Netlisting

- •Specifying the Behavior of the Netlister and Compilers

- •Opening the AMS Options Windows

- •Setting Netlister Options from the Hierarchy Editor

- •Opening the CIW AMS Options Window

- •Setting Compiler Options

- •Viewing the AMS Netlister Log

- •Understanding the Output from the AMS Netlister

- •How Inherited Connections Are Netlisted

- •Inherited Signal Connections

- •Inherited Terminal Connections

- •Instance Values for Inherited Connections

- •Third-Party Tools and Other Cadence Tools

- •How Aliased Signals Are Netlisted

- •How m-factors (Multiplicity Factors) Are Netlisted

- •How Iterated Instances Are Netlisted

- •Passing Model Names as Parameters

- •Effect of the modelname, model, and modelName Parameters

- •Handling of the model* and componentName Parameters

- •Precedence of the model* and componentName Parameters

- •Specifying Parameters to be Excluded from Netlisting

- •Ignoring Parameters for Entire Libraries

- •Example: Specifying Parameters to Ignore

- •Ensuring that Floating Point Parameters Netlist Correctly

- •Working with Schematic Designs

- •Setting Schematic Rules Checker Options for AMS Designer

- •Creating Cellviews Using the AMS Environment

- •Preparing a Library

- •Creating the Symbol View

- •Using Blocks

- •Descend Edit

- •Inherited Connections

- •Global Signals in the Schematic Editor

- •Inherited Connections in a Hierarchy

- •How Net Expressions Evaluate

- •Net and Pin Properties

- •groundSensitivity and supplySensitivity Properties

- •Making Connect Modules Sensitive to Inherited Connection Values

- •Using External Text Designs

- •Overview of Steps for Using External Text Designs

- •Bringing Modules into a Cadence Library

- •Specifying the Working Library

- •Compiling into Libraries

- •Compiling into Temporary Libraries

- •Listing Compiled Modules

- •Using Text Blocks in Schematics

- •Using Modules Located in a Cadence Library

- •Preparing for Simulation

- •Using Analog Primitives

- •Using SPICE and Spectre Netlists and Subcircuits

- •Preparing to Use SPICE and Spectre Netlists and Subcircuits

- •Placing SPICE and Spectre Netlists and Subcircuits in a Schematic

- •Using Test Fixtures

- •Creating and Using a Textual Test Fixture

- •Creating a Textual Test Fixture

- •Using a Test Fixture

- •Example: Creating and Using a Test Fixture

- •Using Design Configurations

- •Ensuring HDL Design Unit Information Is Current

- •Preparing a Design for Simulation

- •Overview of AMS Design Prep

- •What AMS Design Prep Does to Prepare a Design for Simulation

- •When to Use AMS Design Prep

- •Specifying the Behavior of AMS Design Prep

- •Setting Options for Global Design Data

- •Specifying Global Signals

- •Specifying Design Variables

- •Specifying Model Files to Use During Elaboration

- •Running AMS Design Prep

- •The cds_globals Module

- •Global Signals

- •Design Variables

- •Setting Elaborator Options

- •Setting Simulator Options

- •Setting Waveform Selection Options

- •Creating Probes

- •Selecting Instances from the Virtuoso Schematic Editing Window

- •Selecting Buses

- •Selecting Instances from the Scope Navigator

- •Copying and Pasting Within Tables

- •Elaborating and Simulating

- •Viewing Messages

- •Plotting Waveforms After Simulation Ends

- •Starting the SimVision Waveform Viewer

- •Plotting Waveforms Selected on a Schematic (Direct Plot)

- •Using the amsdesigner Command

- •Examples

- •Producing Customized Netlists

- •Producing Customized Netlists

- •Identifying the Sections of a Netlist

- •Using ams.env Variables to Customize Netlists

- •Using Netlisting Procedures to Customize Netlists

- •Examples: Problems Addressed by Customized Netlists

- •Example: Adjusting Parameter Values to Account for Number of Fingers

- •Example: Using Symbols that Represent Verilog Test Code

- •Data Objects Supported for Netlisting

- •Netlister Object

- •Formatter Object

- •Cellview Object

- •Parameter Object

- •Instance Object

- •SKILL Functions Supported for Netlisting

- •Default Netlisting Procedures

- •Netlisting Helper Functions

- •Variables for ams.env Files

- •How AMS Designer Determines the Set of Variables

- •Why AMS Designer Uses ams.env Files, Not .cdsenv Files

- •List of ams.env Variables

- •Detailed Descriptions of ams.env Variables

- •aliasInstFormat

- •allowDeviantBuses

- •allowNameCollisions

- •allowSparseBuses

- •allowUndefParams

- •amsCompMode

- •amsDefinitionViews

- •amsEligibleViewTypes

- •amsExcludeParams

- •amsExpScalingFactor

- •amsLSB_MSB

- •amsMaxErrors

- •amsScalarInstances

- •amsVerbose

- •analogControlFile

- •bindCdsAliasLib

- •bindCdsAliasView

- •cdsGlobalsLib

- •cdsGlobalsView

- •checkAndNetlist

- •checkOnly

- •checktasks

- •compileAsAMS

- •compileExcludeLibs

- •compileMode

- •connectRulesCell

- •connectRulesCell2

- •connectRulesLib

- •connectRulesView

- •detailedDisciplineRes

- •discipline

- •excludeViewNames

- •hdlVarFile

- •headerText

- •ieee1364

- •ifdefLanguageExtensions

- •incdir

- •includeFiles

- •includeInstCdfParams

- •initFile

- •instClashFormat

- •iterInstExpFormat

- •language

- •lexpragma

- •logFileAction

- •logFileName

- •macro

- •maxErrors

- •messages

- •modifyParamScope

- •ncelabAccess

- •ncelabAnnoSimtime

- •ncelabArguments

- •ncelabCoverage

- •ncelabDelayMode

- •ncelabDelayType through ncelabMessages

- •ncelabMixEsc

- •ncelabModelFilePaths

- •ncelabNeverwarn through ncelabVipdelay

- •ncsimArguments

- •ncsimEpulseNoMsg through ncsimExtassertmsg

- •ncsimGUI

- •ncsimLoadvpi through ncsimStatus

- •ncsimTcl

- •ncsimUnbuffered through ncsimUseAddArgs

- •ncvhdlArguments

- •ncvlogArguments

- •ncvlogUseAddArgs

- •netClashFormat

- •netlistAfterCdfChange

- •netlistMode

- •netlistUDFAsMacro

- •neverwarn

- •noline

- •nomempack

- •nopragmawarn

- •nostdout

- •nowarn

- •paramDefVals

- •paramGlobalDefVal

- •pragma

- •processViewNames

- •prohibitCompile

- •runNcelab

- •runNcsim

- •scaddlglblopts

- •scaddltranopts

- •scale

- •scalem

- •scannotate

- •scapprox

- •scaudit

- •sccheckstmt

- •sccmin

- •sccompatible

- •scdebug

- •scdiagnose

- •scdigits

- •scerror

- •scerrpreset

- •scfastbreak

- •scgmin

- •scgmincheck

- •schomotopy

- •sciabstol

- •scic

- •scicstmt

- •scignshorts

- •scinfo

- •scinventory

- •sclimit

- •sclteratio

- •scmacromod

- •scmaxiters

- •scmaxnotes

- •scmaxrsd

- •scmaxstep

- •scmaxwarn

- •scmethod

- •scmodelevaltype

- •scmosvres

- •scnarrate

- •scnotation

- •scnote

- •scopptcheck

- •scpivabs

- •scpivotdc

- •scpivrel

- •scquantities

- •screadic

- •screadns

- •screlref

- •screltol

- •scrforce

- •scscale

- •scscalem

- •scscftimestamp

- •scscfusefileflag

- •scskipcount

- •scskipdc

- •scskipstart

- •scskipstop

- •scspeed

- •scstats

- •scstep

- •scstop

- •scstrobedelay

- •scstrobeperiod

- •sctemp

- •sctempeffects

- •sctitle

- •sctnom

- •sctopcheck

- •sctransave

- •scusemodeleval

- •scvabstol

- •scwarn

- •scwrite

- •simRunDirLoc

- •simVisScriptFile

- •status

- •templateFile

- •templateScript

- •timescale

- •update

- •use5xForVHDL

- •useDefparam

- •useNcelabNowarn

- •useNcelabSdfCmdFile

- •useNcsimNowarn

- •useNowarn

- •useScaddlglblopts

- •useScaddltranopts

- •useScic

- •useScreadic

- •useScreadns

- •useScwrite

- •useSimVisScriptFile

- •useProcessViewNamesOnly

- •verboseUpdate

- •vlogGroundSigs

- •vloglinedebug

- •vlogSupply0Sigs

- •vlogSupply1Sigs

- •wfDefaultDatabase

- •wfDefInstCSaveAll

- •wfDefInstCSaveLvl

- •wfDefInstSaveCurrents

- •wfDefInstSaveVoltages

- •wfDefInstVSaveAll

- •wfDefInstVSaveLvl

- •wfDefInstVSaveObjects

- •Updating Legacy SimInfo for Analog Primitives

- •The ams Fields

- •Special Handling of model, modelName, modelname, and componentName

- •Converting an Existing Analog Primitive Library

- •Designing for Virtuoso AMS Compliance

- •Terminals

- •Buses

- •Component Description Format

- •Parameters

- •Using Inherited Parameters

- •Using Cell Parameters

- •Parameterized Cells

- •VHDL-AMS Component Declarations

- •Properties

- •Properties to Avoid Completely

- •Avoid the portOrder Property Unless Required by Special Circumstances

- •Properties to Use Only in AMS Compatibility Mode

- •Properties That Have No Special Meaning in the AMS Environment

- •Properties Fully Supported by the AMS Environment

- •SKILL Functions

- •amsCheckCV

- •amsIsPresent

- •amsNetlist

- •amsProcessCellViews

- •amsUIOptionsForm

- •amsUIRunNetlisterForm

- •ddsCvtAMSTranslateCell

- •ddsCvtAMSTranslateLib

- •ddsCvtToolBoxAMS

- •vmsUpdateCellViews

- •Customization Variables

- •schHdlNotCreateDB

- •schHdlUseVamsForVerilog

- •vmsAnalysisType

- •vmsCreateMissingMasters

- •vmsNcvlogExecutable

- •vmsPortProcessing

- •vmsRunningInUI

- •vmsTemplateScript

- •vmsVerboseMsgLevel

- •Compiling Cadence-Provided Libraries

- •Purpose of the amsLibCompile Tool

- •Running the amsLibCompile Tool Manually

- •Example

Virtuoso AMS Environment User Guide

Elaborating, Simulating, and Plotting Results

A type-in field with focus, such as the row2 Name field in this example,

restricts the focus to that field. If one of the fields has focus, you can remove the focus by pressing Escape.

b.Highlight the rows that you want to copy by clicking the row numbers on the left side.

After you highlight one row, you can highlight additional rows by Shift clicking (for contiguous rows) or Control clicking (for scattered rows).

c.Right click to open the pop-up menu and choose Copy.

d.Position the cursor over the row where you want to paste the copied row (or, if you are pasting multiple rows, over what is to be the topmost pasted row).

e.Right click to open the pop-up menu and choose Paste.

■To copy all or part of a type-in field,

a.Click the type-in field to be copied. The focus moves to that field.

b.Within the type-in field, highlight the part of the field to be copied.

c.Right click to open the pop-up menu and choose Copy.

d.Click the target type-in field. Focus moves to the target field.

e.Right click to open the pop-up menu and choose Paste.

Elaborating and Simulating

To use AMS Designer to simulate a design, you must have a license for the AMS simulator (product number 70001). If you attempt to simulate a design without a license, the simulation appears to run indefinitely. AMS Designer does not produce an obvious message to help you understand the problem, although the tool does place a message in the ncsim.log file.

To elaborate and simulate your design,

1. From the Cadence hierarchy editor, choose AMS – Run Simulation.

April 2004 |

286 |

Product Version 5.3 |

Virtuoso AMS Environment User Guide

Elaborating, Simulating, and Plotting Results

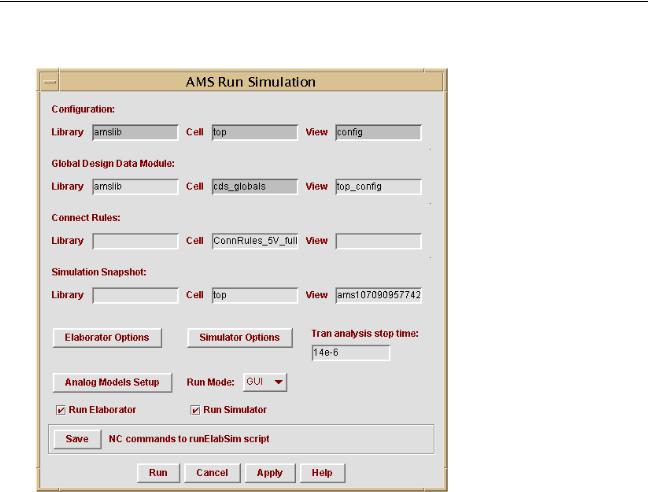

The AMS Run Simulation form appears.

2.Ensure that the correct library, cell, and view are specified in theConfiguration section.

3.Ensure that the correct library and view are specified in theGlobal Design Data Module section.

The cds_globals module, which is created by AMS Design Prep, contains information about global signals and design variables. The cell is always named cds_globals and, by default, the view name is created from the top-level cell name and the config name, using the format topCell_configView.

4.In the Connect Rules section, specify the connectrules module to be used.

The connectrules module tells the elaborator when to insert connection modules. Which default connectrules module appears in the form depends on the version of the AMS simulator that you are using. For more information, see “Using Connect Modules”, in the “Mixed-Signal Aspects of Verilog-AMS” chapter of theCadence

Verilog-AMS Language Reference.

5.(Optional) Change the information in the Simulation Snapshot section.

April 2004 |

287 |

Product Version 5.3 |

Virtuoso AMS Environment User Guide

Elaborating, Simulating, and Plotting Results

The default snapshot view name incorporates a time mark to ensure that existing snapshots in the library are not accidentally overwritten.

You might want to save the snapshot under a simpler, more convenient name if you plan to simulate a different existing snapshot, or if you want to resimulate this snapshot from a different run directory.

Note: Before simulating, be sure that the View field correctly names a valid snapshot view. If you type in a snapshot view that does not exist in the library and attempt to simulate, the simulation fails without issuing an error message.

6.(Optional) Click Elaborator Options if you want to change those options.

7.(Optional) Click Simulator Options if you want to change those options.

8.(Optional) Enter a stop time in the Tran analysis stop time field if the stop time has not been specified in some other way, such as by using a simulation control file.

9.(Optional) Click Analog Models Setup if you want to change the models that are used in the design

10.If you want to run the elaborator, ensure that Run Elaborator is checked.

11.If you want to run the simulator, ensure that Run Simulator is checked.

12.In the Run Mode cyclic field, choose whether you want to simulate in GUI (interactive), Tcl, or batch mode.

GUI Opens a graphical interface that allows you to interact with the simulator by using buttons, menus, and Tcl commands.

Tcl Opens a text-based window where you can use the Cadence-supported Tcl commands to interact with the simulator. (For a description of the Tcl commands, see Appendix B, “Tcl-Based Debugging,” in theVirtuoso

AMS Simulator User Guide.) (Note: If the Tcl window does not appear, verify that the xterm command is in your path.)

■If you have not specified a Tcl input script, the window opens and waits for you to enter a Tcl command.

■If you have specified a Tcl input script, the script runs as soon as the window opens. If the script contains an exit or finish command, the the window closes after the script runs. If the script does not cause the simulator to exit, the window remains open, waiting for you to enter a Tcl command.

To close the window, type the exit or finish commands.

April 2004 |

288 |

Product Version 5.3 |

Virtuoso AMS Environment User Guide

Elaborating, Simulating, and Plotting Results

Batch Runs the simulation in the background. This mode, which does not allow you to interact with the simulator, usually simulates more quickly than the other modes.

13.(Optional) Click Save to write the ncelab and ncsim commands to the runElabSim script in the run directory.

Writing the commands to a file makes it possible for you to reuse the commands later.

14.Click Run.

Viewing Messages

AMS Designer places the ncelab.log, ncsim.log, ncvhdl.log, and ncvlog.log files in the run directory. You can view them there by using a tool such as vi. If your primary interest is in viewing warnings and errors found in these log files, you can use the following steps instead.

1.From the Cadence hierarchy editor, choose AMS – Logfile Viewer – Simulator Log

Files.

April 2004 |

289 |

Product Version 5.3 |