- •Қ.М. Мұқашев, к.С. Шадинова электроника және схематехника негіздері

- •Студенттің жұмыс орыны

- •Жұмыстың қысқаша мазмұны Зертханалық стенд

- •Электрондық осциллограф

- •Стендті ток көзімен қоректендіру

- •Құрама электр өлшеуіш прибор

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •2 . Құрама электр өлшеУіш прибор

- •Жұмыстың қысқаша мазмұны

- •Құрама электрөлшеу приборының конструкциясы

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •3. Импульстық сигналдар

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •4. Импульстық сигналдарды түрлендіру

- •Жұмыстың қысқаша мазмұны

- •Жұмыстың орындалу тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •5. Диодты және транзисторлы кілттер

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •6. Диодты – транзисторлы логика

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •7. Логикалық элементтердің интегралдық микросхемалармен құрылуы

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •8. Импульстық сигналдардың генераторлары

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •2 Және – емес логикалық элементтермен мультивибратордың схемасын құру және зерттеу.

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •9. Асинхронды және тактілік rs – триггерлер

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •10. Құрама rs- d және jk- триггерлер

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •11. Реверсивті санауыштар

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •4 Разрядты екілік санауыш.

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •12. ЫғыстыруШы регистр

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Бақылау сұрақтары

- •Әдебиеттер

- •13. Шифратор және Мультиплексор

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •14. Үш кірісті толық дешифратор

- •Студент білу тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •15. Бір разрядты екілік қосуыштар

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау ережесі

- •Үй тапсырмасы

- •Пысықтау сұрақтары

- •Әдебиеттер

- •16. Арифметикалық – логикалық құрылғы

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Пысықтау сұрақтары

- •Үй тапсырмасы

- •Әдебиеттер

- •17. Цифрлық мағлұматты бейнелеу

- •Студент игеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Материалды толық меңгеру үшін алдын-ала игерілетін сұрақтар а) базистік білім бойынша:

- •Студенттің оқытушымен бірге орындайтын жұмысы

- •Студенттің бастапқы және қорытынды білім деңгейін қадағалау

- •Әдебиеттер

- •18. Оперативті жадылық құрылғы

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Пысықтау сұрақтары

- •Үй тапсырмасы

- •Әдебиеттер

- •19. Цифрлық-аналогты түрлендіргіш

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Бақылау сұрақтары

- •Әдебиеттер

- •20. Аналогты – цифрлық түрлендіргіш

- •Студент білуі тиіс:

- •Студент меңгеруі тиіс:

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау тәртібі

- •Пысықтау сұрақтары

- •Әдебиеттер

- •21. Айнымалы токтың түзеткіштері

- •Жұмыстың қысқаша мазмұны

- •Жұмысты орындау әдістемесі

- •Пысықтау сұрақтары

- •Үй тапсырмасы

- •Әдебиеттер

- •Қосымшалар

- •1. Радиоаппаратураның құрама элементтерін ауыстыру әдістемесі

- •2. Жартылай өткізгіш приборларды таңбалау тәртібі

- •3. Интегралдық микросхемаларды таңбалау принциптері

- •4. Шетелдік имс таңбалау ерекшеліктері

- •5. Логикалық элементтердің графикалық шартты белгілерінің стандарттары

- •6. Сәуле шығарушы диодтарды таңбалау принципі

- •7. Стендтегі микросхемалардың графикалық бейнеленуі және контактыларының орналасуы

- •8. Стендтің толық техникалық нұсқауы

- •Стендтің конструкциясы

- •Қорытынды

- •Әдебиеттер

- •Мазмұны

- •Электроника және схематехника негіздері

Студент меңгеруі тиіс:

Әр түрлі санды кірістік және шығыстық тізбектері бар шифратордың логикалық функциясын құру және минимизациялау жолдарын;

Шифратордың ақиқат кестесін құрып, оның жұмыс істеу қабілетін тексеруді;

Мультиплексордың логикалық функциясын құруды;

Шифратор мен мультиплексордың схемасында кездесетін ақауларды тауып жөндеуі.

Шифратор мен мультиплексордың жұмысын олардың құрылымдық схемасы бойынша талдауды;

Мультиплексор мен шифраторды қажетті жерде пайдалануды;

Қажет болған жағдайда шифратордың бір түрінен екінші түріне ауысуды.

Жұмыстың қысқаша мазмұны

Шифратор (фр. Coder) - кірісіндегі бірлік команданы шығысындағы екілік санақ жүйесіндегі кодқа түрлендіруге арналған электрондық құрылғы. Толық шифратордың кірісінің К және шығысының n сандарының арасындағы қатынас K=2n теңдеуімен анықталынады. Сондықтан кірістерінің саны көп болатын шифраторларды құру қиынға түседі, яғни мұндай шифраторлар кішігірім сандар мен символдарды екілік санақ жүйесіне түрлендіру үшін қолданылады.

Шифраторлар мағлұматты цифрлы жүйелерге енгізуге арналған әр түрлі құрылғыларда кеңінен қолданылады. Сол үшін осы құрылғының әрбір пернесі (клавиша) шифратордың кезекті кірісімен байланыстырылады. Таңдаған пернені басу барысында шифратордың сәйкес кірісінде бірлік потенциал туындайды. Осы потенциал шифратордың шығу тізбектеріндегі екілік санақ жүйесіндегі кодпен бейнеленетін мағлұматқа тасымалданады. Бұл мағлұматтың мәні пернедегі әр бір символға сәйкес келетіндей болып дербес түрде тағайындалады. Егер шифратордың кірістік тізбектерінің саны тым көп болса, олармен түзілетін алмасулардың бәрін пайдалануға мүмкіндік бола бермейді. Ондай жағдайда шифратор толық емес деп есептеледі. Керісінше, пернелердің саны кірістік тізбектердің санына тең болса, шифратор толық деп есептеледі.

Мысалы,

төрт разрядты санды өндіру үшін

шифратордың 10 кірісін пайдалану

жеткілікті, ал сол шифратор

![]() кірістік тізбектермен жұмыс істеуге

қабілетті. Ендеше, 10х4 шифратор толық

еместер қатарына жатқызылады.

кірістік тізбектермен жұмыс істеуге

қабілетті. Ендеше, 10х4 шифратор толық

еместер қатарына жатқызылады.

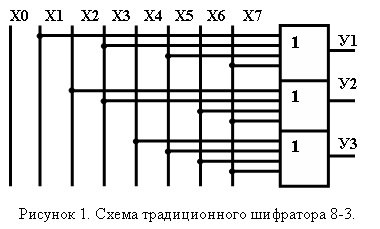

Мысал ретінде 8 разрядты бірлік кодты екілік кодқа түрлендіруге арналған 8х3 (К=23=8) шифраторының құрылуын қарастырайық. Әр жолы логикалық 1-ге сәйкес келетін сигнал шифратордың тек бір кірісіне ғана берілетін болсын. Осындай шифратордың жұмыс істеу логикасы 1-кестеде келтірілген ақиқат кестесі арқылы суреттеледі.

Осы ақиқат кестесіне сүйене отырып, шифратордың жұмысын сипаттайтын логикалық теңдеулерді жазуға болады. Теңдеулер логикалық қосынды түрінде бейнеленеді. Теңдеудегі айнымалы шама ретінде шифратордың әрбір шығысындағы бірлік мәнге сәйкес келетін ондық санның реттік нөмірі қабылданады, яғни шифратордың әрбір шығысы үшін жазылатын логикалық функциялар төмендегідей өрнектеледі:

![]()

![]()

![]()

1-кесте. Шифратордың ақиқат кестесі

|

Ондық Х |

Екілік код | ||

|

У3 |

У2 |

У1 | |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

Осы шарттарды қанағаттандыратын шифратордың схемасын НЕМЕСЕ логикалық элементтерімен құруға болады. Бұл схеманың кемшілігі екі пернені қатар басқан кезде пайда болатын қателіктерден құтқара алмайтындығында. Сондықтан іс жүзінде жетекші (приоритеті бар) шифратор жиі қолданылады. Бұл шифратордың шығыстық тізбектеріндегі екілік санның коды қатар басылған бірнеше пернелердің тек мәні үлкеніне ғана сәйкес туындайды.

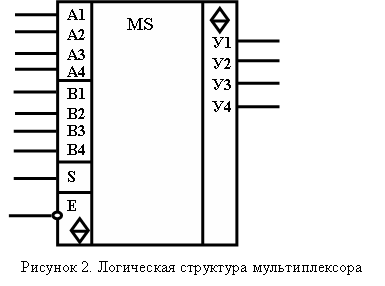

Осы жұмыстың екінші бөлімінде мультиплексор деп аталатын селекторлық схема талданады. Мультиплексор дегеніміз кірістік тізбектердің біреуіндегі мағлұматты адресі көрсетілген шығыстық тізбекке тасымалдаушы комутатор. Сондай мультиплексорға К155КП11 микросхемасымен құрылған электрондық комутаторды жатқызуға болады.

1-сурет. Дәстүрлі 8-3 шифраторының құрылуы.

Осындай мультиплексордың логикалық құрылымы 2-суретте келтірілген. Бұл мультиплексордың екі түрлі 4 разрядты кірістік тізбектері бар ( Ai және Bi). Осы тізбектердің біреуіндегі мағлұматты мультиплексор параллель кодпен сыртқы тізбектерге (у1, у2, у3, у4) тасымалдайды.

![]() 2-сурет.

Мультиплексордың логикалық құрылымы.

2-сурет.

Мультиплексордың логикалық құрылымы.

Бұл

микросхеманың кірістік тізбектері

логикалық «0», логикалық «1» және шығысы

мен кірісінің арасындағы жоғарғы мәнді

кедергіге ие болатын үш түрлі күйде

бола алады. Соңғы жағдайда оның шығыстық

тізбектері (Уi)

кірістік тізбектерінен (Ai

немесе

Bi)

мүлдем ажыратылады. Бұл процесс

мультиплексордың Е

кірісіне логикалық «1» шамасы берілген

кезде орындалады, яғни Е=1 болған

кезде коммутациялауға тиым салынады.

Егер Е=0 болса,

мультиплексордың S-

кірісінің күйіне байланысты (0 немесе

1) оның шығысындағы

шамалар Уi

сәйкес

![]() тізбектерінен, немесе

тізбектерінен, немесе![]() тізбектерінен тасымалданады.

тізбектерінен тасымалданады.