- •Features

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •Port E (PE7..PE0)

- •Port F (PF7..PF0)

- •Port G (PG4..PG0)

- •RESET

- •XTAL1

- •XTAL2

- •AVCC

- •AREF

- •Resources

- •Data Retention

- •Capacitive touch sensing

- •AVR CPU Core

- •Introduction

- •Status Register

- •Stack Pointer

- •I/O Memory

- •Overview

- •Timing

- •Using all Locations of External Memory Smaller than 64 Kbyte

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Crystal Oscillator

- •External Clock

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 0

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Register Description for I/O Ports

- •8-bit Timer/Counter0 with PWM and Asynchronous Operation

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Normal Mode

- •Fast PWM Mode

- •8-bit Timer/Counter Register Description

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Noise Canceler

- •Force Output Compare

- •Normal Mode

- •Fast PWM Mode

- •16-bit Timer/Counter Register Description

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •8-bit Timer/Counter2 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Normal Mode

- •Fast PWM Mode

- •8-bit Timer/Counter Register Description

- •Output Compare Modulator (OCM1C2)

- •Overview

- •Description

- •Timing Example

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Dual USART

- •Overview

- •AVR USART vs. AVR UART – Compatibility

- •Clock Generation

- •External Clock

- •Frame Formats

- •Parity Bit Calculation

- •Parity Generator

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Using MPCM

- •Features

- •TWI Terminology

- •Transferring Bits

- •Address Packet Format

- •Data Packet Format

- •Overview of the TWI Module

- •Scl and SDA Pins

- •Bus Interface Unit

- •Address Match Unit

- •Control Unit

- •Using the TWI

- •Master Receiver Mode

- •Slave Receiver Mode

- •Miscellaneous States

- •Analog Comparator

- •Analog to Digital Converter

- •Features

- •Operation

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •Analog Input Circuitry

- •Features

- •Overview

- •TAP Controller

- •PRIVATE0; $8

- •PRIVATE1; $9

- •PRIVATE2; $A

- •PRIVATE3; $B

- •Bibliography

- •Features

- •System Overview

- •Data Registers

- •Bypass Register

- •Reset Register

- •EXTEST; $0

- •IDCODE; $1

- •AVR_RESET; $C

- •BYPASS; $F

- •Scanning the ADC

- •ATmega128 Boundary-scan Order

- •Application Section

- •Programming Time for Flash when Using SPM

- •Simple Assembly Code Example for a Boot Loader

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Chip Erase

- •Reading the Flash

- •Reading the EEPROM

- •Data Polling Flash

- •Data Polling EEPROM

- •AVR_RESET ($C)

- •PROG_ENABLE ($4)

- •Data Registers

- •Reset Register

- •Programming Enable Register

- •Programming Command Register

- •Virtual Flash Page Read Register

- •Performing Chip Erase

- •Reading the Flash

- •Reading the EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •Speed Grades

- •External Clock Drive Waveforms

- •External Clock Drive

- •Two-wire Serial Interface Characteristics

- •ADC Characteristics

- •External Data Memory Timing

- •Idle Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Errata

- •ATmega128 Rev. F to M

ATmega128

ATmega128

System Clock

and Clock

Options

Clock Systems and their Distribution

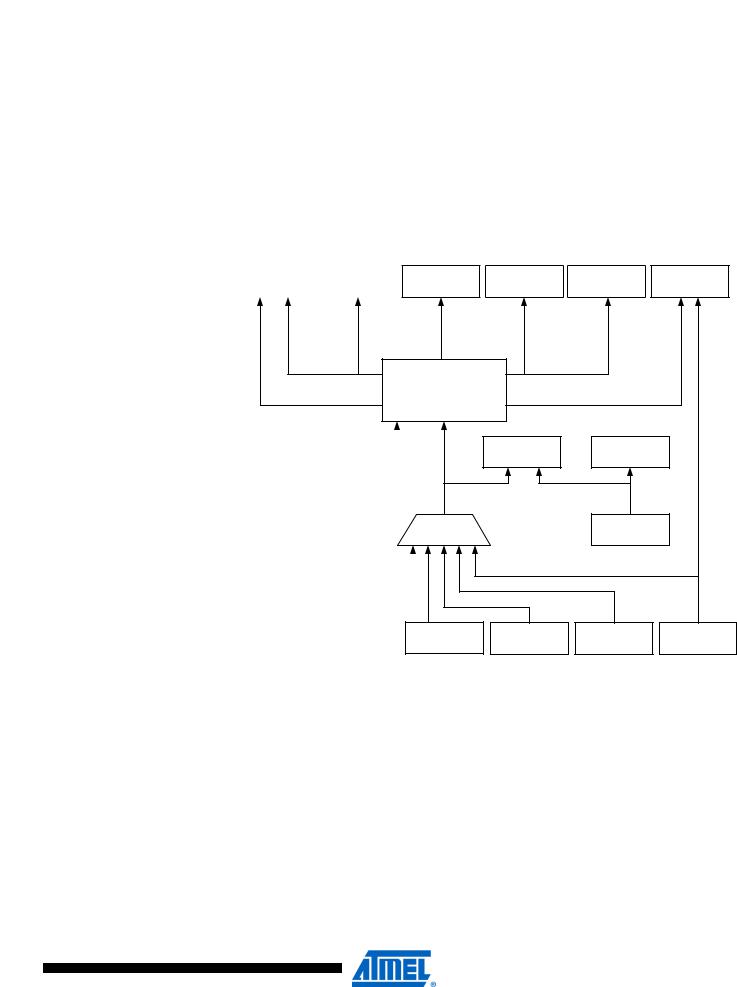

Figure 18 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes, as described in “Power Management and Sleep Modes” on page 44. The clock systems are detailed below.

Figure 18. Clock Distribution

Asynchronous |

|

General I/O |

Timer/Counter |

|

modules |

|

|

|

clkI/O

clkASY

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer/Counter |

|

External RC |

|

||

Oscillator |

|

Oscillator |

|

||

|

|

|

|

|

|

ADC |

CPU Core |

RAM |

Flash and |

|

EEPROM |

||||

|

|

|

||

clkADC |

|

|

|

|

AVR Clock |

clkCPU |

|

|

|

Control Unit |

|

|

|

|

|

clkFLASH |

|

|

|

|

Reset Logic |

Watchdog Timer |

|

|

Source clock |

Watchdog clock |

|

||

Clock |

|

Watchdog |

|

|

Multiplexer |

|

Oscillator |

|

|

|

Crystal |

Low-Frequency |

Calibrated RC |

|

External clock |

Oscillator |

Crystal Oscillator |

Oscillator |

|

CPU Clock – clkCPU |

The CPU clock is routed to parts of the system concerned with operation of the AVR core. |

|

Examples of such modules are the General Purpose Register File, the Status Register and the |

|

data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing |

|

general operations and calculations. |

I/O Clock – clkI/O |

The I/O clock is used by the majority of the I/O modules, like Timer/Counters, SPI, and USART. |

|

The I/O clock is also used by the External Interrupt module, but note that some external inter- |

|

rupts are detected by asynchronous logic, allowing such interrupts to be detected even if the I/O |

|

clock is halted. Also note that address recognition in the TWI module is carried out asynchro- |

|

nously when clkI/O is halted, enabling TWI address reception in all sleep modes. |

Flash Clock – clkFLASH |

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simul- |

|

taneously with the CPU clock. |

35

2467X–AVR–06/11