- •Федеральное агентство по образованию и науке Российской Федерации

- •Лабораторная работа №1 Изучение технологии изготовления и основных параметров резисторов Цель работы:

- •Теоретические сведения.

- •Общие сведения о резисторах постоянного сопротивления Основные параметры резисторов постоянного сопротивления

- •Непроволочные резисторы

- •Проволочные резисторы

- •Основные сведения о технологиях изготовления постоянных резисторов

- •Резисторы переменного сопротивления

- •Основные параметры резисторов

- •Переменные регулировочные резисторы

- •Переменные подстроечные резисторы

- •Основные сведения о технологии изготовления переменных композиционных резисторов

- •Специальные резисторы Полупроводниковые терморезисторы

- •Основные параметры и характеристики

- •Технология изготовления терморезисторов

- •Полупроводниковые варисторы

- •Основные параметры и характеристики

- •Технология изготовления варисторов

- •Полупроводниковые фоторезисторы

- •Основные параметры фоторезисторов

- •Технология изготовления фоторезисторов

- •Домашнее задание

- •Лабораторное задание

- •Измерительные приборы, оснастка, образцы

- •Порядок выполнения работы

- •Требования к отчету

- •Контрольные вопросы

- •Литература

- •Приложение 1 Цветовая маркировка миниатюрных резисторов постоянного сопротивления

- •Маркировка буквенно-цифровая

- •Маркировка переменных резисторов

- •Система обозначений

- •Маркировка специальных резисторов Маркировка термисторов

- •Система обозначений термисторов

- •Система обозначений варисторов

- •Лабораторная работа № 2 Изучение конструкции и технологии изготовления дискретных конденсаторов и оценка их электрических параметров.

- •Теоретические сведения

- •Классификация конденсаторов

- •Конденсаторы с органическим диэлектриком

- •Конденсаторы с неорганическим диэлектриком

- •Конденсаторы с оксидным диэлектриком

- •Конденсаторы с газообразным диэлектриком

- •Конструкции конденсаторов

- •Система условных обозначений и маркировка конденсаторов

- •Технология изготовления керамических конденсаторов Получение керамического шликера

- •Технология приготовления шликера

- •Технология литья пленки

- •Керамические материалы

- •Технология изготовления танталовых чип-конденсаторов

- •Домашнее задание

- •Лабораторное задание

- •100.(Сизм – Сном )/Сном.

- •Технологическое оборудование, оснастка, измерительные приборы и материалы

- •Порядок выполнения работы

- •Контрольные вопросы

- •Литература

- •Основные параметры ки

- •Конструкции и технологии изготовления ки

- •Классификация магнитных материалов. Ферриты

- •Порядок расчета

- •Пример расчета

- •Домашнее задание

- •Лабораторное задание

- •Технологическое оборудование, оснастка, измерительные приборы и материалы

- •Порядок выполнения работы

- •Требования к отчету

- •Контрольные вопросы

- •Литература

- •Соединители и прочие коммутационные устройства

- •Электрические соединители. Классификация электрических соединений по их применению включает:

- •Токосъем – или

- •Соединение –

- •Основные параметры соединителей

- •У электростатического реле (рис 6,г) принцип действия основан на использовании кулоновских сил, которые обеспечивают притяжение подвижного электрода с мембраной к неподвижному.

- •Электронные реле (рис.6,д) представляют собой обычный электронный ключ, например на транзисторах (на биполярных, либо на кмоп или моп структурах и др.) (рис.7).

- •Резисторы, конденсаторы, катушки индуктивности и прочие дискретные пассивные и активные эрк.

- •Резисторы, конденсаторы, катушки индуктивности и прочие дискретные пассивные и активные эрк.

- •Общие сведения о корпусах дискретных полупроводниковых приборов

- •Общие сведения об устройствах индикации

- •Корпуса интегральных схем

- •Понятие о фильтрах и линиях задержки

- •Общие представления о резонаторах

- •Понятие о криоэлектронных приборах

- •Домашнее задание

- •Лабораторное задание

- •Инструменты приспособления и макетные образцы

- •Порядок выполнения работы

- •Результаты изучения компонентов в составе ячейки эвс

- •Требования к отчету

- •Контрольные вопросы

- •Литература

- •Лабораторная работа №5 Изучение технологии изготовления жидкокристаллических индикаторов

- •Теоретические сведения

- •Общие сведения о жидких кристаллах и их свойствах

- •Принцип работы жки

- •Особенности конструкции жки и технология её изготовления

- •Сравнительные характеристики разных типов индикаторов

- •Домашнее задание

- •Лабораторное задание

- •Макетные образцы

- •Порядок выполнения работы.

- •Требования к отчёту

- •Контрольные вопросы

- •Литература

- •Приложение 1 Индикаторы на светоизлучающих диодах

- •Физические основы работы сид

- •Приложение 2 Индикаторы на электронно-лучевых трубках

- •Газоразрядные индикаторы

- •Вакуумные люминесцентные индикаторы

- •Приложение 5 Электролюминесцентные индикаторы

- •Накальные индикаторы

- •Электрохромные индикаторы

- •Электрофорезные индикаторы

- •Приложение 9 Электромеханические индикаторы

- •Лабораторная работа № 6

- •Линии передачи

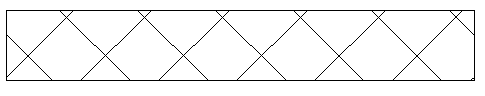

- •Подложки и проводники мпл

- •Элементы, узлы и устройства

- •Фильтры

- •Генератор свч колебаний на лавинно-пролетном диоде (глпд)

- •Малошумящий усилитель (мшу)

- •Технология свч гис

- •Технология изготовления свч гис и мсб

- •Технологический маршрут изготовления свч гис и мсб

- •Аппаратура

- •Лабораторное задание

- •Контрольные вопросы

- •Литература

- •Технологические среды и материалы для изготовления кристаллодержателя на гибком носителе (гн).

- •Анализ способов и методов сборки и монтажа кристаллодержателя на гн и выбор наиболее целесообразного.

- •Последовательность в изготовлении кристаллодержателя на гибком носителе.

- •Структура полиимидных носителей.

- •Конструкционные материалы.

- •Конструкции ленточных носителей

- •Полиимидный носитель с алюминиевыми выводами

- •Домашнее задание.

- •Контрольные вопросы

- •Литература

- •Приготовление керамического шликера Состав керамического шликера

- •Минеральная составляющая

- •Растворители

- •Пластификаторы

- •Поверхностно-активное вещество (пав)

- •Этапы технологии приготовления шликер

- •Технология литья пленки

- •Изготовление заготовок слоев

- •Металлизация слоев

- •Изготовление основания кристаллодержателя

- •Герметизация корпусов

- •Материалы для производства керамических кристаллодержателей

- •Пасты для изготовления керамических кристаллодержателей

- •Требования к проводниковым пастам

- •Определение реологических требований к пасте

- •Реологические свойства пасты

- •Вязкость

- •Поверхностное натяжение

- •Исследования методов нанесения паст

- •Домашнее задание

- •Лабораторное задание

- •Материалы для выполнения лабораторной работы.

- •Порядок выполнения работы

- •Требования к отчету.

- •Контрольные вопросы.

- •Литература

- •Содержание

Технологический маршрут изготовления свч гис и мсб

Нанесение технологического защитного покрытия на поверхность подложки с обеих сторон. Применяется при механической обработке подложек, сверлении отверстий и др.

Сверление отверстий в подложках на скоростном сверлильном станке алмазным инструментом, либо прошивка отверстий лазерным лучом или ультразвуком.

Удаление технологического защитного покрытия.

Очистка подложек. Сначала производится очистка от полировочных паст на ультразвуковой установке, затем плазмохимическая обработка, после чего следует сушка в потоке нейтрального газа.

Формирование резисторов, тонкопленочных проводников и контактных площадок вакуумным напылением с применением масочного метода или фотолитографии. Масочный метод: напыление резистивного слоя через маску; напыление электропроводящих слоев для получения площадок через маску. Фотолитография (ФЛ): метод получения рисунка в напыленных слоях (по всей поверхности подложки). Последовательность выполнения ФЛ может быть разной. Если есть в схеме резисторы, то все слои могут напыляться в одном технологическом цикле, после чего проводят ФЛ последовательно в каждом слое (начиная с верхнего слоя), в этом случае речь идет о двойной ФЛ. Иногда напыляют резистивный слой и проводят ФЛ в этом слое, а затем напыляют проводники и контактные площадки, после чего следует ФЛ в проводящем слое. В последнем случае точность изготовления элементов хуже, но электрические характеристики могут быть лучшими по сравнению с двойной ФЛ.

Доводка номиналов сопротивлений резисторов отжигом.

Электролитическое доращивание основного электропроводящего слоя до требуемой толщины (обычно до 20 мкм).

Химическое или электрохимическое осаждение антикоррозийного покрытия проводящих элементов (Au, Ag, Sn – Pb, либо Sn - Vi).

При необходимости напыляют с обратной стороны (см. п8) подложки электропроводящие слои (Cr-Сu) с последующим гальваническим доращиванием защитного покрытия.

Скрайбирование.

Монтаж навесных компонентов.

Сборка, монтаж и герметизация ГИС.

1 .

.

2

.

.

3 .

.

4 .

.

5 .

.

6 7.

8

.

.

9.

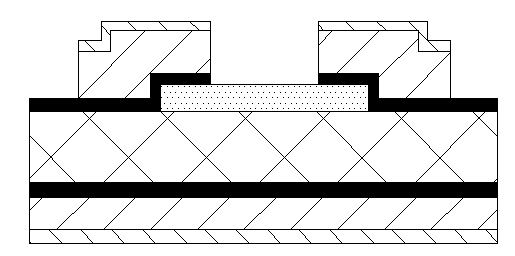

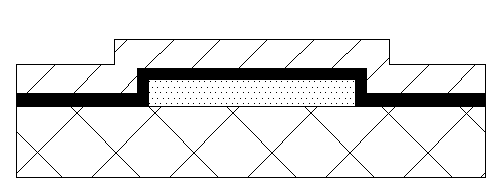

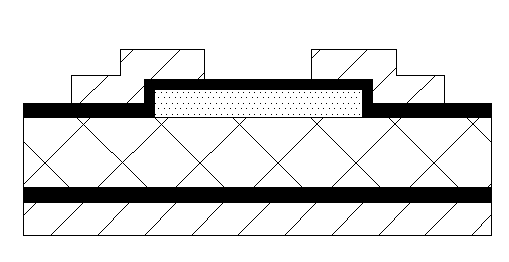

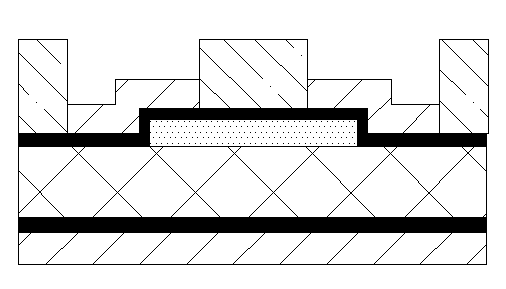

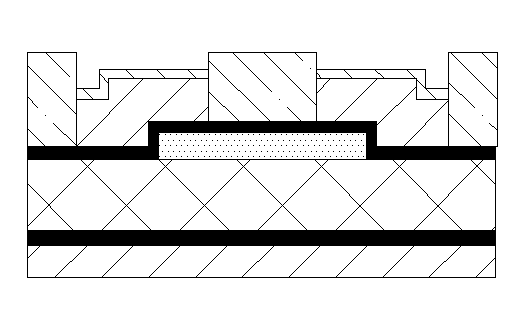

Рис. 29. Схема основных этапов технологического процесса изготовления одного из вариантов микрополосковой платы СВЧ-модуля;

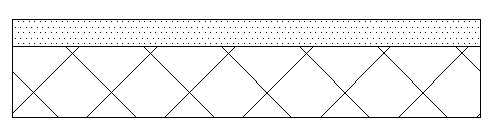

1 – очистка поликора;

2 – напыление резистивного слоя; 3 – ФЛ в резистивном слое;

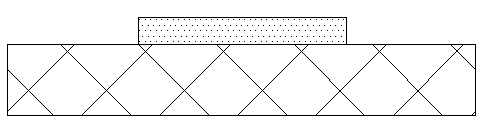

4 – напыление проводящего слоя Cr-Cu;

5 – ФЛ (в слое Cu);

6 – напыление структур Cr-Cu с обратной стороны подложки;

7 – ФЛ в слое фоторезиста перед гальваническим доращиванием Cu и осаждением Au;

8 – гальваническое доращивание Cu и осаждение Au;

9 – удаление ФР и стравливание технологического поля из Cr.

Аппаратура

В лабораторной работе используется макет, состоящий из кассеты СВЧ ГИС различного назначения и пластины с образцами плат после различных операций изготовления СВЧ ГИС, микроскоп ММУ-3 и лупа.

Лабораторное задание

Изучить образцы макета.

Определить, после какой операции взяты эти образцы.

Заполнить форму табл.1

Форма табл. 1

Технологический процесс изготовления СВЧ ГИС

№ пластины в кассете

Наименование операции

Назначение операции в технологическом маршруте

Характерные признаки операции

Материалы формируемого слоя

Примечания

1

.

n

Изобразить топологию реактивных СВЧ – элементов данного изделия.