- •Лекция 1 введение

- •Лекция 2 Дискретные системы управления и их преимущества

- •2.1 Структура дискретной системы управления.

- •2.2 Выбор аппаратной части цф

- •2.3 Выбор языка программирования цф

- •2.4 Методы перехода к дискретной передаточной функции.

- •Лекция 3 использование z и w - преобразования

- •Лекция 4 способы программирования дискретной передаточной функции

- •4.1 Параллельное и последовательное программирование

- •4.2 Непосредственное программирование

- •4.3 Реализация цф в виде подпрограмм

- •Лекция 5 анализ и синтез дискретных су

- •5.1 Обеспечение заданной точности

- •5.2. Обеспечение заданного запаса устойчивости

- •Цифровые системы с экстраполятором первого порядка

- •Лекция 6 Расчет корректирующих средств

- •6.1. Расчет непрерывных корректирующих средств

- •Можно принять

- •6.2. Расчет дискретных корректирующих средств

- •Дискретная частотная передаточная функция

- •Переход к передаточной функции цвм дает

- •Типовые последовательные дискретные корректирующие звенья

- •Лекция 7 разработка микропроцессорных средств (мпс) дискретных су

- •7.1 Регистровая алу. Базовая структура ралу.

- •7.2 Регистровая алу разрядно-модульного типа

- •7.3 Наращивание разрядности обрабатываемых слов

- •7.4 Однокристальные ралу

- •Лекция 8 устройства микропрограммного управления микропроцессорных су

- •8.1 Устройства управления на жёсткой логике

- •Блок (узел) микропрограммного управления (бму).

- •8.2 Эмуляция системы команд (архитектуры) микро эвм посредством программирования

- •Лекция 9 модули памяти микропроцессорных су

- •9.1 Особенности и принцип построения озу

- •Статические озу

- •Динамические озу

- •9.2 Особенности и принципы построения пзу и ппзу

- •9.3 Организация и применение стековой памяти

- •Лекция 10 модули памяти микропроцессорных су(продолжение)

- •10.1. Классификация зу микро-эвм

- •10.2. Функциональные схемы озу, пзу, ппзу

- •10.2.1. Функциональные схемы озу

- •10.3. Организация многокристальной памяти

- •Лекция 11 основы реализации многопроцессорных систем

- •Лекция 12 основы реализации многопроцессорных систем (Продолжение)

- •Лекция 13 особенности разработки аппаратных средств

- •Разработка аппаратных средств мпу

- •Особенности и принципы построения разрядно - модульных микропроцессоров

- •Лекция 14 аналого-цифровые преобразователи

- •14.1 Обеспечение совместимости объекта измерения с процессором по форме представления информации

- •14.1.1 Основные операции аналого-цифрового преобразования

- •14.1.2 Алгоритмы аналого-цифрового преобразования и структуры

- •14.2 Оптимизация выбора бис ацп и бис цап микропроцессорных средств.

- •Лекция 15 датчики

- •15.1. Первичные преобразователи (датчики)

- •15..2. Свойства и разновидности измерительных преобразователей

- •15.3. Измерительные цепи

- •15.4. Контактные резистивные преобразователи

- •Лекция 16 датчики (Продолжение)

- •16.1. Реостатные и потенциометрические преобразователи

- •16.2. Электромагнитные первичные преобразователи

- •Лекция 17 датчики и исполнительные приводы

- •17.1. Ёмкостные первичные преобразователи

- •17.1.2. Пьезоэлектрические преобразователи

- •17.1.3. Тензометрические преобразователи

- •17.1.4. Оптические преобразователи

- •17.1.5. Тепловые преобразователи

- •17.1.6. Терморезисторы

- •117.2 Исполнительные приводы

- •Лекция 18 Промышленные контролеры

- •Лекция 19 Промышленные контролеры (Продолжение)

- •19.1 Локальные промышленные сети

- •19.2 Общие принципы построения промышленных контроллеров

- •19.3 Особенности распределенной системы управления

- •Лекция 20 типовые структуры су с эвм

- •2. Для автоматических систем характерна замена человека в контуре

- •Лекция 21 Дискретные системы управления на основе малых локальных сетей

- •Лекция 22 дискретные системы управления с параллельной обработкой данных

- •Лекция 23 многопроцессорные дискретные системы управления с общей памятью

- •Лекция 24 перспективы развития и внедрения дискретных су

- •Лекция 25 модели связи и архитектуры памяти

Блок (узел) микропрограммного управления (бму).

БМУ - узел микропроцессора, предназначенный для выработки последовательности адресов микрокоманд, считываемых из управляющей памяти для выполнения микро команды или управляющей директивы.

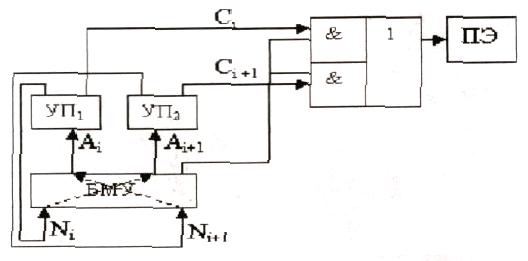

Рисунок 8.6 - БМУ

БМУ состоит из:

1. Рг адреса микро команды, в котором хранится адрес текущей микро команды в течение времени, необходимого для выполнения данной микро команды в процессорном элементе и формирования адреса следующей микро команды.

2. выходные буферы обеспечивающие электрическое сопряжение с управляющей памятью, а также благодаря наличию режима третьего состояния позволяет обеспечить подключение к одной и той же управляющей памяти нескольких блоков ЕМУ.

3. логические схемы определения адреса следующей микро команды. Данная схема формирует адрес следующей микро команды в зависимости от адреса текущей микро команды состояния зоны следящего адреса текущей микрокоманды состояния, триггера внешних условий.

В начальный момент времени по сигналу ЗМ заносится в регистр адреса код операции К0 - К7, который, как правило, является начальным адресом микро программы, необходимой макро команде ЗУ (управляющей памяти) обычно представляется как 1-, 2 -, массив микро команд.

Разработка ЕМУ (логическая схема определения адреса следующей микро команды) базируется на формировании определённого числа переходов в пределах массива адресов памяти.

На основании содержательного анализа избранных типов переходов формируется таблица, отражающая правила формирования адреса строки и колонки. По данной таблице строится схема формирования адреса следующей микро команды.

Логическая схема, определения адреса следующей микро команды строится на основании MS-b, программируемых логических схемах, ПЗУ.

Области применения: устройства управления программами, построение быстродействующих контроллеров.

Построение быстродействующих контролеров на основе БМУ и ПЗУ Типовым процессом проектирования является:

1. анализ объекта управления.

а) изучение состава датчиков входной информации.

б) изучение состава исполнительных элементов.

в) изучение состава или разработка алгоритма работы объекта управления.

г) изучение состава динамических характеристик объекта управления, датчика входной информации и исполнительных элементов.

д) изучение состава динамической и статической точности системы управления.

е) анализ конструктивных требований.

2. оценка возможностей исполнения типового варианта контроллера.

3. формирование

взаимосвязей «объект управления»

![]() «контроллер».

«контроллер».

4. разработка программ работы контроллера.

Рисунок 8.7 - Типовая структура контроллера

8.2 Эмуляция системы команд (архитектуры) микро эвм посредством программирования

Эмуляция системы команд, принадлежащей ЭВМ означает, что ее машинный язык будет адекватно связан с другой машиной на уровне микропрограммирования, при этом на данной вычислительной машине может быть использован весь программный запас, разработанный на предыдущей вычислительной машине, требуется значительного уменьшения времени на создание программного обеспечения, в одной вычислительной машине можно реализовать несколько систем команд.

Рисунок 8.8 - Эмуляция системы команд

Существует 3 способа эмуляции системы команд:

1. использование КОП команды непосредственно в качестве начала микропрограммы.

Достоинства: простота реализации. Недостатки: отсутствие необходимой корреляции между кодами операций и рациональным разбиением управляющей памяти.

2. использование косвенной адресации. Достоинства: более рациональное использование памяти. Недостатки: снижение быстродействия.

3. помещение таблицы: переходов в дополнительное ПЗУ. Достоинства: максимальное быстродействие. Недостатки: лишние аппаратные затраты.

Структурные методы повышения быстродействия микроЭВМ.

Рисунок 8.9 - Временные диаграммы взаимодействия основных узлов

микроЭВМ

Ni - ссылка на адрес следующей микро команды

Сi - разряд, управляющий работой ПЭ

Si - информация о состоянии ПЭ

Аi - адрес текущей микро команды

tA - время установки RG адреса в БМУ

tNC - время реакции УП на адрес поступающий из БМУ

tS- время с момента выработки сигнала Q до окончания выполнения операции в ПЭ

tm - время установки RG хранения результата операции.

Конвейерная обработка информации

Рисунок 8.10 - Конвейерная обработка информации

В системе с конвейерной обработкой информации имеют место 2 параллельных процесса:

1. формирование адреса следующей микро команды.

2. выполнение операций в процессорном элементе.

При этом задержки tS и tNC совмещаются, а задержки установки RG tA и конв. RG примерно одинаково. При этом быстродействие увеличивается в 1.5-1.8 раза.

Достоинства: увеличение быстродействия при минимальных аппаратных затратах. Недостатки: наличие фазового сдвига в тех участках вычислительного процесса, в которых проводится анализ состояния процессорного элемента.

Для устранения данного недостатка используются "длинные" команды, которые занимают 2 такта.

Многоуровневая конвейерная обработка

Рисунок 8.11 - Многоуровневая конвейерная обработка

В данном случае имеет место процессор с повышенным быстродействием и управляющим памятью с относительно низким быстродействием. Устанавливается конвейер из такого количества RG, во сколько раз процессор по своему быстродействию выше, чем быстродействие управляющей памяти.

Достоинства: максимальное быстродействие при минимальных аппаратных затратах. Недостатки: наличие фазового сдвига в тех участках вычислительного процесса, в которых оценивается состояние ПЭ, для исключения недостатка во все RG записывается одна и та же микро команда, или работа всего устройства идет через регистр Рri.

Память с расслоением.

В этом случае выбирается столько слоев в памяти во сколько раз быстродействие ПЭ больше быстродействия управляющей памяти.

Достоинства и недостатки те же. Недостатки устраняются путем записи одной и той же команды в 2-х ячейках памяти.

Рисунок 8.12 - Схема памяти с расслоением

Вычислительные системы с переменной длительностью цикла

1 - это логические операции.

2 - арифметические операции без формирования признаков состояния.

3 - арифметические команды с анализом, и формированием признаков.

В структуру микро команды добавляется 2 разряда (или более), которые несут информацию о том, какие операции выполняются в данный момент. Данные операции управляются ГТИ, обеспечивающего формирование соответствующей временной диаграммы.