- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

6.10. Jtag

www.jtag.ru

Под JTAG, подразумевается стандарт: IEEE 1149.1-2001 Test Access Port and Boundary-Scan Architecture (Стандарт IEEE 1149.1-2001 Порт тестового доступа и Архитектура Граничного сканирования).

С ростом степени интеграции БИС, плотности монтажа и появлением многослойных печатных плат, методы диагностики, основанные на подключении к контрольным точкам платы и выводам микросхем, становятся все более сложными в использовании и неэффективными.

Основные недостатки альтернативных способов диагностики были связаны, прежде всего, с отсутствием соответствующих общепринятых стандартов—и, как следствие, широкой поддержки проектировщиков и производителей.

В начале 1985 года объединенными усилиями нескольких европейских компаний была создана группа для разработки решения проблем тестирования интегральных схем, цифровых устройств и систем. Эта группа получила имя: Joint European Test Action Group (JETAG). Позднее, в 1988 году к ней присоединились представители североамериканских компаний, и название было изменено на Joint Test Action Group (JTAG).

Результатом работы этой группы явился принятый в 1990 году стандарт IEEE Std.1149.1 и его усовершенствованная версия: стандарт IEEE Std.1149.1a (1993 год).

В основу стандарта положена идея внедрение в компоненты цифрового устройства средств, обеспечивающих унифицированный подход к решению следующих задач:

- Тестирование связей между интегральными схемами, после того, как они были смонтированы на печатной плате или другой основе;

- Наблюдение за работой компонент без вмешательства в их нормальную работу, или непосредственное управление одним или более компонентом;

- Обеспечение стандартизованного доступа к произвольным средствам самотестирования, встраиваемым в БИС;

Cтандарт JTAG определяет:

Интерфейс, через который осуществляется обмен тестовыми инструкциями и данными между ведущим устройством и встроенными средствами тестирования (TAP — Test Access Port) ;

Минимальный набор средств тестирования, встраиваемых в БИС (средства поддержки метода Граничного Сканирования);

Рассмотрим порт тестового доступа: TAP (Test Access Port).

Когда мы говорим о передаче информации через JTAG, то мы подразумеваем обмен между ведущим устройством и встроенными в БИС средствами тестирования. Для этой цели был разработан TAP (Test Access Port)—Порт Тестового Доступа.

Аппаратная поддержка поддержки JTAG реализуется достаточно простыми схемами. TAP требует 4-х внешних контактов:

TDI (Test Data Input)—контакт для получения последовательных данных. На этот контакт последовательно, бит-за-битом податься данные, которые затем интерпретируются схемой управления;

TDO (Test Data Output)—контакт вывода последовательных данных. С этого контакта ведущее устройство последовательно считывает данные из БИС (например результат тестовых операций);

TCK (Test Clock Input)—контакт сигнала синхронизации обмена;

TMS (Test Mode Select)—этот контакт управляет состоянием внутреннего автомата TAP. В частности с помощью этого контакта определяется что грузиться: команда или данные, а также определяться начало и конец загрузки;

Следующий контакт не является обязательным для реализации:

TRST (Test ReSeT)—сброс в начальное состояние контроллера внутреннего автомата TAP

Рассмотрим подробнее структуру БИС, построенными в соответствии с требованиями JTAG.

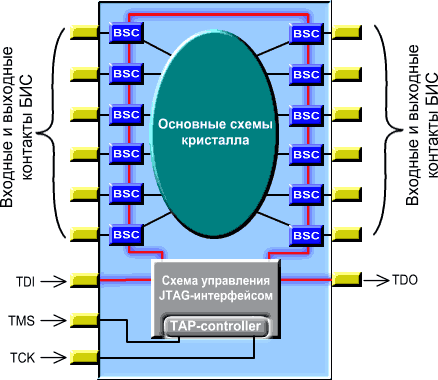

Рис. 5. Архитектура БИС поддерживающая метод граничного сканирования.

Основу архитектурной поддержки метода состоявляют ячейки граничного сканирования (BSC—Boundary Scan Cell). Последовательность из этих ячеек разделяет внутреннюю логику БИС и ее внешние выводы. С точки зрения обмена эта последоваетельность представляет собой один регистр данных, который включаться в канал JTAG. Такой регистр называеться Регистром Граничного Сканирования (Boundary Scan Register). Ниже приведен наиболее простой вариант схемы отдельной ячейки:

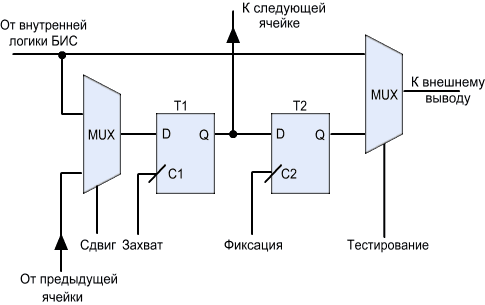

Рис. 6. Схема сканирующей ячейки

Можно выделить несколько режимов в работе ячейки Ж

Режим сдвига, когда в триггера Т1 по сигналу "захват" сохраняется состояние аналогичного триггера предыдущей ячейки. В этом режиме ведущее устройство последовательно выдвигает текущее состояние ячеек и вдвигает новое;

Режим наблюдения ("Sample") В этом режиме по импульсу текущее состояние вывода фиксируется в триггере, и может быть потом считано ведущим устройством. При этом, в процессе обмена данные получаемая от ведущего устройства фиксируются в триггере. При необходимости, в режиме тестирования (EXTEST) эти данные могут быть выведены на внешний вывод;

Режим тестирования ( EXTEST—Executing Test ). В этом режиме на выход подается логическое значение, которое находиться в триггере Т2;

В приведенной схеме на каждый вывод БИС приходиться один бит регистра граничного сканирования (его роль играет триггер Т1). Однако очень часто встречаються схемы, в которых на каждый вывод приходиться 3 бита: бит для вывода значения в тестовом режиме, бит, сохраняющий фактический логический уровень, находящийся на выводе, и бит управляющий переводом вывода в высоко-импедансное состояние.

Рассмотрим Возможности Граничного Сканирования

Таким образом ведущее устройство может получить доступ к любому выводу любой БИС, включенной в JTAG-цепочку.

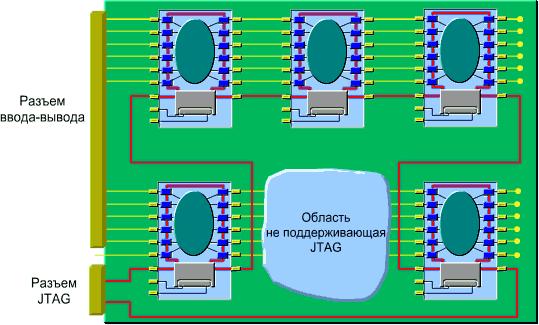

Рис. 7. Плата с поддержкой JTAG.

Выставляя на одних выводах логические уровни и проверяя состояния других ведущее устройство может делать заключение о наличии или отсутствии связей между выводами различных БИС;

Перехватывая управление выводами можно формировать на выводах областей не охваченных цепочкой тестовые комбинации и проверять корректность реакций. Например, управляя выводами центрального процессора произвести тестирование работоспособности ОЗУ; Делать "снимки" состояний контактов интегральных схем цифрового устройства, и на основе их анализа делать заключение о правильности его работы;