- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

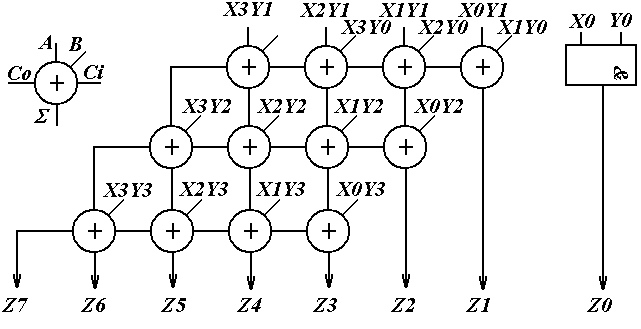

2.9.3.2 Матричный умножитель

Рассмотрим структуру матричного умножителя умножающего два четырехразрядных двоичных числа.

Рисунок 2.43 - Матричный умножитель четырехразрядных двоичных чисел

Как и для предыдущего умножителя X1Y0 означает логическое И между X1 и Y0. Как видно из рисунка в состав умножителя входят 16 элементов И, 9 полных сумматоров и 3 полусумматора. Информация на выходах Z появится непосредственно при подаче на входы 1 и 2 множителя. Помимо схемы на рисунке 2.43 на практике применяются схемы древовидных матричных умножителей и умножителей с ускоренным переносом (Рабинер, Гоулд, Теория и применение цифровой обработки сигналов)

3 Программируемые логические интегральные схемы (плис)

Современный этап развития ЭВТ характеризуется двумя противоречивыми тенденциями:

С одной стороны увеличивается сложность и ужесточаются требования, предъявляемые к быстродействию, надежности, энергопотреблению и стоимости специализированных микросхем

С другой стороны жизненный цикл изделий МПТ существенно сократился.

Целью разработки любого микроэлектронного устройства является создание специализированной схемы, которая может быть построена на основе микросхем массового применения и на основе программируемых логических интегральных схем.

Любая специализированная СБИС может быть изготовлена различными способами.

Рисунок 2.44 - Классификация способов изготовления специализированных СБИС

В случае полузаказных СБИС на заводе изготавливается часть микросхемы.

БМК – базовый матричный кристалл. БМК содержит нескоммутированные транзисторы, которые сгруппированы в базовой ячейки – простейшие функциональные или логические преобразователи. Для специализации БМК необходимо осуществить соединение транзисторов внутри базовых ячеек. Это достигается путем реализации на заказ от 1 до 3 слоев СБИС. Это позволяет ускорить и удешевить процесс разработки СБИС. Но, однако, для специализации БМК также необходимо сложное технологическое оборудование. А время, затраченное на проектирование, составляет 2-3 месяца.

В СБИС программируемой логики (ПЛ) в процессе массового изготовления полностью реализуются как все функциональные преобразователи так и соединения между ними. А кроме того дополнительные программные элементы, позволяющие настроить функциональные преобразователи на выполнение требуемых логических функций. До проектирования специализация СБИС ПЛ могут быть выполнены на одном рабочем месте, оснащенном ПК и программатором.

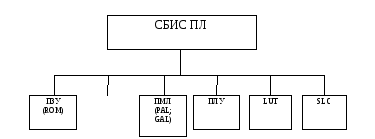

3.1 Классификация сбис пл

В качестве критериев классификации применяют следующие:

Степень интеграции

Архитектура простейшего функционального преобразователя

Организация внутренней структуры СБИС и структуры матрицы соединений функциональных преобразователей

Наличие внутренних ОЗУ

Технология изготовления программируемого элемента.

Классификация по степени интеграции

По степени интеграции БМК и СБИС ПЛ характеризуются логической емкостью. Она измеряется числом логических вентелей или элементов 2И-НЕ. В соответствии с этим СБИС делят на 4 типа:

Низкой степени интеграции – до 1500 логических вентелей

Средней степени интеграции – от 1500 до 15000

Высокой степени интеграции – от15000 до 150000

Сверхвысокой интеграции – более 150000

По архитектуре простейшего функционального преобразователя.

По архитектуре простейшего функционального преобразователя различают 6 типов.

ПЛМ (PLA)

ПЛК (PLS)

Рисунок 3.1 - Классификация СБИС ПЛ

Первые в историческом смысле СБИС ПЛ – это ПЗУ, в которых выделяют постоянные запоминающие устройства ППЗУ (PROM), репрограммируемые запоминающие устройства РПЗУ (EPROM), электрические репрограммируемые ЭППЗУ (EEPROM). ПЗУ имеет структуру функционального преобразователя, в котором можно реализовать m независимых логических функций от n переменных причем, m – разрядность шины данных ПЗУ, n – разрядность шины адреса ПЗУ.

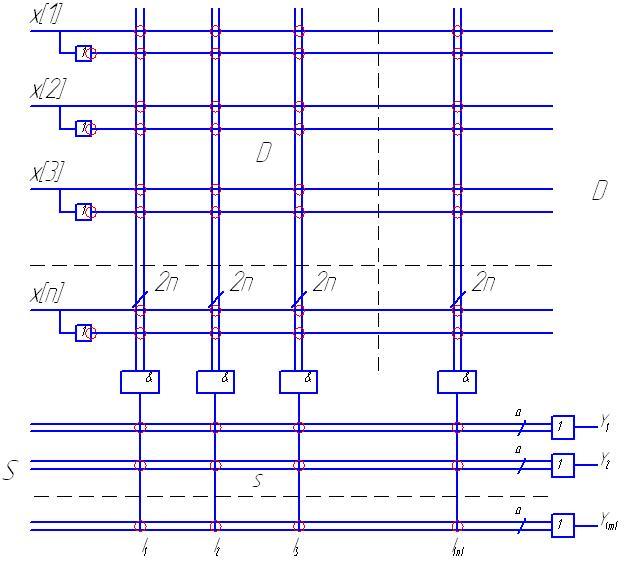

СБИС следующего поколения ПЛМ (программируемые логические матрицы) (PLA), а так же ПЛК (программируемые логические контроллеры) (PLS). Структура матрицы ПЛМ состоит из дешифратора D и шифратора S. Причем и дешифратор, и шифратор являются программируемыми.

Рисунок 3.2 - Архитектура функционального преобразователя СБИС ПЛМ.

Для обеспечения возможности реализации не только комбинационных, но и последовательных схем, на выходе шифратора добавляется триггер. Такие БИС называются программируемым логическим контроллером. Так как все логические функции представляются в дизъюнктивной нормальной форме (в форме суммы произведений), то матрица ИЛИ оказывается разряженной и занятая ей часть кристалла используется не полностью.

Следующим этапом развития СБИС ПЛ является появление СБИС программируемой матричной логики. В них дешифратор является программируемым, а шифратор имеет фиксированную структуру. Такие БИС получили название PAL, а если на выходе таких схем присутствуют регистры, то они называются GAL. Архитектура СБИС ПМЛ положена в основу программируемых логических устройств ПЛУ или PLD.

Рассмотрим структуру простейшего функционального преобразователя СБИС ПЛУ.

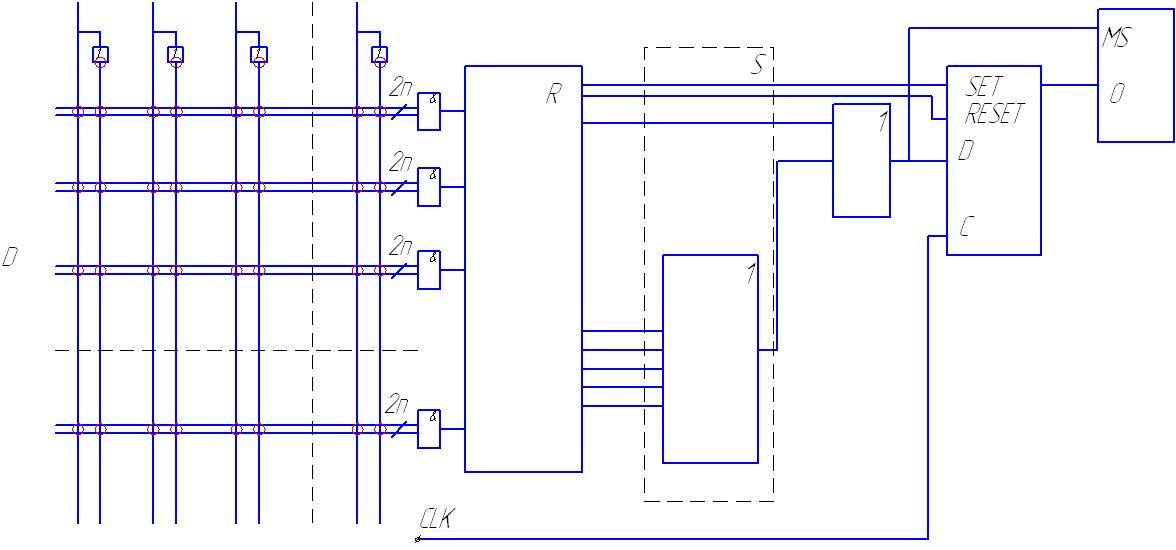

Рисунок 3.3 - Архитектура простейшего функционального преобразователя СБИС ПЛУ

В состав функционального преобразователя входят: дешифратор D в виде программируемой матрицы И, матрица размещения результатов функции R, шифратор S с элементом ИЛИ, инвертор, выполненный на сумматоре по модулю 2 (элемент «исключающий ИЛИ»), синхронный триггер и мультиплексор, позволяющие выбрать асинхронный или синхронный режим простейшего функционального преобразователя.

В настоящее время получили развитие другие архитектуры ПФП. Например табличные архитектуры, которые используют для формирования логических функций таблицы перекодировок Look Up Table, а так же архитектура SLC (Simple logic cell), объединяющая разнообразные архитектуры СБИС ПЛ, и использующая комбинационные схемы для реализации логических функций.

Организация внутренней структуры и структуры матрицы соединения.

В соответствии с этим критерием выделят одноуровневую (плоскую) и многоуровневую (Иерархическую) структуры.

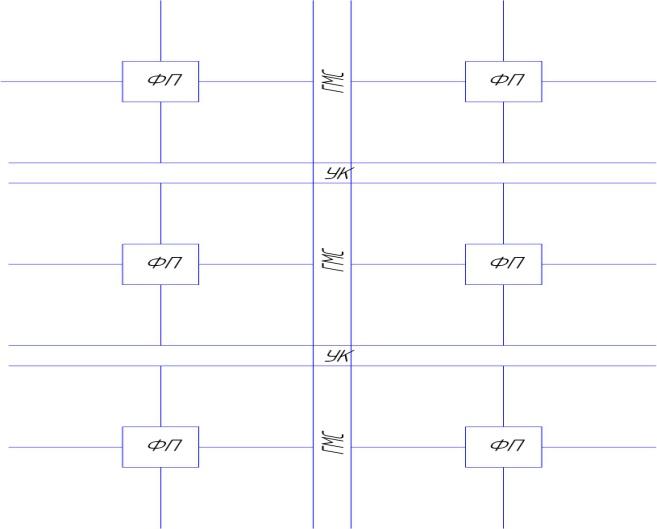

Рисунок 3.4 - Структура одноуровневой СБИС ПЛ

ФП – функциональный преобразователь.

УК – программируемый узел коммутации (может реализовать коммутацию во времени т.е. в зависимости от состояния микросхемы внутренняя коммутация тек же меняется).

ГМС – глобальная матрица соединений.

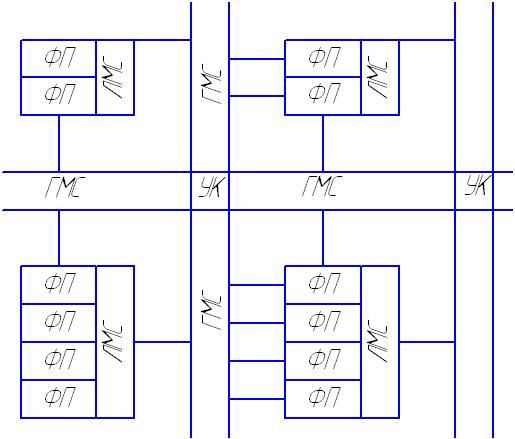

Структура многоуровневой СБИС (двухуровневая).

ЛМС – локальная матрица соединений.

Рисунок 3.5 - Структура многоуровневой СБИС ПЛ.

В иерархической структуре кроме ГМС присутствуют и локальные матрицы соединений, реализующие связи между простейшими функциональными устройствами.

Наличие внутренних ОЗУ.

Выделяют СБИС ПЛ имеющие внутренние ОЗУ и не имеющие внутренних ОЗУ. Внутреннее ОЗУ может реконфигурироваться и иметь разную структуру при сохранении того же объема.

По технологии изготовления различают пять видов.

FUSE или ANTIFUSE

EPROM – программируемые элементы допускают УФ стирание.

EEPROM – программируемые элементы допускают электрическое стирание.

FLASH – более надежная по сравнению с EEPROM.

SRAM – обеспечивает возможность неограниченных циклов перезаписи, а так же изменить конфигурацию без выключения. Однако при выключении питания конфигурация пропадает, микросхема теряет конфигурацию. Поэтому при включении питания данная микросхема должна быть заново сконфигурирована с помощью небольшой ПЗУ.