- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

2.9.2.1.Полувычитатель

Полувычитатель— логическая схема, имеющая два входа и два выхода. Полувычитатель позволяет вычислять разность A-B, где A и B — это одноразрядные двоичные числа (А-уменьшаемое, B-вычитаемое) при этом результатом будут два бита D и Bo (D — это бит разности , а Bo — бит заёма)

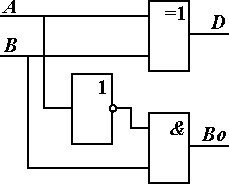

Рисунок 2.36 - Электрическая принципиальная схема полувычитателя

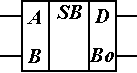

Рисунок 2.37 - Условно графическое обозначение полувычитателя

На основании схемы составим таблицу истинности

Таблица__

|

Входы |

Выходы | ||

|

A |

B |

Di |

B0 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

Уменьшаемое |

Вычитаемое |

Разность |

Заем |

2.9.2.2. Полный вычитатель

При вычитании многоразрядных двоичных чисел нужно принимать во внимание заем "единиц" в более старших разрядах. Такую операцию осуществляет полный вычитатель. Рассмотрим схему полного вычитателя с использованием двух полувычитателей.

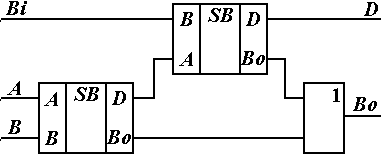

Рисунок 2.38 - Электрическая принципиальная схема полного вычитателя с использованием полувычитателей

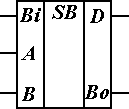

Рисунок 2.39 - Условно графическое обозначение полного вычитателя.

Пользуясь рисунком 2.38 составим таблицу истинности полного вычитателя

Таблица__

|

Входы |

Выходы | |||

|

A |

B |

Bi |

Di |

B0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

A-B-Bi |

Разность |

Заем | ||

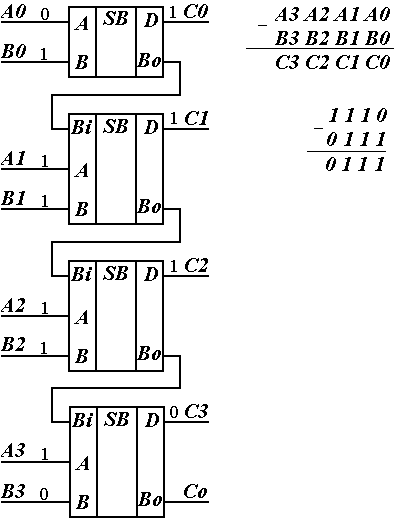

2.9.2.3. Многоразрядный вычитатель

На базе полувычитателей и полных вычитателей строятся схемы многоразрядных параллельных вычитателей. Рассмотрим схему четырехразрядного вычитателя, осуществляющего вычитание двух четырехразрядных двоичных чисел.

Работу многоразрядного вычитателя поясняет рисунок 2.40. На входы A вычитателей подается первое уменьшаемое. На входы B вычитателей вычитаемое. На выходах С формируется разность. Для обеспечения заема из младшего разряда в старший выходы заема младшего разряда подключаются к входам заема старшего разряда. Отметим, что младший разряд «сообщает» старшему о том, что он у него занял независимо от того была ли единица в старшем разряде.

Рассмотрим схему четырех разрядного параллельного вычитателя.

Рисунок 2.40 - Принцип работы многоразрядного вычитателя.

2.9.3 Умножители

С точки зрения принципа действия умножители разделяются на многотактные (сложения и сдвига) и однотактные (матричные). В любом случае произведение является результатом последовательных сложений и сдвигов.

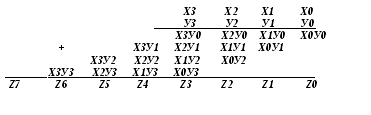

2.9.3.1. Многотактный умножитель сложения и сдвига

Рассмотрим структуру многотактного умножителя, умножающего 2 четырехразрядных двоичных числа. При умножении необходимо сформировать 4 строки частичной суммы. Строки формируются с помощью элемента И. Например X1Y0 означает логическое И между X1 и Y0. Для формирования произведения необходимы также сумматоры и устройство обеспечивающее сдвиг частичных сумм друг относительно друга, как на рисунке 2.41.

Рисунок 2.41 - Умножитель четырехразрядных чисел. Принцип работы.

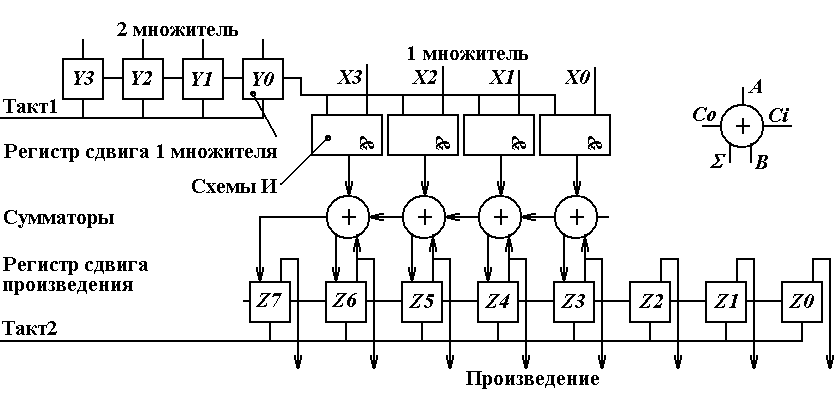

Для реализации вышеуказанных функций можно применить следующую схему многотактного умножителя:

Рисунок 2.42. Многотактный умножитель четырехразрядных двоичных чисел.

Как видно из рисунка 2.42 многоактный умножитель состоит из резистора сдвига 1 множителя, предназначенного для хранения второго множителя, сигнал ТАКТ1, осуществляющий сдвиг регистра сдвига 1 на 1 разряд вправо. Схемы И предназначены для формирования строк частичных сумм. Сумматоры предназначены для сложения частичных сумм. Регистр сдвига произведения предназначен для хранения произведения и сдвига частичных сумм на 1 разряд вправо.

Принцип работы:

В начальный момент времени в регистре сдвига произведения содержится 0, а в регистре сдвига 1 множителя записывается второй сомножитель. На входы Х0..Х3 подается первый сомножитель, при этом младший разряд регистра сдвига второго сомножителя У0 подается на входы схем И, подается первый сомножитель. На выходах схем И формируется первая строка частичной суммы, которая подается на входы А сумматоров. На входы В сумматоров подается значение из регистра сдвига произведения. В данный момент это 0. Результат сложения записывается в регистр сдвига произведения. Далее подается ТАКТ 2, осуществляющий сдвиг регистра сдвига произведения на один разряд вправо.

Подается тактовый импульс ТАКТ 1, который сдвигает регистр сдвига 1, и на выходе регистра сдвига регистра появляется разряд Y1, который подается на схемы И, формируя на выходах схем И вторую строчку частичной суммы, которая подается на входы А сумматоров. На входы В сумматоров подается сдвинутый один раз результат из регистра сдвига произведения. Результат сложения опять записывается в регистр сдвига произведения и подается ТАКТ2, по которому регистр сдвига 2 сдвигается на один разряд вправо. Далее процесс повторяется еще 2 такта ТАКТ1 и ТАКТ2, по которым формируется третья и четвертая строчки частичных сумм.

Недостатком такого умножителя является то, что умножение происходит за несколько тактов тактовой частоты. Для четырехразрядного потребуется 4 импульса ТАКТ1 и 4 импульса ТАКТ2, что ограничивает быстродействие. Достоинством является простота аппаратной реализации, особенно для многоразрядных умножителей. Указанного недостатка лишен матричный умножитель, поскольку он выполняет операцию умножения на один такт.