- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

Interfaces.By.Ru

www.itt-ltd.com

Протокол CAN, разработанный фирмой BOSCH в 80 года 20 века, изначально проектировался для нужд автомобильной промышленности. Разработанный интерфейс оказался настолько удачным, что на настоящий момент он применяется повсеместно. В том числе в промышленной автоматике и в аэрокосмическом приборостроении.

Интерфейс CAN имеет следующие основные характеристики:

Физический уровень передачи данных в CAN - спецификации не определен. Это может быть дифференциальный сигнал, передаваемый по витой паре, оптоволокно, просто открытый коллектор и т.п. Физический уровень (Physical Layer) протокола CAN определяет сопротивление кабеля, уровень электрических сигналов в сети и т.п. Существует несколько физических уровней протокола CAN (ISO 11898, ISO 11519, SAE J2411). В подавляющем большинстве случаев используется физический уровень CAN определенный в стандарте ISO 11898.

ISO 11898 в качестве среды передачи определяет двухпроводную дифференциальную линию с импедансом (терминаторы) 120 Ом (допускается колебание импеданса в пределах от 108 Ом до 132 Ом.

Максимальная скорость сети CAN в соответствие с протоколом равна 1 Mbit/s. При скорости в 1 Mbit/sec максимальная длина кабеля равна примерно 40 метрам. Ограничение на длину кабеля связано с конечной скоростью распространения сигнала и механизмом побитового арбитража (во время арбитража все узлы сети должны получать текущий бит передачи одновременно, те сигнал должен успеть распространится по всему кабелю за единичный отсчет времени в сети.

Скорость передачи задается программно и может быть до 1 Мбит/с. Пользователь выбирает скорость, исходя из расстояний, числа абонентов и емкости линий передачи. Максимальное число абонентов, подключенных к данному интерфейсу фактически определяется нагрузочной способностью примененных приемопередатчиков. Максимальная скорость передачи: 1 Mbit/s при длине линии до 40 м или - 40 Kbit/s при длине линии 1000 м. При этом практически любой CAN – контроллер допускает программирование скорости обмена - от 1 Mbit/s до 10Kbit/s

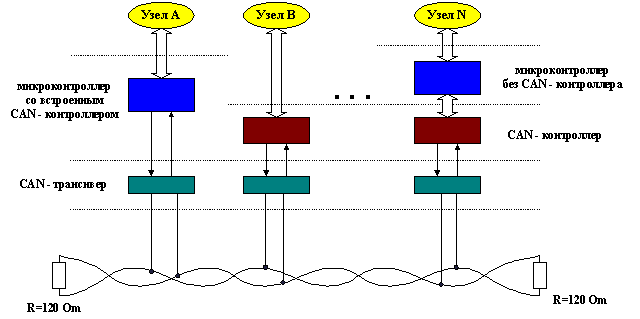

Сеть на основе интерфейса CAN представлена на рисунке

Рис. Организация сети на основе интерфейса CAN

На рис. 2 приведен пример с тремя наиболее типовыми структурами CAN – узла:

1. микроконтроллер (со встроенным CAN – контроллером) + CAN – трансивер.

2. микроконтроллер (без встроенного CAN – контроллера) + внешний CAN – контроллер + CAN – трансивер.

3. CAN – контроллер + CAN – трансивер.

Первая и вторая структуры применяются в платах с "интеллектом", в которых установлен микроконтроллер, осуществляющий, например, сбор и предобработку данных с каких-либо датчиков и способный самостоятельно передать эти данные по шине CAN. Третья структура используется для плат без "интеллекта", в которых обмен данными невозможен без управления CAN – контроллером извне.

Протокол CAN обладает развитой системой обнаружения и сигнализации ошибок. Для этих целей используется поразрядный контроль, прямое заполнение битового потока ”стаффинг”, проверка пакета сообщения CRC-полиномом, контроль формы пакета сообщений, подтверждение правильного приема пакета данных. Система арбитража протокола CAN исключает потерю информации и времени при "столкновениях" на шине.

Протокол CAN использует оригинальную систему адресации сообщений, а не привычную нам адресацию узлов. Каждое сообщение снабжается идентификатором, который определяет назначение передаваемых данных, но не адрес приемника. Любой приемник может реагировать как на один идентификатор, так и на несколько. На один идентификатор могут реагировать несколько приемников. Метод назначения идентификатора сообщения является главным архитектурным элементом CAN систем, так как идентификатор CAN-сообщения определяет относительный приоритет сообщения и следовательно время обработки сообщения (latency time). Идентификатор сообщений, 11- или 29-битный, также определяет приоритет сообщения в отношении доступа к шине. Этим обеспечиваются эффективные средства для передачи высокоприоритетных сообщений с очень малым временем ожидания, даже при высокой загруженности шины. Система может различать: с 11-битным идентификатором до 2048 различных сообщений, с 29-битным идентификатором - до 512 миллионов сообщений.

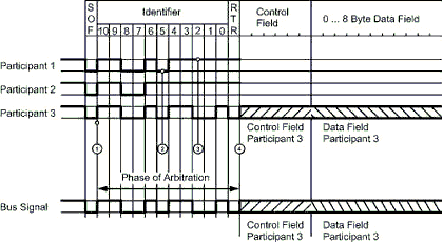

Арбитраж шины, согласно CAN-протоколу, основан на схеме арбитража c неразрушающим соперничеством. Так как всем узлам позволено начинать передачу кадров после того, как шина окажется свободной, это может привести к тому, что в одно и то же время сразу несколько узлов начнут передачу (рис. 1). Чтобы предотвратить разрушение одним узлом кадра другого узла, узел во время передачи поля идентификатора и RTR бита контролирует шину. Когда при передаче рецессивного бита (recessive bit) он обнаруживает доминирующий бит (dominant bit),(то есть передатчик обнаруживает, что на шине не те данные что он передает) он освобождает шину, немедленно останавливает передачу и продолжает принимать кадр.

Рис. №3.

Применяемый принцип арбитража гарантирует, что в любом случае наиболее высокоприоритетное сообщение всегда будет передано первым, а шина используется наиболее эффективно.

Данные в CAN передаются короткими сообщениями-кадрами стандартного формата. В CAN существуют четыре типа сообщений: Data Frame ,Remote Frame,

Error Frame, Overload Frame

Data Frame - это наиболее часто используемый тип сообщения. Он состоит из следующих основных частей: "Начало кадра", "поле арбитража", "поле контроля", "поле данных", "поле CRC", "поле подтверждения", "конец кадра".

Каждая часть имеет определенный формат

Remote Frame - это Data Frame без поля данных и с выставленным битом RTR. Основное предназначение Remote кадра - это инициация одним из узлов сети передачи в сеть данных другим узлом, запрос определенного сообщения.

Error Frame - это сообщение которое явно нарушает формат сообщения CAN. Передача такого сообщения приводит к тому, что все узлы сети регистрируют ошибку формата CAN-кадра, и в свою очередь автоматически передают в сеть Error Frame. Результатом этого процесса является автоматическая повторная передача данных в сеть передающим узлом.

Overload Frame - Имеются два вида перегрузки, которые оба приводят к передаче кадра перегрузки.

1. Внутреннее состояние приёмника, которое требует задержки следующего кадра данных или кадра удаленного запроса данных.

2. Обнаружение бита с лог. "0" в течение поля перерыва в межкадровом пространстве.

Передача кадра перегрузки из-за состояния 1 возможна только в первом битовом интервале перерыва, в то время как кадры перегрузки по состоянию 2 начинают передаваться на следующем битовом интервале после обнаружения бита с лог. "0".

Для больших задержек может быть послано несколько кадров перегрузки.

6.7 I2C

Каждый, кто занимался разработкой радиоэлектронной техники, сталкивался с ситуацией, когда для согласования уровней сигналов, выборки и адресации функционально-законченных узлов, приходится использовать огромное количество промежуточных ИС.

Для увеличения эффективности, упрощения схемотехнических решений, Philips разработала простую двунаправленную двухпроводную шину для так называемого "межмикросхемного" (inter-IC) управления.

Шина получила название - InterIC, или IIC (I2C) шина.

В настоящее время только Philips производит более 150 наименований I2C-совместимых устройств, функционально предназначенных работы в электронном оборудовании различного назначения. В их числе ИС памяти, видеопроцессоров и модулей обработки аудио- и видео-сигналов, АЦП и ЦАП, драйверы ЖК-индикаторов, процессоры со встроенным аппаратным контроллером I2C шины и многое другое.

I2C шина является одной из модификаций последовательных протоколов обмена данных. В стандартном режиме обеспечивается передача последовательных 8-битных данных со скоростью до 100 кбит/с, и до 400 кбит/с в "быстром" режиме. Для осуществления процесса обмена информацией по I2C шине, используется всего два сигнала линия данных SDA линия синхронизации SCL. Для обеспечения реализации двунаправленности шины без применения сложных арбитров шины выходные каскады устройств, подключенных к шине, имеют открытый сток или открытый коллектор для обеспечения функции монтажного "И".

Максимальное допустимое количество микросхем, подсоединённых к одной шине, ограничивается максимальной емкостью шины 400 пФ.

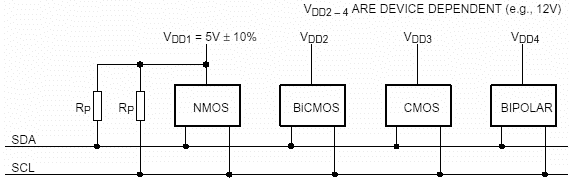

Все I2C-совместимые устройства имеют интерфейс, который позволяет им связываться друг с другом по шине даже в том случае, если их напряжение питания существенно отличается. На следующем рисунке представлен принцип подключения нескольких ИМС с различными напряжениями питания к одной шине обмена.

Рисунок___Архитектура шины I2C.

Каждое устройство распознается по уникальному адресу и может работать как передатчик или приёмник, в зависимости от назначения устройства.

Кроме того, устройства могут быть классифицированы как ведущие и ведомые при передаче данных. Ведущий - это устройство, которое инициирует передачу данных и вырабатывает сигналы синхронизации. При этом любое адресуемое устройство считается ведомым по отношению к ведущему.

Исходя из спецификации работы шины, в каждый отдельный момент в шине может быть только один ведущий, а именно то устройство, которое обеспечивает формирование сигнала SCL шины. Ведущий может выступать как в роли ведущего-передатчика, так и ведущего-приемника. Тем не менее - шина позволяет иметь несколько ведущих, накладывая определенные особенности их поведения в формировании сигналов управления и контроля состояния шины. Возможность подключения более одного ведущего к шине означает, что более чем один ведущий может попытаться начать пересылку в один и тот же момент времени. Для устранения "столкновений", который может возникнуть в данном случае, разработана процедура арбитража - поведения ведущего при обнаружении "захвата" шины другим ведущим.

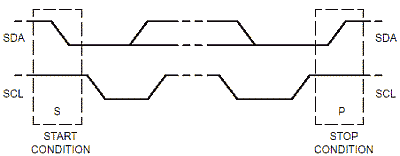

Состояние СТАРТ и СТОП

Процедура обмена начинается с того, что ведущий формирует состояние СТАРТ - ведущий генерирует переход сигнала линии SDA из ВЫСОКОГО состояния в НИЗКОЕ при ВЫСОКОМ уровне на линии SCL. Этот переход воспринимается всеми устройствами, подключенными к шине как признак начала процедуры обмена.

Рисунок ___ Старт и стоп условия

Генерация синхросигнала - это всегда обязанность ведущего; каждый ведущий генерирует свой собственный сигнал синхронизации при пересылке данных по шине.

Процедура обмена завершается тем, что ведущий формирует состояние СТОП - переход состояния линии SDA из низкого состояния в ВЫСОКОЕ при ВЫСОКОМ состоянии линии SCL.

Состояния СТАРТ и СТОП всегда вырабатываются ведущим. Считается, что шина занята после фиксации состояния СТАРТ. Шина считается освободившейся через некоторое время после фиксации состояния СТОП.

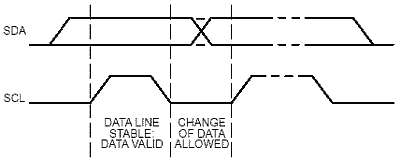

Рисунок __- Передача одного бита

При передаче посылок по шине I2C каждый ведущий генерирует свой синхросигнал на линии SCL.

После формирования состояния СТАРТ, ведущий опускает состояние линии SCL в НИЗКОЕ состояние и выставляет на линию SDA старший бит первого байта сообщения. Количество байт в сообщении не ограничено.

Спецификация шины I2C разрешает изменения на линии SDA только при НИЗКОМ уровне сигнала на линии SCL.

Данные действительны и должны оставаться стабильными только во время ВЫСОКОГО состояния синхроимпульса.

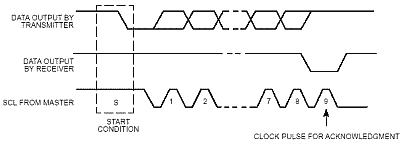

Для подтверждения приема байта от ведущего - передатчика ведомым - приемником в спецификации протокола обмена по шине I2C вводится специальный бит подтверждения, выставляемый на шину SDA после приема 8 бита данных.

Подтверждение

Таким образом передача 8 бит данных от передатчика к приемнику завершаются дополнительным циклом (формированием 9-го тактового импульса линии SCL), при котором приемник выставляет низкий уровень сигнала на линии SDA, как признак успешного приема байта.

Рисунок ___ Передача 8 бит

Подтверждение при передаче данных обязательно. Соответствующий импульс синхронизации генерируется ведущим. Передатчик отпускает (ВЫСОКОЕ) линию SDA на время синхроимпульса подтверждения. Приёмник должен удерживать линию SDA в течение ВЫСОКОГО состояния синхроимпульса подтверждения в стабильном НИЗКОМ состоянии.

В том случае, когда ведомый-приёмник не может подтвердить свой адрес (например, когда он выполняет в данный момент какие-либо функции реального времени), линия данных должна быть оставлена в ВЫСОКОМ состоянии. После этого ведущий может выдать сигнал СТОП для прерывания пересылки данных.

Если в пересылке участвует ведущий-приёмник, то он должен сообщить об окончании передачи ведомому-передатчику путем не подтверждения последнего байта. Ведомый-передатчик должен освободить линию данных для того, чтобы позволить ведущему выдать сигнал СТОП или повторить сигнал СТАРТ.

Синхронизация выполняется с использованием подключения к линии SCL по правилу монтажного И.

Это означает, что ведущий не имеет монопольного права на управление переходом линии SCL из НИЗКОГО состояния ВЫСОКОГО. В том случае, когда ведомому необходимо дополнительное время на обработку принятого бита, он имеет возможность удерживать линию SCL в низком состоянии до момента готовности к приему следующего бита. Таким образом, линия SCL будет находиться в НИЗКОМ состоянии на протяжении самого длинного НИЗКОГО периода синхросигналов.

Устройства с более коротким НИЗКИМ периодом будут входить в состояние ожидания на время, пока не кончится длинный период. Когда у всех задействованных устройств кончится НИЗКИЙ период синхросигнала, линия SCL перейдет в ВЫСОКОЕ состояние. Все устройства начнут проходить ВЫСОКИЙ период своих синхросигналов. Первое устройство, у которого кончится этот период, снова установит линию SCL в НИЗКОЕ состояние. Таким образом, НИЗКИЙ период синхролинии SCL определяется наидлиннейшим периодом синхронизации из всех задействованных устройств, а ВЫСОКИЙ период определяется самым коротким периодом синхронизации устройств.

Механизм синхронизации может быть использован приемниками как средство управления пересылкой данных на байтовом и битовом уровнях.

На уровне байта, если устройство может принимать байты данных с большой скоростью, но требует определенное время для сохранения принятого байта или подготовки к приему следующего, то оно может удерживать линию SCL в НИЗКОМ состоянии после приема и подтверждения байта, переводя таким образом передатчик в состояние ожидания.

На уровне битов, устройство такое как микроконтроллер без встроенных аппаратных цепей I2C или с ограниченными цепями может замедлить частоту синхроимпульсов путем продления их НИЗКОГО периода. Таким образом скорость передачи любого ведущего адаптируется к скорости медленного устройства.

Адресация в шине I2C

Каждое устройство, подключённое к шине, может быть программно адресовано по уникальному адресу.

Для выбора приемника сообщения ведущий использует уникальный адресную компоненту в формате посылки. При использовании однотипных устройств, ИС часто имеют дополнительный селектор адреса, который может быть реализован как в виде дополнительных цифровых входов селектора адреса, так и в виде аналогового входа. При этом адреса таких однотипных устройств оказываются разнесены в адресном пространстве устройств, подключенных к шине.

В обычном режиме используется 7-битная адресация.

Процедура адресации на шине I2C заключается в том, что первый байт после сигнала СТАРТ определяет, какой ведомый адресуется ведущим для проведения цикла обмена. Исключение составляет адрес "Общего вызова", который адресует все устройства на шине. Когда используется этот адрес, все устройства в теории должны послать сигнал подтверждения. Однако, устройства могут обрабатывать "общий вызов" на практике встречаются редко.

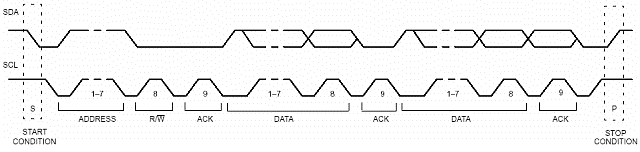

Первые семь битов первого байта образуют адрес ведомого. Восьмой, младший бит, определяет направление пересылки данных. "Ноль" означает, что ведущий будет записывать информацию в выбранного ведомого. "Единица" означает, что ведущий будет считывать информацию из ведомого.

После того, как адрес послан, каждое устройство в системе сравнивает первые семь бит после сигнала СТАРТ со своим адресом. При совпадении устройство полагает себя выбранным как ведомый-приёмник или как ведомый-передатчик, в зависимости от бита направления.

Адрес ведомого может состоять из фиксированной и программируемой части.

Часто случается, что в системе будет несколько однотипных устройств (к примеру ИМС памяти, или драйверов LED-индикаторов), поэтому при помощи программируемой части адреса становится возможным подключить к шине максимально возможное количество таких устройств. Количество программируемых бит в адресе зависит от количества свободных выводов микросхемы. Иногда используется один вывод с аналоговой установкой программируемого диапазона адресов, как это, к примеру, реализовано в ИМС SAA1064. При этом в зависимости от потенциала на этом адресном выводе ИМС, возможно смещение адресного пространства драйвера так, чтобы однотипные ИМС не конфликтовали между собой на общей шине.

Все ИМС, поддерживающие работу в стандарте шины I2C, имеют набор фиксированых адресов, перечень которых указан производителем в описаниях контроллеров.

Комбинация бит 11110ХХ адреса зарезервирована для 10-битной адресации.

В общем виде процесс обмена по шине от момента формирования состояния СТАРТ до состояния СТОП можно проиллюстрировать следующим рисунком :

Рисунок ___ Передача нескольких байт по шине I2C.

Как следует из спецификации шины, допускаются как простые форматы обмена, так и комбинированные, когда в промежутке от состояния СТАРТ до состояния СТОП ведущий и ведомый могут выступать и как приемник и как передатчик данных. Комбинированные форматы могут быть использованы, например, для управления последовательной памятью.

Во время первого байта данных можно передавать адрес в памяти, который записывается во внутренний регистр-защелку. После повторения сигнала СТАРТа и адреса ведомого выдаются данные из памяти. Все решения об авто-инкременте или декременте адреса, к которому произошел предыдущий доступ, принимаются конструктором конкретного устройства. Поэтому, в любом случае лучший способ избежать неконтролируемой ситуации на шине перед использованием новой (или ранее не используемой) ИМС следует тщательно изучить ее описание (datasheet), получив его с сайта производителя. Более того, производители часто размещают рядом более подробные инструкции по применению.

В любом случае, по спецификации шины все разрабатываемые устройства должны сбрасывать логику шины при получении сигнала СТАРТ или повторный СТАРТ и подготавливаться к приему адреса.

Тем не менее основные проблемы с использованием I2C шины возникают именно из-за того, что разработчики, "начинающие" работать с I2C шиной не учитывают того факта, что ведущий (часто - микропроцессор) не имеет монопольного права ни на одну из линий шины.

Арбитраж.

Мастер может начинать передачу только если шина свободна. Два и более мастера могут генерировать в состояние START почти одновременно. Следовательно, необходим арбитраж между ними для того, чтобы выяснить кто передаст свои данные. Для этого используется линия SDA. Она так же, как SCL выполнена по схеме монтажной &. Рассмотрим процедуру арбитража:

Рисунок __ Арбитраж.

Как видно из рисунка, если данные, передаваемые мастером, не соответствуют состоянию шины, например, на втором такте состояние шины SDA не соответствует состоянию шины SDA1 поэтому передатчик автоматически отключается от шины (SDA1=1).

6.8 SPI

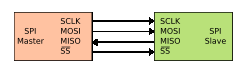

SPI (англ. Serial Peripheral Interface, SPI bus — последовательный периферийный интерфейс, шина SPI) — последовательный синхронный стандарт передачи данных в режиме полного дуплекса, разработанный компанией Motorola для обеспечения простого и недорогого сопряжения микроконтроллеров и периферии. SPI также иногда называют четырёхпроводным (англ. four-wire) интерфейсом .

В отличие от стандартного последовательного порта (standard serial port), SPI является синхронным протоколом, в котором любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим устройством (процессором). Принимающая периферия (ведомая) синхронизирует получение битовой последовательности с тактовым сигналом. К одному последовательному периферийному интерфейсу ведущего устройства-микросхемы может присоединяться несколько микросхем. Ведущее устройство выбирает ведомое для передачи, активируя сигнал «выбор кристалла» (chip select) на ведомой микросхеме. Периферия, не выбранная процессором, не принимает участие в передаче по SPI.

Рисунок __ Организация шины SPI

В SPI используются четыре цифровых сигнала:

MOSI или SI — выход ведущего, вход ведомого (англ. Master Out Slave In). Служит для передачи данных от ведущего устройства ведомому.

MISO или SO — вход ведущего, выход ведомого (англ. Master In Slave Out). Служит для передачи данных от ведомого устройства ведущему.

SCLK или SCK — последовательный тактовый сигнал (англ. Serial CLocK). Служит для передачи тактового сигнала для ведомых устройств.

CS или SS — выбор микросхемы, выбор ведомого (англ. Chip Select, Slave Select).

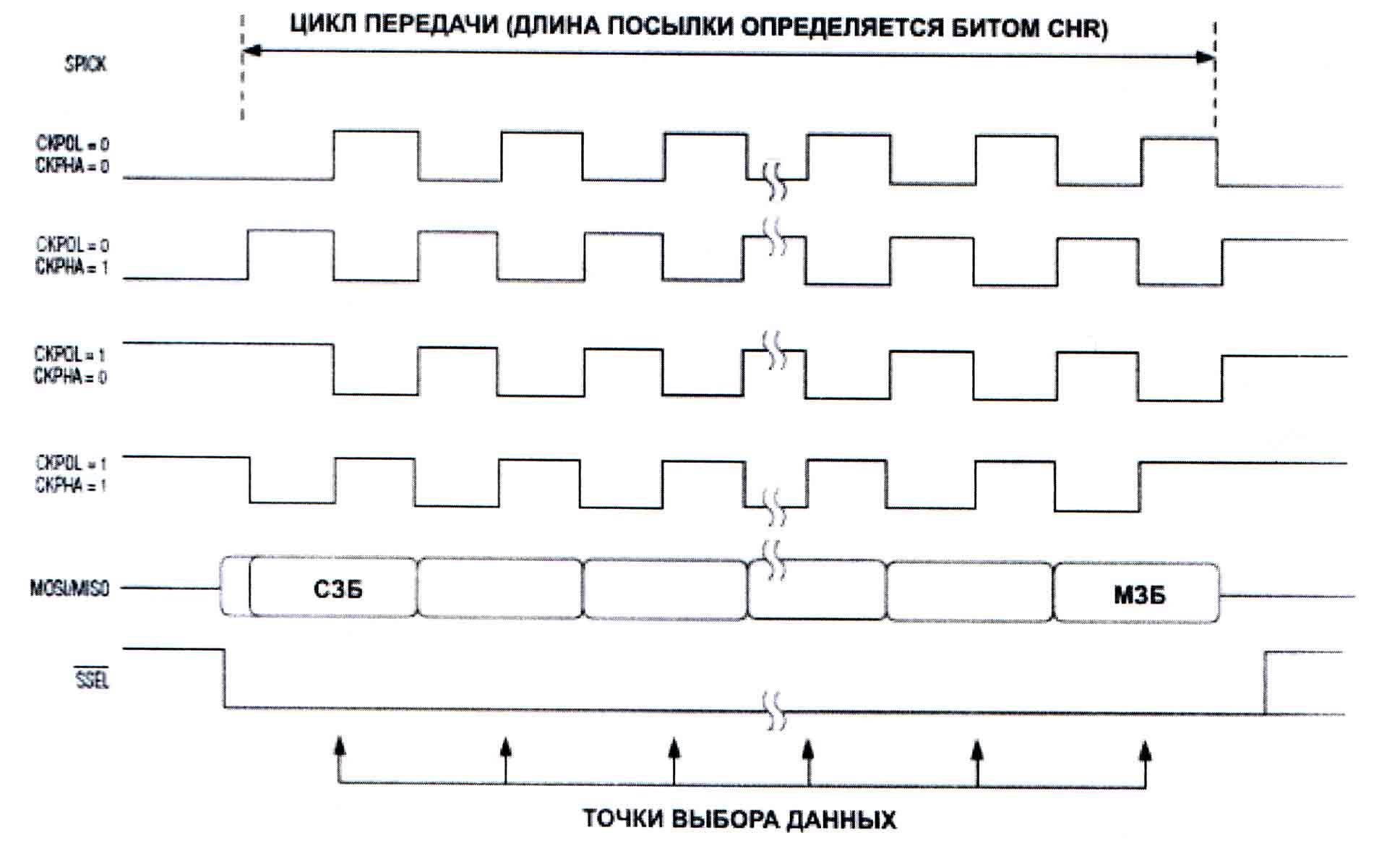

В течении передачи по интерфейсу SPI даны одновременно передаются и принимаются по двум линиям синхронно с синхроимпульсом. Полярность и фаза последовательных синхроимпульсов – это основной компонент, определяющий формат передачи данных по интерфейсу SPI. Полярность последовательных синхроимпульсов соответствует свободному состоянию линий синхронизации SCK. Фаза синхроимпульсов определяет, по какому фронту (активному или неактивному) будет осуществляться захват данных. Если логическое состояние свободной линии синхронизации определено как низкое, то активным фронтом синхроимпульса является переход от низкого к высокому, а неактивным – от высокого к низкому. Полярность и фазу можно определить с помощью двух бит, в разных реализациях они называются по разному или реализован только один из вариантов. Обозначив эти биты CKPOL и CKPHA, рассмотрим форматы передачи:

Рисунок _ возможные форматы передачи по интерфейсу SPI.