- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

2.9 Арифметические устройства.

2.9.1 Устройства сложения

Устройства сложения подразделяют на полусумматоры, полные сумматоры, и строящиеся на базе них, многоразрядные сумматоры. Рассмотрим их по порядку.

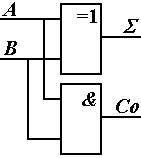

2.9.1.1 Полусумматор

Полусумматор

— логическая схема, имеющая два входа

и два выхода. Полусумматор позволяет

вычислять сумму A+B,

где A

и

B

—

это одноразрядные двоичные числа, при

этом результатом будут два бита

![]() ,

С0,

где

,

С0,

где

![]() — это бит суммы, а С0

—

бит переноса полусумматоров.

— это бит суммы, а С0

—

бит переноса полусумматоров.

Рассмотрим схему полусумматора и его условно графическое обозначение

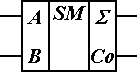

Рисунок 2.31 - Схема полусумматора

Рисунок 2.32 - Условно графическое обозначение полусумматора

Из приведенной выше схемы легко получить таблицу истинности.

Таблица Таблица истинности полусумматора.

|

Входы |

Выходы | ||

|

А |

В |

|

С0 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 Слагаемое |

2 Слагаемое |

Сумма |

Перенос |

Полусумматор осуществляет сложение двух одноразрядных двоичных чисел. Однако при сложении многоразрядных двоичных чисел необходимо учитывать переносы из младших разрядов. Эту операцию выполняет полный сумматор.

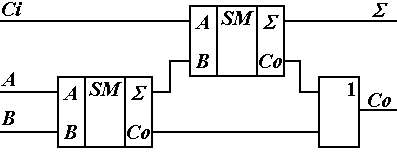

2.9.1.2 Полный сумматор

Полный сумматор предназначен для сложения двух одноразрядных двоичных чисел с учетом возможного переноса из младшего разряда, для этого полный сумматор снабжен дополнительным входом Ci. Работу сумматора поясняет его схема

Рисунок 2.33 - Схема полного сумматора с использованием двух полусумматоров

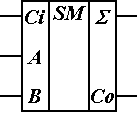

Рисунок 2.34 - Условно графическое обозначение полного сумматора

Назначение входов

Сi – вход переноса, Сo – выход переноса.

На основании принципиальной схемы составим таблицу истинности полного сумматора

Таблица истинности полного сумматора

|

Ci |

A |

B |

|

C0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

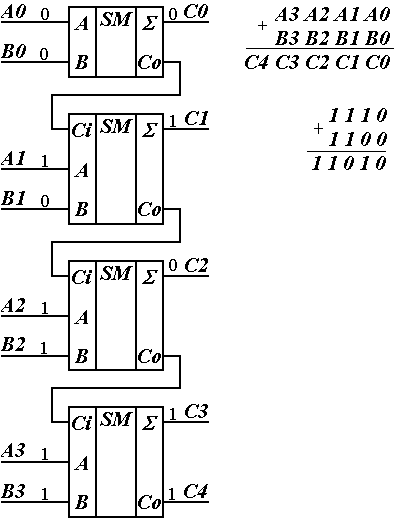

2.9.1.3. Многоразрядный сумматор

На базе полусумматоров и полных сумматоров строятся схемы многоразрядных параллельных сумматоров. Рассмотрим схему четырехразрядного сумматора, осуществляющего сложение двух четырехразрядных двоичных чисел.

Работу сумматора поясняет рисунок 2.35. На входы A сумматоров подается первое слагаемое. На входы B сумматоров второе слагаемое. На выходах С сумматоров формируется сумма. Для обеспечения переноса из младшего разряда в старший выходы переноса младшего разряда подключаются к входам переноса старшего разряда, последний выход переноса является разрядом С4 суммы.

Рисунок 2.35 - Принцип работы многоразрядного сумматора

2.9.2 Устройства выполняющие операцию вычитания

Как и устройства сложения, устройства, выполняющие операцию вычитания, делятся на: полувычитатели; полные вычитатели; многоразрядные вычитатели.