- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

2.6.1 Асинхронный rs – триггер

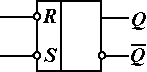

Условно графическое обозначение RS триггера представлено на рисунке 2.16.

Рисунок 2.16 - Условно графическое обозначение RS триггера.

Вход S (от английского SET) предназначен для установки триггера в единичное состояние. Вход S – инверсный, т.е. при подаче на него логического 0 триггер устанавливается в единичное состояние. Вход R (от английского RESET) предназначен для установки триггера в нулевое состояние (для сброса триггера).

Два выхода (прямой и инверсный) всегда принимают противоположное состояние. Состояние двух единиц или двух нулей на выходах называется запрещенным.

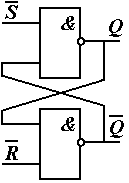

Рассмотрим схему триггера на элементах И-НЕ.

Рисунок 2.17 - Схема триггера на элементах И-НЕ

По данной схеме составим таблицу истинности:

|

Режим работы |

Входы |

Выходы | |||

|

|

|

|

Q |

|

Влияние на выход Q |

|

Запрещенное состояние |

0 |

0 |

1 |

1 |

Запрещено - не используется |

|

Установка 1 |

0 |

1 |

1 |

0 |

Для установки Q в 1 |

|

Установка 0 |

1 |

0 |

0 |

1 |

Для установки Q в 0 |

|

Хранение |

1 |

1 |

БИ |

БИ |

Зависит от предыдущего состояния |

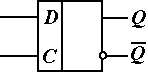

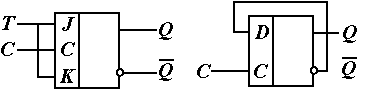

2.6.2 Синхронный d-триггер

D-триггер (D от англ. delay - задержка) - запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

Условно графическое обозначение D триггера представлено на рисунке 2.18 а его одна из возможных схем реализации с использованием логических элементов на рисунке 2.19

Рисунок 2.18 - Условно графическое обозначение D триггера.

Рисунок 2.19 - Вариант схемы D триггера с использованием логических элементов.

Вход D – вход данных, С – вход синхроимпульсов, R – вход асинхронного сброса, S – вход асинхронной установки 1, Q – прямой и инверсный выходы.

Составим таблицу истинности D триггера

|

D |

C |

|

|

Q |

|

Режим работы |

|

Х |

Х |

0 |

1 |

1 |

0 |

асинхронная установка 1 |

|

1 |

1 |

1 |

0 |

0 |

1 |

асинхронная установка 0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

хранение |

|

1 |

|

1 |

1 |

1 |

0 |

синхронная установка 1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

хранение |

|

0 |

|

1 |

1 |

0 |

1 |

синхронная установка |

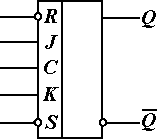

2.6.3 JK — триггер.

Это универсальный триггер, обладающий характеристикой всех других триггеров.

JK-триггер работает также как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump - прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill - убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становиться равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггер, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К. Также JK триггер может иметь входы асинхронной установки S и сброса R.

Рисунок 2.20 - Условно графическое обозначение D триггера

Таблица истинности JK триггера

|

D |

C |

|

|

Q |

|

Режим работы |

|

Х |

Х |

0 |

1 |

1 |

0 |

асинхронная установка 1 |

|

1 |

1 |

1 |

0 |

0 |

1 |

асинхронная установка 0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

хранение |

|

1 |

|

1 |

1 |

1 |

0 |

синхронная установка 1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

хранение |

|

0 |

|

1 |

1 |

0 |

1 |

синхронная установка 0 |

Режим

переключение состоит в том, что состояние

на выходах

![]() и

и

![]() изменяется на противоположное при

подаче синхроимпульса.

изменяется на противоположное при

подаче синхроимпульса.

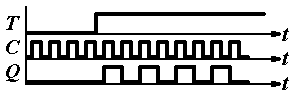

2.6.4 Т – триггер.

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

Рисунок 2.21 - T триггер на JK и D триггере

Таблица истинности Т триггера может быть представлена в виде

|

С |

T |

Q |

|

0 |

0 |

0 |

|

1 |

0 |

0 |

|

0 |

0 |

0 |

|

1 |

1 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

|

0 |

1 |

0 |

Как видно из таблицы истинности временная диаграмма работы T триггера

Рисунок 2.22 - Временная диаграмма работы T триггера.