- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

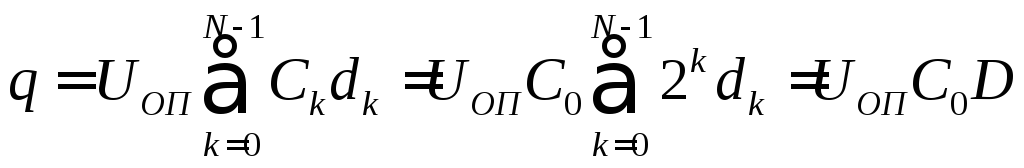

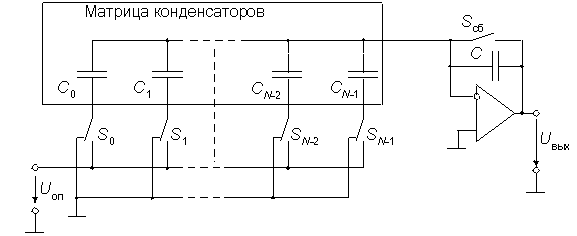

5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

Основой ЦАП этого типа является матрица конденсаторов, емкости которых соотносятся как целые степени двух. Схема простого варианта такого преобразователя приведена на рис. 11. Емкость k-го конденсатора матрицы определяется соотношением

Сk=2kC0, (17)

Цикл преобразования состоит из двух фаз. В первой фазе ключи S0…SN–1 находятся в левой позиции. Ключ сброса Sсб замкнут. При этом все конденсаторы разряжены. Во второй фазе ключ сброса Sсб размыкается. Если k-й бит входного N-разрядного слова dk=1, то соответствующий ключ Sk переключается в правую позицию, подключая нижнюю обкладку конденсатора к источнику опорного напряжения, или остается в левой позиции, если dk=0. Суммарный заряд конденсаторов матрицы с учетом (17) составит

(18)

(18)

Равный заряд получает и конденсатор С в обратной связи ОУ. При этом выходное напряжение ОУ составит

![]() (19)

(19)

Рис. 8.11. Параллельный ЦАП на коммутируемых конденсаторах

Подставив (18) в (19), найдем окончательно

![]() (20)

(20)

Для хранения результата преобразования (постоянного напряжения) в течении сколь-нибудь продолжительного времени к выходу ЦАП этого типа следует подключить устройство выборки-хранения. Хранить выходное напряжение неограниченное время, как это могут делать ЦАП с суммированием весовых токов, снабженные регистром-защелкой, преобразователи на коммутируемых конденсаторах не могут из-за утечки заряда. Поэтому они применяются, в основном, в составе аналого-цифровых преобразователей. Другим недостатком является большая площадь кристалла ИМС, занимаемая подобной схемой.

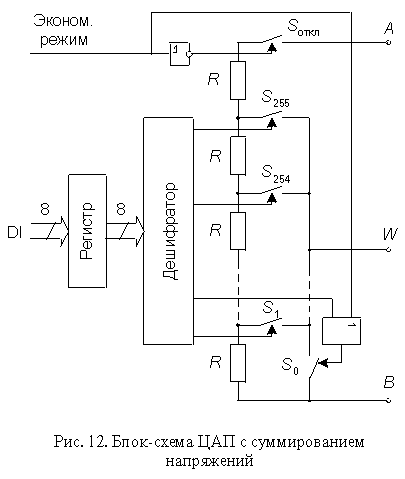

5.1.2.3 Цап с суммированием напряжений

Схема восьмиразрядного преобразователя с суммированием напряжений, изготавливаемого в виде ИМС, приведена на рис. 8.12. Основу преобразователя составляет цепь из 256 резисторов равного сопротивления, соединенных последовательно. Вывод W через ключи S0…S255 может подключаться к любой точке этой цепи в зависимости от входного числа. Входной двоичный код D преобразуется дешифратором 8х256 в унитарный позиционный код, непосредственно управляющий ключами. Если приложить напряжение UAB между выводами А и В, то напряжение между выводами W и B составит

UWB=UABD.

Достоинством данной схемы является малая дифференциальная нелинейность и гарантированная монотонность характеристики преобразования. Ее можно использовать в качестве резистора, подстраиваемого цифровым кодом. Выпускается несколько моделей таких ЦАП. Например, микросхема AD8403 содержит четыре восьмиразрядных ЦАП, выполненных по схеме на рис. 8.12, с сопротивлением между выводами А и В 10, 50 либо 100 кОм в зависимости от модификации. При подаче активного уровня на вход “Экономичный режим” происходит размыкание ключа Sоткл и замыкание ключа S0. ИМС имеет вход сброса, которым ЦАП можно установить на середину шкалы. Фирма Dallas Semiconductor выпускает несколько моделей ЦАП (например, сдвоенный DS1867) с суммированием напряжений, у которых входной регистр представляет собой энергонезависимое оперативное запоминающее устройство, что особенно удобно для построения схем с автоматической подстройкой (калибровкой). Недостаток схемы – необходимость изготавливать на кристалле большое количество (2N) согласованных резисторов. Тем не менее, в настоящее время выпускаются 8-ми, 10-ти и 12-ти разрядные ЦАП данного типа с буферными усилителями на выходе, например, AD5301, AD5311 и AD5321.

Для сопряжения используются цифро-аналоговые преобразователи (ЦАП) или аналого-цифровые преобразователи (АЦП).

Структура обработки сигналов цифровыми и аналоговыми преобразователями: