- •1. История эвм и основные определения

- •1.1 История создания эвм

- •1.2 Принципы фон Неймана

- •1.3 Особенности современных компьютеров

- •1.4 Развитие программного обеспечения

- •1.5 История пэвм

- •1.6 Появление ibm pc

- •1.7 Принцип открытой архитектуры

- •1.8 Развитие компьютеров ibm pc

- •2. Основы цифровой электроники

- •2.1. Числа, используемые в цифровой электронике. Двоичная система счисления

- •2.1.1. Перевод чисел из десятичной системы счисления в двоичную и обратно

- •2.1.2. Двоичная арифметика

- •2.1.3. Представление отрицательных чисел в двоичной системе счисления

- •2.1.4. Представление чисел c плавающей точкой в двоичной системе счисления

- •2.2 Другие системы счисления, используемые в микропроцессорной технике

- •2.2.1 Шестнадцатеричная система счисления

- •2.2.2 Двоично-десятичная система счисления

- •2.3. Базовые логические элементы

- •2.3.1. Формы описания логических элементов

- •2.3.2. Универсальный характер логического элемента и-не.

- •2.3.3. Логические элементы с числом входов больше двух

- •2.3.4. Интегральные схемы

- •2.3.5. Конструирование схемы по таблице истинности.

- •2.4. Классификация цифровых схем

- •2.5. Комбинационные схемы

- •2.5.1. Мультиплексор

- •2.5.2. Демультиплексор

- •2.5.3 Дешифратор

- •2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

- •2.6. Последовательные схемы

- •2.6.1 Асинхронный rs – триггер

- •2.6.2 Синхронный d-триггер

- •2.7 Двоичные счетчики

- •2.8 Регистры

- •2.9 Арифметические устройства.

- •2.9.1 Устройства сложения

- •2.9.1.1 Полусумматор

- •2.9.1.2 Полный сумматор

- •2.9.1.3. Многоразрядный сумматор

- •2.9.2 Устройства выполняющие операцию вычитания

- •2.9.2.1.Полувычитатель

- •2.9.2.2. Полный вычитатель

- •2.9.2.3. Многоразрядный вычитатель

- •2.9.3 Умножители

- •2.9.3.1. Многотактный умножитель сложения и сдвига

- •2.9.3.2 Матричный умножитель

- •3 Программируемые логические интегральные схемы (плис)

- •3.1 Классификация сбис пл

- •3.2 Язык описания аппаратуры ahdl

- •If high then

- •Io: bidir

- •Variable

- •Variable

- •If load then

- •4 Микропроцессорная техника

- •4.1 Общая структура микроЭвм.

- •4.2 Микропроцессорный комплект бис кр580 или intel8080.

- •4.3 Архитектура микропроцессора кр580ик80 (i8080)

- •4.3.1 Состав бис

- •4.3.2 Описание выводов микросхемы

- •4.3.3 Команды микропроцессора кр580ик80

- •4.3.3.1 Группа команд пересылки

- •4.3.3.2 Группа арифметических команд

- •4.3.3.3 Группа логических команд

- •4.3.3.3 Группа команд передачи управления

- •4.3.3.4. Группа команд работы со стеком, ввода-вывода и управления регистрами процессора;

- •4.4 Программируемый контроллер прерывания (пкп) кр580вн59

- •4.5 Архитектура программируемого таймера кр580ви53

- •4.6 Архитектура бис программируемого адаптера параллельного интерфейса кр580вв55.

- •4.7 Программируемый контроллер режима прямого доступа к памяти кр580 вт57.

- •4.8 Программируемый контроллер последовательного интерфейса кр580вв51

- •5. Сопряжение цифровых и аналоговых устройств.

- •5.1 Цифроаналоговые преобразователи

- •5.1.1.1 Цап с широтно-импульсной модуляцией

- •5.1.1.2 Последовательный цап на переключаемых конденсаторах

- •5.1.2 Параллельные цап

- •5.1.2.1 Цап с суммированием весовых токов

- •5.1.2.2 Параллельный цап на переключаемых конденсаторах (цап с суммированием зарядов)

- •5.1.2.3 Цап с суммированием напряжений

- •5.1.3 Параметры цап

- •5.1.3.1 Статические параметры

- •5.1.3.2 Динамические параметры

- •5.1.3.3 Шумы цап

- •5.2. Аналого цифровые преобразователи

- •5.2.1 Параллельные ацп

- •5.2.2 Последовательные ацп

- •5.2.2.1 Ацп последовательного счета

- •5.2.2.2 Ацп последовательного приближения

- •5.2.2.3 Интегрирующие ацп

- •5.2.2.3.1 Ацп многотактного интегрирования

- •5.2.2.3.2 Сигма-дельта ацп

- •5.2.2.3.3 Преобразователи напряжение-частота

- •5.2.3 Последовательно-параллельные ацп

- •5.2.3.1 Многоступенчатые ацп

- •5.2.3.2 Многотактные последовательно-параллельные ацп

- •5.2.3.3 Конвеерные ацп

- •5.2.4 Параметры ацп

- •6. Интерфейсы, применяемые в микропроцессорных системах и микроконтроллерах.

- •6.3 IrDa (http://www.Gaw.Ru)

- •6.4 Ieee 1284 (Centronics, ecp, epp)

- •Interfaces.By.Ru

- •6.9 1Wire

- •6.10. Jtag

- •6.11 Механизмы кодирования передаваемых в последовательном коде данных

3.2 Язык описания аппаратуры ahdl

(Бродин Б.В., Калинин А.В. Системы на микроконтроллерах и СБИС программируемой логики. М.: Изд. ЭКОМ, 2002г., 2000с.)

В России широкое распространение получили программируемые логические схемы

3.2.1.

Оператор оценивает значение выражения и по нему выбирает режим работы схемы в соответствии со списком.

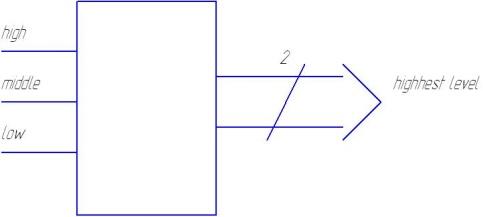

Рассмотрим реализацию логики оператора if на AHDL. В качестве примера возьмем кодировщик приоритета, который преобразует уровень самого приоритетного активного входа в его значение.

SUBDESIGN priority

{low, middle, high: INPUT;

highest_level [1..0]: OUTPUT;

}

BEGIN

If high then

highest_level [ ]=3;

ELSIF middle THEN

highest_level [ ]=2;

ELSIF low THEN

highest_level [ ]=1;

ELSE

highest_level [ ]=0;

END IF

END.

На выходе схемы получается код, соответствующий приоритету того входа, на который подана логическая единица. Если ни один вход не равен 1, то схема выдает 0.

Логическая операция CASE.

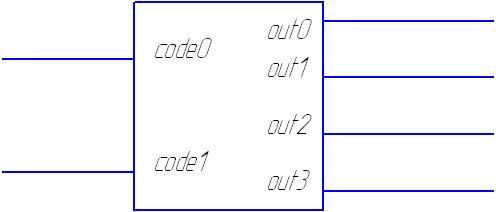

Рассмотрим пример, реализующий функцию дешифратора, преобразующего код из двухразрядного в четырехразрядный.

SUBDESIGN decoder

{code[1..0]: INPUT;

out[3..0] :OUTPUT;

}

BEGIN

CASE code [ ] IS

WHEN 0 => OUT[ ]=B”0001”;

WHEN 1 => OUT[ ]=B”0010”;

WHEN 2 => OUT[ ]=B”0100”;

WHEN 3 => OUT[ ]=B”1000”;

END CASE

END.

С помощью операторов IF и CASE можно проектировать дешифраторы. Однако схема сгенерирования компилятором устройства получается весьма сложной. Поэтому в AHDL введены специальные функции, описывающие дешифратор. Для описания дешифраторов используется объявление таблиц истинности TABLE.

Рассмотрим пример, реализующий дешифратор двоичного кода в сигнал семисегментного индикатора.

SUBDESIGN 7segment

{i[3..0]: INPUT;

a,b,c,d,e,f,g: OUTPUT

}

BEGIN

TABLE

i[3..0]=> a,b,c,d,e,f,g;

H”0”=>1,1,1,1,1,1,0;

H”1”=>0,1,1,0,0,0,0;

H”2”=>1,1,0,1,1,0,1;

H”3”=>1,1,1,1,0,0,1;

H”4”=>0,1,1,0,0,1,1;

H”5”=>1,0,1,1,0,1,1;

H”6”=>1,0,1,1,1,1,1;

H”7”=>1,1,1,0,0,0,0;

H”8”=>1,1,1,1,1,1,1;

H”9”=>1,1,1,1,0,1,1;

H”A”=>1,1,1,0,1,1,1;

H”B”=>0,0,1,1,1,1,1;

H”C”=>1,0,0,1,1,1,0;

H”D”=>0,1,1,1,1,0,1;

H”E”=>1,0,0,1,1,1,1;

H”F”=>1,0,0,0,1,1,1.

END TABLE;

END.

В этом примере в таблице перечислены все возможные шестнадцатеричные цифры и соответствующие им состояния выводов. Если необходимо реализовать дешифратор, учитывающий «не все» состояния входов т.е. с повторяющимися (несущественными) состояниями, то такие состояния обозначают символом Х. например рассмотрим дешифратор, реализующий определение области памяти, к которой обращается микропроцессор. Т.е. всю память разделим на несколько участков:

ПЗУ (имеющие адреса, начинающиеся с 00)

ФЗУ (имеющие адреса, начинающиеся с 100)

А так же 3 устройства, имеющие конкретные адреса.

SUBDESIGN decode3

{ Addr [15..0], m.io: INPUT;

ROM, RAM, PRINT, SP [2..1]: OUTPUT

}

BEGIN

TABLE

m_io, addr [15..0] => ROM, RAM, PRINT, SP [];

1, B “00xxxxxxxxxxxxx” => 1, 0, 0, B “00”;

1, B “100xxxxxxxxxxxx” => 0, 1, 0, B “00”;

0, B “0000010101100000” => 0, 0, 1, B “00”;

0, B “0001010110101100” => 0, 0, 0, B “10”;

0, B “0000110111010011” => 0, 0, 0, B “01”;

END TABLE;

END.

m_io предназначен для выбора к чему обращается микропроцессор. Если m_io = 1, то микропроцессор обращается к памяти. Если m_io = 0, то микропроцессор обращается к устройству ввода и вывода.

Использование для переданных значений по умолчанию на языке AHDL.

Можно определить значение по умолчанию для узла или группы, которые будут автоматически использоваться для них, если в файле их значения не будут заданы. Язык AHDL позволяет присваивать значения узлу или группе неоднократно и, если произойдет конфликт, система автоматически будет использовать значение по умолчанию. Если значения по умолчанию не были заданы, то узлам и группам автоматически присваивается значение GND или все 0. Значение по умолчанию можно использовать и в условных операторах IF и CASE.

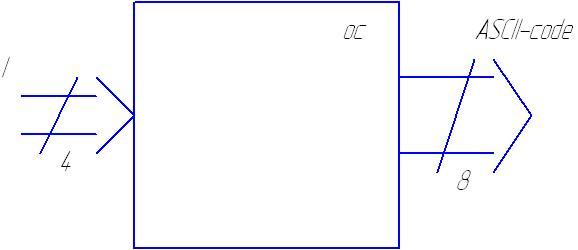

Рассмотрим пример:

Пусть на вход системы подается шестнадцатеричный одноразрядный код. На выходе системы должен появиться соответствующий ASCII код. А если одновременно поданы сигналы на несколько входов, то устройство должно выдавать «?».

SUBDESIGN Default 1

{ i [3..0]: INPUT;

ASCII_CODE OUTPUT;}

BEGIN

DEFAULTS

ASCII_CODE [] = b “01111111”; % “?”

END DEFAULTS

TABLE

I [3..0] => ASCII_CODE;

B “1000” => B “01100001”; % “a”

B “0100” => B “01100010”; % “b”

B “0010” => B “01100011”; % “c”

B “0001” => B “01100100”; % “d”

END TABLE;

END.

Реализация двунаправленных выводов.

Порты программируемых микросхем в устройствах могут быть заданы как двунаправленные (BIDIR). Порты микросхемы (ножки микросхемы) так и обозначаются BIDIR, а подключение к ним осуществляется с помощью устройств, построенных на примитиве TRI (тристабильный вывод).

Рассмотрим триггер, который делает выборку значения, найденного на шине с тремя состояниями, а так же может передать обратно на шину хранимое значение.

SUBDESIGN BUS_REG

{ CLIK, OF: INPUT;