- •Путилин а.Б. Организация эвм и систем

- •Глава 11. Общая характеристика микропроцессоров 154

- •Глава 12. Интерфейсы программно-модульных и

- •Глава 13. Интерфейсы и шины персональных эвм 221

- •Введение

- •Глава 1 Представление информации в информационных системах

- •1.1. Понятие об информации и информационных процессах

- •1.2. Сигналы и информация

- •1.3. Виды информации и их классификация

- •1.4. Структура информации

- •1.5. Дискретизация сигналов при вводе в эвм

- •Контрольные вопросы

- •Глава 2 Аналоговые вычислительные устройства

- •2.1. Методы моделирования

- •2.2. Методы построения аналоговых вычислительных устройств

- •2.3. Основные характеристики аву

- •2.4. Функциональные устройства

- •2.5. Суммирующие и вычитающие устройства

- •2.6. Дифференцирующие устройства

- •2.7. Интегрирующие устройства

- •Контрольные вопросы

- •Глава 3 Цифровые вычислительные устройства

- •3.1. Основные понятия и определения цифровой вычислительной техники.

- •3.2. Характеристики эвм

- •3.3. Поколения эвм

- •Контрольные вопросы

- •Глава 4 Математическое введение в цифровую вычислительную технику.

- •4.1. Системы счисления, используемые в эвм

- •4.2. Формы представления числовой информации в эвм

- •4.3. Машинные коды чисел

- •4.4. Кодирование алфавитно-цифровой информации

- •4.5. Элементы алгебры логики

- •4.6. Функционально полные системы

- •4.7. Минимизация функций алгебры логики

- •Контрольные вопросы

- •Глава 5 Комбинационные цифровые устройства

- •5.1. Понятие о комбинационных и последовательностных цифровых устройствах

- •5.2. Базовые интегральные логические элементы

- •5.3. Синтез кцу

- •Контрольные вопросы

- •Глава 6 Типовые кцу

- •6.1. Дешифраторы

- •6.2. Шифраторы

- •6.3. Мультиплексоры

- •6.4. Сумматоры

- •Контрольные вопросы

- •Глава 7 Анализ работы кцу

- •7.1. Быстродействие кцу

- •7.2. Состязания в кцу

- •Контрольные вопросы

- •Глава 8 Понятие о пцу

- •8.1. Основные определения и структура пцу

- •8.2. Классификация триггеров

- •8.3. Асинхронный rs-триггер с прямыми входами

- •8.4. Синхронный rs–триггер со статическим управлением

- •8.5. Универсальный jk–триггер

- •Контрольные вопросы

- •Глава 9 Типовые пцу

- •9.1. Регистры

- •9.2. Cчетчики

- •9.3. Сумматоры на основе пцу

- •9.4. Построение запоминающих устройств

- •Контрольные вопросы

- •Глава 10 Аналого-цифровые и цифро-аналоговые преобразователи

- •10.1. Аналого-цифровые преобразователи (ацп)

- •10.2. Ацп с интегрированием

- •10.3. Ацп c последовательным сравнением

- •10.4. Ацп с преобразованием измеряемой величины в кодируемый временной интервал

- •10.5. Ацп двоичного поразрядного уравновешивания

- •10.6. Основные характеристики ацп

- •10.7. Цифро-аналоговые преобразователи (цап)

- •Контрольные вопросы

- •Глава 11 Общая характеристика микропроцессоров

- •11.1. Использование микропроцессоров в иит

- •11.2. Структура микропроцессоров

- •11.3. Классификация микропроцессоров

- •11.4. Программное управление мп

- •11.5. Особенности построения модульных мп

- •11.6. Принципы организации эвм с использованием мп

- •Контрольные вопросы

- •Глава 12 Интерфейсы информационных и вычислительных систем

- •12.1. Назначение и характеристики интерфейсов

- •12.2. Принципы организации интерфейсов

- •12.3. Классификация интерфейсов

- •12.4. Системные интерфейсы мини- и микроЭвм. Общая характеристика системных интерфейсов

- •12.5. Интерфейсы мини- и микроЭвм рдр –11

- •12.6. Интерфейсы мини- и микроЭвм nova

- •12.7. Интерфейсы 8- и 16-разрядных микроЭвм

- •12.8. Устройства согласования системных интерфейсов

- •Контрольные вопросы

- •Глава 13 Малые интерфейсы стандартных устройств

- •13.1. Общая характеристика

- •13.2. Интерфейс ирпр

- •13.3. Интерфейс ирпс

- •Глава 14

- •14.1. Программно-модульный интерфейс iec 625-1. Общая характеристика интерфейса

- •14.2. Логическая организация интерфейса

- •14.3. Схемы поддержки и бис для интерфейса

- •14.4. Локальные системы на базе интерфейса

- •14.5. Интерфейсы магистрально-модульных и мультимикропроцессорных систем. Развитие интерфейсов системы камак

- •14.6. Интерфейсы системы Multibus

- •14.7. Интерфейс системы Fastbus

- •Контрольные вопросы

- •Глава 15 Интерфейсы и шины персональных эвм

- •15.1. Общая характеристика интерфейсов

- •15.2 Последовательный и параллельный интерфейсы

- •15.3. Универсальная последовательная шина usb

- •Топология

- •Кабели и разъемы

- •15.4. Интерфейс портативных компьютеров (pcmcia)

- •15.5. Шины персональных компьютеров эвм серии pc/at

- •Факс-модем

- •Принтер

- •15.6. Локальные шины (Local bus и vl-bus)

- •15.7. Интерфейс FireWare

- •Контрольные вопросы

- •Литература

- •Термины и определения

Контрольные вопросы

Какое устройство называется последовательностным? Опишите его структуру.

Проведите классификацию триггеров.

Каковы основные характеристики триггеров?

Опишите работу RS-триггера с прямыми входами с помощью структурной схемы, таблицы истинности.

Опишите работу RS-триггера со статическим управлением с помощью структурной схемы, таблицы истинности.

Опишите работу универсального JK-триггера по структурной схеме и таблице истинности.

Опишите работу Т-триггера по структурной схеме и таблице истинности.

Опишите работу D-триггера по структурной схеме и таблице истинности.

Глава 9 Типовые пцу

9.1. Регистры

Регистром называется последовательностное цифровое устройство, используемое для хранения и выполнения логических преобразований над n-разрядным двоичным числом. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано некоторое КЦУ, с помощью которого обеспечивается выполнение логических операций или микроопераций над n-разрядными словами в ПЦУ. В регистре могут выполняться следующие микрооперации: прием слова из другого ПЦУ, передача слова из регистра в другое ПЦУ, поразрядные логические операции, сдвиг слова влево или вправо на заданное число разрядов, преобразование последовательного кода слова в параллельный и обратно, установка регистра в начальное состояние (сброс). Схемы выполнения микроопераций реализуется с помощью КЦУ.

Схема

регистра для хранения n-разрядного

двоичного слова приведена на рис.

9.1.1а. Регистр S

состоит из n

триггеров. Состояние регистра определяется

состоянием триггеров. Оно представляется

набором выходных сигналов в парафазном

коде

![]() .

На регистр S

может быть подано для хранения двоичное

n-разрядное

слово X={xn,

xn-1,

..., x1}

с помощью совокупности входных сигналов

в парафазном коде

.

На регистр S

может быть подано для хранения двоичное

n-разрядное

слово X={xn,

xn-1,

..., x1}

с помощью совокупности входных сигналов

в парафазном коде

![]() .

.

Если на входы поступают сигналы Xi, равные 0 или 1, то триггеры регистра S устанавливаются в состояния в соответствии со значениями переменных Xi. Триггеры регистра сохраняют значение S=X до прихода новых входных сигналов. В регистре S(n) каждый i-ый элемент (триггер) соответствует двоичной переменной Si и является i-ым разрядом регистра S. Число разрядов в регистре определяет его длину.

Используемое для регистров условное обозначение дано на рис. 9.1.1б. Указываются наименование регистра (S), старший (n) и младший (1) разряды.

Состояние регистра представляется целым числом в двоичной системе счисления. Для сокращения записи состояния регистра можно использовать восьмеричную и шестнадцатеричную формы представления двоичных чисел. Состояние регистра можно представить не только в двоичном алфавите, но и в любом другом.

Рис. 9.1.1. Структурная схема регистра и его обозначение

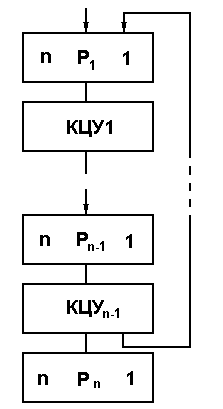

Регистры играют важную роль при построении сложных цифровых устройств. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом с помощью соответствующих схем КЦУ рис. 9.1.2.

Рис. 9.1.2. Структурная схема цифрового устройства, использующего регистры и КЦУ

Анализ схемы регистра позволяет отметить характерную особенность - однородность (регулярность) структуры.

Регистр состоит из однотипных элементов (триггеров), которые регулярно размещены друг относительно друга. Однородность элементов с регулярным размещением их в регистре позволяет существенно упростить процессы изготовления, контроля, эксплуатации. Упрощается так же описание и изучение регистра. Регистр можно описать совокупностью однотипных автоматов. Достаточно задать автоматное описание для одного элемента регистра и указать число элементов. Регулярность схемы регистра позволяет прийти к выводу о возможности построения регулярных схем КЦУ для выполнения микроопераций на множестве однотипных элементов. Это дает возможность довольно просто осуществлять синтез схемы КЦУ, сводя его к синтезу многократно повторяющейся схемы КЦУ для одного разряда регистра и схемы, обеспечивающей взаимодействие (при необходимости) двух соседних разрядов. Такой подход позволяет свести сложное описание КЦУ в виде совокупности булевых функций от переменных к простому описанию КЦУ. При этом КЦУ можно представить в виде повторяющегося n раз набора булевых функций от конечного числа m переменных, где m<<n.

В зависимости от типа выполняемых в регистре микроопераций различаются следующие типы регистров:

с параллельным приемом и выдачей информации;

с последовательным приемом и выдачей информации;

с последовательным приемом и параллельной выдачей информации;

с параллельным приемом и последовательной выдачей информации.

В зависимости от числа входных и выходных каналов регистры делятся на однофазные (сигналы передаются по одному каналу) и парафазные (передача сигналов по двум каналам). Парафазные регистры реализуются на RS-триггерах, а однофазные - на D-триггерах. Регистры характеризуются числом разрядов и быстродействием, определяемым максимальной тактовой частотой приема, передачи и сдвига информации.

Регистры памяти

Регистр с параллельным приемом и выдачей информации называется регистром памяти. В качестве элементов регистра памяти используются синхронные D-триггеры при однофазных входных сигналах (рис. 9.1.3.) или RS-триггеры при парафазных входных сигналах (рис. 9.1.4.).

Предварительная установка регистра в нулевое состояние осуществляется посылкой “Установить 0” на асинхронные входы сброса триггеров. Изменение информации в регистре происходит после изменения сигналов на входах X при поступлении сигнала на вход синхронизации С.

«Уст. 0» «Уст. 0»

Рис. 9.1.3. Регистр памяти на Рис. 9.1.4. Регистр памяти на

D-триггерах RS-триггерах

Регистры сдвига

Регистры с последовательным приемом или выдачей информации получили название регистров сдвига.

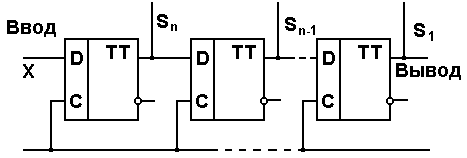

В регистре сдвига вправо первый разряд вводимого числа X1 подается на вход одного, крайнего слева, разряда Sn регистра и вводится в него при поступлении первого сигнала синхронизации С. С приходом следующего сигнала синхронизации значение X1 c выхода разряда Sn вводится в разряд Sn-1, а в разряд Sn поступает X2. В каждом такте производится сдвиг поступающей информации на один разряд вправо. После n сдвигов синхронизации весь регистр оказывается заполненным разрядами числа X, и первый разряд числа X1 появится на выходе S1. Если подать последовательность из n сигналов синхронизации и на вход разряда Sn подать X=0, то из регистра будет выводиться число X через выход S1 и в конце вывода регистр будет освобожден от хранения числа X. Регистры сдвига реализуются на D-триггерах (рис. 9.1.5.) или RS-триггерах (рис. 9.1.6.). В последней схеме для ввода информации в первый разряд включается схема инвертора.

Рис. 9.1.5. Структурная схема регистра сдвига на D-триггерах

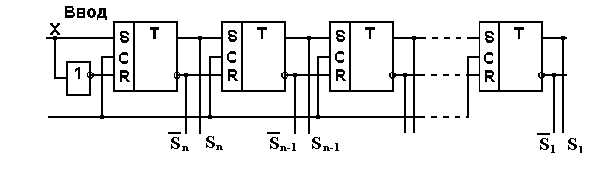

Рис. 9.1.6. Структурная схема регистра сдвига на RS-триггерах

Для параллельного вывода информации из регистра сдвига необходимо все выходы разрядов регистра сдвига подключить к различным полюсам Sn, Sn-1, ..., S1. Для реализации регистров сдвига применяются так же триггеры с динамическим управлением по входу С. Применение таких триггеров гарантирует нормальную работу регистра сдвига. Схема регистра сдвига влево на D-триггерах с динамическим управлением представлена на рис. 9.1.7.

Рис. 9.1.7. Структурная схема регистра сдвига влево

Комбинируя схемы сдвига вправо и влево и используя управляющие сигналы, можно построить регистр сдвига в обоих направлениях. Такой регистр называется реверсивными (рис. 9.1.8.). При подаче разрешающего сигнала на управляющий вход V1 включается схема сдвига вправо. Реверсивный регистр при этом превращается в регистр сдвига вправо. При подаче разрешающего сигнала на управляющий вход V2 включается схема сдвига влево. Реверсивный регистр превращается в регистр сдвига влево.

Рис. 9.1.8. Структурная схема реверсивного регистра

В регистрах сдвига влево и вправо разряды двоичного кода выходят за пределы разрядного регистра. Если соединить выход крайнего правого разряда регистра со входом крайнего левого разряда, то получим схему кольцевого (циклического) регистра сдвига. Реверсивные регистры можно использовать для построения стековых регистров, имеющих единственный общий вход и выход. Такие регистры работают по принципу “первый вошел – последний вышел”. Стековые регистры называются так же регистрами магазинного типа.

Возможно так же совмещение в одной схеме регистра памяти и регистра сдвига. На рис. 9.1.9. представлена схема, выполняющая функции 4-разрядного регистра памяти и 4-разрядного регистра сдвига влево. В каждом разряде регистра использован D-триггер с двумя D-входами и двумя управляющими V-входами. При подаче V1=0 D-входы, используемые в схеме сдвига, отключаются и схема превращается в схему регистра памяти с однофазными входами и парафазными выходами. При подаче V2=1 разрешается прием информации, которая поступает на входы в параллельной форме и при подаче разрешения на вход синхронизации С передается в регистр. Если подается V1=1, то схема превращается в схему регистра сдвига влево. В такой схеме прием информации осуществляется параллельно, а выдача либо последовательно либо параллельно.

Рис. 9.1.9. Схема, совмещающая регистр памяти и регистр сдвига влево

На рис. 9.1.10. показано условное графическое изображение схемы регистра памяти и сдвига. Стрелка, стоящая рядом с символом регистра RG, указывает направление сдвига.

Рис. 9.1.10. Графическое обозначение регистра памяти и сдвига

Применение регистров

Регистры находят применение при выполнении различных временных преобразований информации. Регистры сдвига используются в схемах умножения и деления: сдвиг числа влево и вправо на один разряд соответствует его умножению или делению на два. Регистры можно использовать для задержки передаваемой информации на n тактов. В сложных ПЦУ, состоящих из большого числа регистров, возникает необходимость передачи слов с одного регистра на другой. Это можно осуществить с помощью специальной микрооперации передачи слова. Два регистра соединяются друг с другом с помощью КЦУ, реализующего управляемую схему передачи. Передачу слова из регистра S в регистр R можно записать в виде микрооперации передачи R:=S.