- •Путилин а.Б. Организация эвм и систем

- •Глава 11. Общая характеристика микропроцессоров 154

- •Глава 12. Интерфейсы программно-модульных и

- •Глава 13. Интерфейсы и шины персональных эвм 221

- •Введение

- •Глава 1 Представление информации в информационных системах

- •1.1. Понятие об информации и информационных процессах

- •1.2. Сигналы и информация

- •1.3. Виды информации и их классификация

- •1.4. Структура информации

- •1.5. Дискретизация сигналов при вводе в эвм

- •Контрольные вопросы

- •Глава 2 Аналоговые вычислительные устройства

- •2.1. Методы моделирования

- •2.2. Методы построения аналоговых вычислительных устройств

- •2.3. Основные характеристики аву

- •2.4. Функциональные устройства

- •2.5. Суммирующие и вычитающие устройства

- •2.6. Дифференцирующие устройства

- •2.7. Интегрирующие устройства

- •Контрольные вопросы

- •Глава 3 Цифровые вычислительные устройства

- •3.1. Основные понятия и определения цифровой вычислительной техники.

- •3.2. Характеристики эвм

- •3.3. Поколения эвм

- •Контрольные вопросы

- •Глава 4 Математическое введение в цифровую вычислительную технику.

- •4.1. Системы счисления, используемые в эвм

- •4.2. Формы представления числовой информации в эвм

- •4.3. Машинные коды чисел

- •4.4. Кодирование алфавитно-цифровой информации

- •4.5. Элементы алгебры логики

- •4.6. Функционально полные системы

- •4.7. Минимизация функций алгебры логики

- •Контрольные вопросы

- •Глава 5 Комбинационные цифровые устройства

- •5.1. Понятие о комбинационных и последовательностных цифровых устройствах

- •5.2. Базовые интегральные логические элементы

- •5.3. Синтез кцу

- •Контрольные вопросы

- •Глава 6 Типовые кцу

- •6.1. Дешифраторы

- •6.2. Шифраторы

- •6.3. Мультиплексоры

- •6.4. Сумматоры

- •Контрольные вопросы

- •Глава 7 Анализ работы кцу

- •7.1. Быстродействие кцу

- •7.2. Состязания в кцу

- •Контрольные вопросы

- •Глава 8 Понятие о пцу

- •8.1. Основные определения и структура пцу

- •8.2. Классификация триггеров

- •8.3. Асинхронный rs-триггер с прямыми входами

- •8.4. Синхронный rs–триггер со статическим управлением

- •8.5. Универсальный jk–триггер

- •Контрольные вопросы

- •Глава 9 Типовые пцу

- •9.1. Регистры

- •9.2. Cчетчики

- •9.3. Сумматоры на основе пцу

- •9.4. Построение запоминающих устройств

- •Контрольные вопросы

- •Глава 10 Аналого-цифровые и цифро-аналоговые преобразователи

- •10.1. Аналого-цифровые преобразователи (ацп)

- •10.2. Ацп с интегрированием

- •10.3. Ацп c последовательным сравнением

- •10.4. Ацп с преобразованием измеряемой величины в кодируемый временной интервал

- •10.5. Ацп двоичного поразрядного уравновешивания

- •10.6. Основные характеристики ацп

- •10.7. Цифро-аналоговые преобразователи (цап)

- •Контрольные вопросы

- •Глава 11 Общая характеристика микропроцессоров

- •11.1. Использование микропроцессоров в иит

- •11.2. Структура микропроцессоров

- •11.3. Классификация микропроцессоров

- •11.4. Программное управление мп

- •11.5. Особенности построения модульных мп

- •11.6. Принципы организации эвм с использованием мп

- •Контрольные вопросы

- •Глава 12 Интерфейсы информационных и вычислительных систем

- •12.1. Назначение и характеристики интерфейсов

- •12.2. Принципы организации интерфейсов

- •12.3. Классификация интерфейсов

- •12.4. Системные интерфейсы мини- и микроЭвм. Общая характеристика системных интерфейсов

- •12.5. Интерфейсы мини- и микроЭвм рдр –11

- •12.6. Интерфейсы мини- и микроЭвм nova

- •12.7. Интерфейсы 8- и 16-разрядных микроЭвм

- •12.8. Устройства согласования системных интерфейсов

- •Контрольные вопросы

- •Глава 13 Малые интерфейсы стандартных устройств

- •13.1. Общая характеристика

- •13.2. Интерфейс ирпр

- •13.3. Интерфейс ирпс

- •Глава 14

- •14.1. Программно-модульный интерфейс iec 625-1. Общая характеристика интерфейса

- •14.2. Логическая организация интерфейса

- •14.3. Схемы поддержки и бис для интерфейса

- •14.4. Локальные системы на базе интерфейса

- •14.5. Интерфейсы магистрально-модульных и мультимикропроцессорных систем. Развитие интерфейсов системы камак

- •14.6. Интерфейсы системы Multibus

- •14.7. Интерфейс системы Fastbus

- •Контрольные вопросы

- •Глава 15 Интерфейсы и шины персональных эвм

- •15.1. Общая характеристика интерфейсов

- •15.2 Последовательный и параллельный интерфейсы

- •15.3. Универсальная последовательная шина usb

- •Топология

- •Кабели и разъемы

- •15.4. Интерфейс портативных компьютеров (pcmcia)

- •15.5. Шины персональных компьютеров эвм серии pc/at

- •Факс-модем

- •Принтер

- •15.6. Локальные шины (Local bus и vl-bus)

- •15.7. Интерфейс FireWare

- •Контрольные вопросы

- •Литература

- •Термины и определения

6.4. Сумматоры

Сумматоры представляют собой цифровые устройства для сложения чисел. Рассмотрим сложение двух целых двоичных чисел без знаков А и В с формированием их суммы S:

А = 0 1 0 1 1

+

В = 0 0 0 1 1

S = 0 1 1 1 0

Из примера следует, что при формировании результата в любом i-ом разряде необходимо учесть значение чисел в этом разряде ai и bi, а так же перенос в этот разряд из предыдущего разряда Pi. Формируются значение суммы в этом разряде Si и перенос в следующий разряд Pi+1. Сумматор может быть построен в виде комбинационного устройства, содержащего схемы для сложения отдельных разрядов (одноразрядные двоичные сумматоры). Условия функционирования одноразрядного сумматора определяются в таблице 6.3:

Таблица 6.3. Условия функционирования одноразрядного сумматора

-

Pi

ai

bi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Булевы функции, описывающие работу одноразрядного двоичного сумматора, можно записать в виде (СДНФ):

![]() (6.4.)

(6.4.)

Используя различные варианты преобразования этих функций, можно реализовать большое число структур одноразрядных двоичных сумматоров. В качестве примера рассмотрим один из возможных вариантов построения сумматора на элементах И-НЕ. Выполним преобразование функции Si:

![]()

Обозначим

![]()

Тогда

![]()

Перейдем с помощью формулы де Моргана к базису Шеффера:

![]() (6.7.)

(6.7.)

где

![]() . (6.8.)

. (6.8.)

Преобразование функции pi+1 на основе склеивания и последующего использования формулы де Моргана дает:

![]()

Структурная схема одноразрядного двоичного сумматора, соответствующая полученным в результате преобразования булевым выражениям, приведена на рис. 6.4.1.

Рис. 6.4.1. Схема одноразрядного логического сумматора

При

построении КЦУ с несколькими выходами

во многих случаях для уменьшения числа

ЛЭ целесообразно использовать общие

конструкции структурных формул. В

данном примере

![]() применяется как в булевой формуле для

Si,

так и в формуле для Pi+1.

применяется как в булевой формуле для

Si,

так и в формуле для Pi+1.

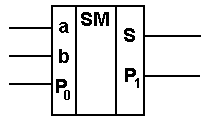

Условное графическое обозначение одноразрядного двоичного сумматора приведено на рис. 6.4.2.

Рис. 6.4.2. Обозначение одноразрядного логического сумматора.

Перенос из младшего разряда здесь обозначен P0, перенос в следующий разряд P1.

Для обработки многоразрядных чисел объединяется соответствующее число одноразрядных сумматоров. При этом отдельные разряды обрабатываемых чисел А и В подаются на входы ai и bi. На вход Pi подается перенос из предыдущего, более младшего разряда. Формируемый в данном разряде перенос Pi+1 передается в следующий, более старший разряд. Такая организация процесса формирования переноса, называемая последовательным переносом, снижает быстродействие многоразрядного сумматора, так как полученный результат в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам. Поэтому иногда организуется параллельный перенос. Для этого в каждом одноразрядном двоичном сумматоре дополнительно формируются два сигнала: образование переноса gi+1 и распространение переноса hi+1:

![]() (6.9.)

(6.9.)

Действительно, при ai=bi=1 в i-ом разряде будет иметь место формирование переноса Pi+1 в следующий разряд независимо от результата переноса из предыдущего i-ого разряда. Следовательно, можно передавать сигнал переноса для обработки старших разрядов, не дожидаясь окончания формирования переноса из младших разрядов. Однако, если хотя бы один из сигналов ai, bi равен единице, то перенос в следующий разряд будет иметь место при наличии переноса из предыдущего разряда. Поэтому можно обеспечить формирование переноса Pi+1 с использованием специальной схемы ускоренного переноса, которая обрабатывает сигналы g и h из каждого разряда по следующему правилу:

![]() (6.10.)

(6.10.)

Для реализации ускоренного переноса в одноразрядные двоичные сумматоры необходимо ввести дополнительные ЛЭ для формирования сигналов gi+1 и hi+1 согласно формулам (6.9.).