- •Путилин а.Б. Организация эвм и систем

- •Глава 11. Общая характеристика микропроцессоров 154

- •Глава 12. Интерфейсы программно-модульных и

- •Глава 13. Интерфейсы и шины персональных эвм 221

- •Введение

- •Глава 1 Представление информации в информационных системах

- •1.1. Понятие об информации и информационных процессах

- •1.2. Сигналы и информация

- •1.3. Виды информации и их классификация

- •1.4. Структура информации

- •1.5. Дискретизация сигналов при вводе в эвм

- •Контрольные вопросы

- •Глава 2 Аналоговые вычислительные устройства

- •2.1. Методы моделирования

- •2.2. Методы построения аналоговых вычислительных устройств

- •2.3. Основные характеристики аву

- •2.4. Функциональные устройства

- •2.5. Суммирующие и вычитающие устройства

- •2.6. Дифференцирующие устройства

- •2.7. Интегрирующие устройства

- •Контрольные вопросы

- •Глава 3 Цифровые вычислительные устройства

- •3.1. Основные понятия и определения цифровой вычислительной техники.

- •3.2. Характеристики эвм

- •3.3. Поколения эвм

- •Контрольные вопросы

- •Глава 4 Математическое введение в цифровую вычислительную технику.

- •4.1. Системы счисления, используемые в эвм

- •4.2. Формы представления числовой информации в эвм

- •4.3. Машинные коды чисел

- •4.4. Кодирование алфавитно-цифровой информации

- •4.5. Элементы алгебры логики

- •4.6. Функционально полные системы

- •4.7. Минимизация функций алгебры логики

- •Контрольные вопросы

- •Глава 5 Комбинационные цифровые устройства

- •5.1. Понятие о комбинационных и последовательностных цифровых устройствах

- •5.2. Базовые интегральные логические элементы

- •5.3. Синтез кцу

- •Контрольные вопросы

- •Глава 6 Типовые кцу

- •6.1. Дешифраторы

- •6.2. Шифраторы

- •6.3. Мультиплексоры

- •6.4. Сумматоры

- •Контрольные вопросы

- •Глава 7 Анализ работы кцу

- •7.1. Быстродействие кцу

- •7.2. Состязания в кцу

- •Контрольные вопросы

- •Глава 8 Понятие о пцу

- •8.1. Основные определения и структура пцу

- •8.2. Классификация триггеров

- •8.3. Асинхронный rs-триггер с прямыми входами

- •8.4. Синхронный rs–триггер со статическим управлением

- •8.5. Универсальный jk–триггер

- •Контрольные вопросы

- •Глава 9 Типовые пцу

- •9.1. Регистры

- •9.2. Cчетчики

- •9.3. Сумматоры на основе пцу

- •9.4. Построение запоминающих устройств

- •Контрольные вопросы

- •Глава 10 Аналого-цифровые и цифро-аналоговые преобразователи

- •10.1. Аналого-цифровые преобразователи (ацп)

- •10.2. Ацп с интегрированием

- •10.3. Ацп c последовательным сравнением

- •10.4. Ацп с преобразованием измеряемой величины в кодируемый временной интервал

- •10.5. Ацп двоичного поразрядного уравновешивания

- •10.6. Основные характеристики ацп

- •10.7. Цифро-аналоговые преобразователи (цап)

- •Контрольные вопросы

- •Глава 11 Общая характеристика микропроцессоров

- •11.1. Использование микропроцессоров в иит

- •11.2. Структура микропроцессоров

- •11.3. Классификация микропроцессоров

- •11.4. Программное управление мп

- •11.5. Особенности построения модульных мп

- •11.6. Принципы организации эвм с использованием мп

- •Контрольные вопросы

- •Глава 12 Интерфейсы информационных и вычислительных систем

- •12.1. Назначение и характеристики интерфейсов

- •12.2. Принципы организации интерфейсов

- •12.3. Классификация интерфейсов

- •12.4. Системные интерфейсы мини- и микроЭвм. Общая характеристика системных интерфейсов

- •12.5. Интерфейсы мини- и микроЭвм рдр –11

- •12.6. Интерфейсы мини- и микроЭвм nova

- •12.7. Интерфейсы 8- и 16-разрядных микроЭвм

- •12.8. Устройства согласования системных интерфейсов

- •Контрольные вопросы

- •Глава 13 Малые интерфейсы стандартных устройств

- •13.1. Общая характеристика

- •13.2. Интерфейс ирпр

- •13.3. Интерфейс ирпс

- •Глава 14

- •14.1. Программно-модульный интерфейс iec 625-1. Общая характеристика интерфейса

- •14.2. Логическая организация интерфейса

- •14.3. Схемы поддержки и бис для интерфейса

- •14.4. Локальные системы на базе интерфейса

- •14.5. Интерфейсы магистрально-модульных и мультимикропроцессорных систем. Развитие интерфейсов системы камак

- •14.6. Интерфейсы системы Multibus

- •14.7. Интерфейс системы Fastbus

- •Контрольные вопросы

- •Глава 15 Интерфейсы и шины персональных эвм

- •15.1. Общая характеристика интерфейсов

- •15.2 Последовательный и параллельный интерфейсы

- •15.3. Универсальная последовательная шина usb

- •Топология

- •Кабели и разъемы

- •15.4. Интерфейс портативных компьютеров (pcmcia)

- •15.5. Шины персональных компьютеров эвм серии pc/at

- •Факс-модем

- •Принтер

- •15.6. Локальные шины (Local bus и vl-bus)

- •15.7. Интерфейс FireWare

- •Контрольные вопросы

- •Литература

- •Термины и определения

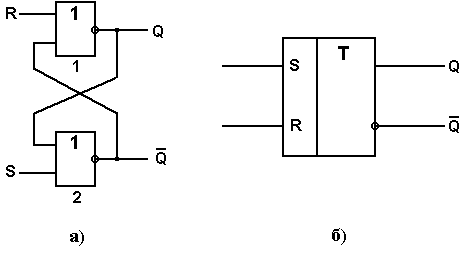

8.3. Асинхронный rs-триггер с прямыми входами

Асинхронный

RS-триггер

с прямыми входами

имеет два информационных входа R

и S,

используемые для установки соответственно

1 и 0, а так же два выхода: прямой Q

и инверсный

![]() .

RS-триггер

построен на двух логических элементах

ИЛИ-НЕ, соединенных в контур (рис.

8.3.1.а.).

.

RS-триггер

построен на двух логических элементах

ИЛИ-НЕ, соединенных в контур (рис.

8.3.1.а.).

Рис. 8.3.1. Структурная схема и обозначение RS-триггера.

Графическое изображение RS-триггера приведено на рис. 8.3.1б. Закон функционирования может быть описан табл. 8.2.

Таблица 8.2. Закон функционирования асинхронного RS-триггера

-

St

Rt

Qt

Qt+1

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

-

1

1

1

-

Как следует из таблицы, при комбинации сигналов St=1, Rt=0 триггер переходит в состояние 1 (Qt+1=1) независимо от предыдущего состояния Qt. При наборе сигналов St=0, Rt=1 триггер устанавливается в состояние0 (Qt+1=0). Комбинация сигналов St=1, Rt=1 является запрещенной, так как она приводит к нарушению работы триггера и неопределенности его состояния.

В RS-триггерах с прямыми входами управляющим воздействием обладают единичные уровни сигналов. Сигналы, которые приводят к переключению элемента, называются активными. Для элементов ИЛИ-НЕ, используемых для построения RS-триггера, активным сигналом является уровень 1.

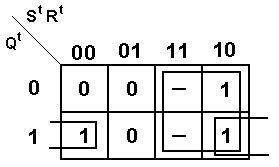

Таблица состояний триггера в момент t+1 может быть задана с помощью карт Карно (рис. 8.3.2.), которые являются аналогом диаграмм Вейча. Используя карту Карно можно построить минимальную булеву функцию для описания функционирования RS-триггера:

![]()

Рис. 8.3.2. Карта Карно асинхронного для RS-триггера.

Из полученного выражения видно, что RS-триггер устанавливается в состояние 1 при воздействии входного уровня St=1 либо остается в состоянии 1, если Rt=0 и триггер был в состоянии Qt=1

8.4. Синхронный rs–триггер со статическим управлением

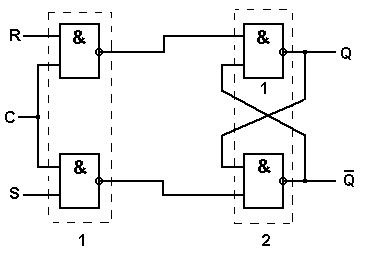

Синхронный RS–триггер со статическим управлением отличается от асинхронного наличием C-входа, на который поступают синхронизирующие (тактовые) сигналы. Синхронный триггер состоит из асинхронного RS-триггера и комбинационного цифрового устройства (рис. 8.4.1.).

Рис. 8.4.1. Структурная схема синхронного RS-триггера

Как видно из рис. 8.4.1, синхронный триггер построен из элементов И-НЕ. Схема 1 представляет собой КЦУ с тремя входами S, C, R и двумя выходами. Схема 1 состоит их двух логических схем И-НЕ. Схема 2 представляет собой асинхронный RS-триггер на элементах И-НЕ. При С=0 входные логические элементы схемы КЦУ блокированы. Их входы принимают значения 1 и не зависят от входных сигналов R и S.

Для асинхронного RS-триггера на элементах И-НЕ набор из единичных сигналов является нейтральным. Триггер будет сохранять свое состояние. При С=1 входные логические элементы схемы КЦУ открыты для передачи информации сигналов R и S на входы асинхронного RS-триггера. Следовательно, синхронный триггер при наличии разрешающего сигнала будет работать по правилам для асинхронного триггера. Закон функционирования асинхронного RS-триггера на элементах И-НЕ может быть задан табл. 8.4.

Таблица 8.4. Закон функционирования асинхронного RS-триггера

-

Ct

St

Rt

Qt

Qt+1

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

0

1

1

1

0

1

0

0

0

0

1

0

1

1

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

1

0

1

1

1

1

1

0

-

1

1

1

1

-

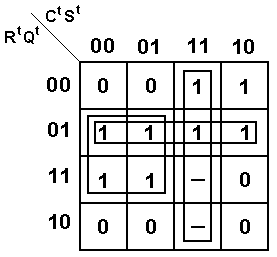

Карта Карно, описывающая работу синхронного RS-триггера на элементах И-НЕ, представлена на рис. 8.4.2.

Рис. 8.4.2. Карта Карно синхронного RS-триггера

Используя карту Карно, можно получить минимальную булеву функцию для описания работы синхронного RS-триггера:

![]()

Легко увидеть, что синхронный RS-триггер принимает состояние 1, если на входы С и S поступают уровни 1, или сохраняет единичное состояние Qt при отсутствии единичных сигналов на входе С или R.

Условное графическое изображение синхронного RS-триггера на элементах И-НЕ приведено на рис. 8.4.2. Синхронные RS-триггеры строятся и на логических элементах ИЛИ-НЕ, а так же на их сочетаниях.

Рис. 8.4.2. Обозначение синхронного RS-триггера

Общее время установления состояния триггера равно сумме задержек передачи сигнала через цепочку из трех логических элементов с задержкой tЗ в каждом:

![]() .

.

При этом длительность сигнала tС на входе С должна превышать время переключения tТ:

![]() .

.

Длительность паузы tП между двумя сигналами на входе С должна быть достаточной для переключения входных элементов в КЦУ (схема 1 на рис. 8.4.1.).

![]() .

.

Следовательно,

минимальный период повторения

синхронизирующих сигналов на входе С

равен

![]() ,

а наибольшая частота

,

а наибольшая частота

![]() .

.