- •Экзаменационный билет № 1

- •1. Стадии жизненного цикла радиоэлектронных устройств и микропроцессорных систем.

- •2. Индикатор тока.

- •Использование индикатора тока

- •Экзаменационный билет № 2

- •1. Сетевой график процесса проектирования мпс и место диагностики и отладки в нем.

- •2. Методика поиска неисправностей с помощью логического анализатора и генератора слов. Логические анализаторы

- •Анализаторы логических состояний

- •Генераторы слов.

- •Экзаменационный билет № 3

- •Параметры функционального использования мпс.

- •Контроль цп.

- •Экзаменационный билет № 4

- •1.Технические параметры мпс.

- •2. Функциональный контроль пзу.

- •Экзаменационный билет № 5

- •1.Параметры технической эксплуатации.

- •2. Тестовый контроль озу.

- •Экзаменационный билет № 6

- •1. Ошибки, неисправности, дефекты. Цель предварительных испытаний.

- •2.Контроль блоков питания мпс

- •Экзаменационный билет № 7

- •1.Техническая диагностика. Термины и определения.

- •2. Контроль увв

- •Экзаменационный билет № 8

- •1.Задачи и классификация систем технического диагностирования.

- •2. Внутрисхемный эмулятор.

- •Экзаменационный билет № 9

- •1.Проблемы контроля из-за двойственной природы мпс.

- •2. Логический анализатор.

- •Экзаменационный билет № 10

- •1.Общая методика поиска неисправностей в мпс.

- •Методы поиска неисправностей в электрических схемах электрооборудования кранов

- •2. Генераторы слов.

- •Экзаменационный билет № 11

- •1.Локализация отказов. Дерево поиска неисправностей.

- •Дерево поиска неисправностей (дпн).

- •2. Тестовый контроль последовательного канала связи.

- •Экзаменационный билет № 12

- •1.Метод тестирования микропроцессорной системы статическими сигналами.

- •2. Логический пульсатор.

- •Использование логического пульсатора

- •Тестирование «стимул—реакция» с помощью пульсатора и пробника

- •Экзаменационный билет № 13

- •1.Основные функции и состав отладочных средств. Основные функции средств отладки

- •Состав отладочных средств

- •2. Функциональный контроль параллельного канала связи.

- •Экзаменационный билет № 14

- •1.Тестирование нагрузками.

- •2. Контроль схем сброса.

- •Экзаменационный билет № 15

- •1.Сигнатурный анализатор и его применение.

- •2. Автоматизация программирования мпс.

- •Экзаменационный билет № 16

- •1.Методика поиска дефектов с помощью системы поэлементного контроля на базе сигнатурного анализатора.

- •2. Контроль системной магистрали мпс.

- •Экзаменационный билет № 17

- •1.Эмулятор микропроцессора.

- •2. Контроль систем прерывания.

- •Экзаменационный билет № 18

- •1.Ручные инструментальный средства. Номенклатура, характеристики.

- •2. Эмулятор пзу. Экзаменационный билет № 19

- •1.Классификация комплексов средств отладки.

- •2. Методика поиска дефектов в шинах питания.

- •2. Тестовый контроль клавиатуры. Экзаменационный билет № 22

- •1.Оценочные комплексы.

- •2. Контроль системного ядра мпс.

- •Экзаменационный билет № 23

- •1.Отладочные комплексы.

- •2. Контроль системы синхронизации.

- •Экзаменационный билет № 24

- •1.Комплексы развития.

- •2. Логический пробник.

Экзаменационный билет № 5

1.Параметры технической эксплуатации.

Параметры технической эксплуатации (ПТЭ) характеризуют те основные связи, которые устанавливаются внутри и вне системы на этапе функционального применения и должны отражать те изменения и возможности их определения и парирования.

Основные параметры: безотказность, долговечность, сохраняемость, ремонтопригодность (показатели надёжности).

Безотказность – свойство изделия сохранять работоспособное состояние в течение определённой наработки.

Вероятность безотказной работы: Pб.р.(T) = exp (-λT) – экспоненциальный закон надёжности, основная формула теории надёжности (где λ – интенсивность отказов).

Среднее время безотказной работы: Tср. = Tо[1-e-T/Tо].

Ремонтопригодность – свойство изделия восстанавливать работоспособное состояние после отказа.

Вероятность восстановления работоспособного состояния: Pв(t) = 1-exp(-μt), (где μ – интенсивность восстановления).

Среднее время восстановления: Tв = 1/μ .

Долговечность – сохранение работоспособности до наступления предельного состояния при установленной системе ТО и ремонта. Долговечность характеризуется ресурсом и сроком службы.

Назначенный ресурс – суммарная наработка изделия в период эксплуатации.

Срок службы – календарная продолжительность эксплуатации, по достижении которой эксплуатация прекращается.

Сохраняемость – свойство изделия непрерывно сохранять исправное и работоспособное состояние в течение времени хранения и после него.

2. Тестовый контроль озу.

Тестирование ОЗУ. В отличие от ПЗУ содержимое ОЗУ не фиксировано, поэтому простой тест CHECKSUM для них не применим.

Имеются два основных типа ОЗУ:

-статическое:

каждый бит записан в «запоминающий элемент», который сохраняет свое состояние до записи в него противоположного логического состояния;

-динамическое:

запоминающий элемент имеет более простую структуру, что увеличивает емкость микросхемы, но со временем информация из него исчезает. Обычно в динамическом ОЗУ бит хранится в виде заряда на емкости затвор — исток МОП-транзистора. Этот заряд исчезнет, если его периодически не восстанавливать в цикле регенерации. Большинство динамических ОЗУ должно иметь период регенерации 2 мс. Для регенерации динамических ОЗУ в системе предусматриваются дополнительные цифровые схемы. Чтобы устранить этот недостаток, были разработаны микросхемы ОЗУ со встроенными схемами регенерации. Эти микросхемы называются квазистатическими, так как, являясь динамическими ОЗУ, они взаимодействуют с остальными компонентами системы как статические.

Для контроля ОЗУ существует несколько алгоритмов:

шахматная доска – общая проверка ОЗУ и определение старшего адреса в МПС:

Для проверки микросхем ОЗУ необходимо записать данные в каждую ячейку, а затем считать их. Если считанный из ячейки двоичный код совпадает с записанным, полагается, что ячейка исправна. Записываемые и считываемые из ОЗУ коды называются ШАХМАТНОЙ ДОСКОЙ, так как в них логические состояния чередуются, как черные и белые клетки на шахматной доске. Обычно для проверки применяются наборы 01010101 (5516) и 10101010 (АА16).

Тест ШАХМАТНАЯ ДОСКА применяется для проверки ОЗУ после включения питания и позволяет определить старший адрес ОЗУ в системе. Многие вычислительные системы поставляются в виде базовой модели с минимальным ОЗУ, которое можно расширять до допустимого в системе максимума путем подключения дополнительных микросхем ОЗУ. Следовательно, емкость ОЗУ в системе может варьироваться от минимума в базовой модели до допустимого максимума. Тест-программа записывает шахматный набор в каждую ячейку ОЗУ, начиная с известного минимального адреса ОЗУ, и продолжает проверку по всем ячейкам до обнаружения ячейки, из которой тест-набор не считывается. Эта ячейка в системе имеет адрес, на единицу больший максимального адреса ОЗУ, и, следовательно, определяет верхнюю границу ОЗУ в системе. Обычно после этого теста емкость доступного пользователю ОЗУ индицируется для оператора на видеодисплее как адрес верхней границы. Если показываемое значение меньше ожидаемого, можно предположить наличие отказавшей микросхемы, и индицируемый адрес помогает найти эту микросхему.

Во многих случаях вместо тест-наборов 55 и АА применяются более простые тест-наборы 00 и FF. Хотя шахматные наборы и служат простым средством первоначальной проверки микросхемы ОЗУ, они не являются исчерпывающим тестом.

бегущая единица, ноль:

когда проверяется система с подозрением на отказ ОЗУ, то запускается более жесткий тест, который заключается в записи и последующем считывании кодов «шагающих единиц»:

0000 0000

0000 0001

0000 0010

0000 0100

0000 1000

0001 0000

0010 0000

0100 0000

1000 0000

Такой тест позволяет обнаруживать любую чувствительность соседних линий данных к перекрестным наведенным помехам, которые проявляются в 2-х соседних разрядах данных при считывании из проверяемой ячейки состояния 1.

В микросхеме ОЗУ линии, несущие информацию о данных и адресе, расположены очень близко друг к другу, а внутренняя топология может вызвать эффект «чувствительности к наборам». Этот эффект, в котором конкретный двоичный код вызывает наводку на другие линии адреса и данных, часто не обнаруживается шахматными кодами. К счастью для большинства пользователей, чувствительные к наборам микросхемы обычно обнаруживаются при разработке или при выборочном контроле в процессе производства. Интерференция часто возникает между линиями шины адреса из-за короткого замыкания линий вне микросхемы ОЗУ или из-за внутреннего отказа.

тест адресных шин – проверка перекрестных помех по адресным линиям:

о

бнуляется

вся память (во

все ячейки ОЗУ записывается код 00)

бнуляется

вся память (во

все ячейки ОЗУ записывается код 00)записывается код FF по адресу 0001 и осуществляется проверка ячеек микросхемы на считывание кода 00

если тест проходит, первая ячейка сбрасывается на 00, код FF записывается только по адресу 0010 и все остальные ячейки вновь проверяются на считывание кода 00

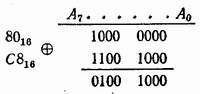

-если при считывании ячейка не дает результат 00, следует предположить «относящийся к адресу» отказ либо в самой микросхеме, либо во внешних линиях шины адреса. Подозреваемые бит или биты в шине адреса находятся с помощью операции исключающего ИЛИ выявленных параллельных адресов (начального адреса ОЗУ и адреса, по которому произошло неправильное считывание). Пусть, например, базовый адрес проверяемого ОЗУ равен 8016, а отказ обнаружен в ячейке C816. Подозреваемые линии шины адреса находятся с помощью операции исключающего ИЛИ:

В данном случае подозрительными оказываются линии А3 и А6. После этого следует проверить и локализовать отказы на обнаруженных линиях и (или) в микросхеме ОЗУ путем ее замены.

тест-галоп.