- •Экзаменационный билет № 1

- •1. Стадии жизненного цикла радиоэлектронных устройств и микропроцессорных систем.

- •2. Индикатор тока.

- •Использование индикатора тока

- •Экзаменационный билет № 2

- •1. Сетевой график процесса проектирования мпс и место диагностики и отладки в нем.

- •2. Методика поиска неисправностей с помощью логического анализатора и генератора слов. Логические анализаторы

- •Анализаторы логических состояний

- •Генераторы слов.

- •Экзаменационный билет № 3

- •Параметры функционального использования мпс.

- •Контроль цп.

- •Экзаменационный билет № 4

- •1.Технические параметры мпс.

- •2. Функциональный контроль пзу.

- •Экзаменационный билет № 5

- •1.Параметры технической эксплуатации.

- •2. Тестовый контроль озу.

- •Экзаменационный билет № 6

- •1. Ошибки, неисправности, дефекты. Цель предварительных испытаний.

- •2.Контроль блоков питания мпс

- •Экзаменационный билет № 7

- •1.Техническая диагностика. Термины и определения.

- •2. Контроль увв

- •Экзаменационный билет № 8

- •1.Задачи и классификация систем технического диагностирования.

- •2. Внутрисхемный эмулятор.

- •Экзаменационный билет № 9

- •1.Проблемы контроля из-за двойственной природы мпс.

- •2. Логический анализатор.

- •Экзаменационный билет № 10

- •1.Общая методика поиска неисправностей в мпс.

- •Методы поиска неисправностей в электрических схемах электрооборудования кранов

- •2. Генераторы слов.

- •Экзаменационный билет № 11

- •1.Локализация отказов. Дерево поиска неисправностей.

- •Дерево поиска неисправностей (дпн).

- •2. Тестовый контроль последовательного канала связи.

- •Экзаменационный билет № 12

- •1.Метод тестирования микропроцессорной системы статическими сигналами.

- •2. Логический пульсатор.

- •Использование логического пульсатора

- •Тестирование «стимул—реакция» с помощью пульсатора и пробника

- •Экзаменационный билет № 13

- •1.Основные функции и состав отладочных средств. Основные функции средств отладки

- •Состав отладочных средств

- •2. Функциональный контроль параллельного канала связи.

- •Экзаменационный билет № 14

- •1.Тестирование нагрузками.

- •2. Контроль схем сброса.

- •Экзаменационный билет № 15

- •1.Сигнатурный анализатор и его применение.

- •2. Автоматизация программирования мпс.

- •Экзаменационный билет № 16

- •1.Методика поиска дефектов с помощью системы поэлементного контроля на базе сигнатурного анализатора.

- •2. Контроль системной магистрали мпс.

- •Экзаменационный билет № 17

- •1.Эмулятор микропроцессора.

- •2. Контроль систем прерывания.

- •Экзаменационный билет № 18

- •1.Ручные инструментальный средства. Номенклатура, характеристики.

- •2. Эмулятор пзу. Экзаменационный билет № 19

- •1.Классификация комплексов средств отладки.

- •2. Методика поиска дефектов в шинах питания.

- •2. Тестовый контроль клавиатуры. Экзаменационный билет № 22

- •1.Оценочные комплексы.

- •2. Контроль системного ядра мпс.

- •Экзаменационный билет № 23

- •1.Отладочные комплексы.

- •2. Контроль системы синхронизации.

- •Экзаменационный билет № 24

- •1.Комплексы развития.

- •2. Логический пробник.

Экзаменационный билет № 23

1.Отладочные комплексы.

Отладочные комплексы предназначены для отладки МПС на программном уровне описания. Отличаются от оценочных комплексов развитым программным обеспечением, увеличенным ЗУ и усложнённым интерфейсом.

Преимущества отладочных комплексов:

возможность программирования на ASS или языке высокого уровня

широкий набор ВУ (НГМД)

тестирует развитую дисковую операционную систему

Недостатки отладочных комплексов:

накладывают ограничения на архитектуру проектируемой системы.

2. Контроль системы синхронизации.

Генератор прямоугольных импульсов, который управляет действиями микропроцессора и всех остальных компонентов вычислительной системы, называется системным генератором синхронизации. Он участвует в каждой операции, происходящей в системе, и формирует базовый временной интервал, в течение которого может происходить событие. Отказы в генераторе либо полностью выводят систему из строя, либо приводят к бессмысленным и неопределенным программным последовательностям.

Имеется множество вариантов реализации схем генераторов синхронизации — от простых RС-схем до высокостабильных кварцевых генераторов. В МПС применяются генераторы с кварцевой стабилизацией, обеспечивающие точную и стабильную частоту синхронизации.

Если системный генератор синхронизации работает слишком быстро или слишком медленно, то это отражается на устойчивости работы микропроцессорных систем. Для достижения максимальной производительности МП обычно работает на предельно допустимой частоте синхронизации fmax и любой уход вверх может привести к неработоспособности. Большинство микропроцессоров допускает частоту синхронизации меньше максимальной, но если частота слишком мала, а в системе применяются динамические ЗУ, то это может привести к потере информации в ЗУ. Обе рассмотренные проблемы возникают с большей вероятностью, когда вместо генератора с кварцевой стабилизацией используется RС-генератор. Однако и кварц иногда возбуждается на третьей гармонике, формируя более высокую, чем ожидается, частоту синхронизации.

Во многих МП требуются многофазные и не перекрывающиеся сигналы синхронизации, иногда имеющие несовместимые с ТТЛ уровни. Для КР580ИК80 требуется 2-х фазные сигналы синхронизации, которые формируются при помощи БИС 580.

Схемы синхронизации варьируются от прямого подключения кварца или RC-цепочки к БИС МП до специализированных БИС.

Параметры сигналов синхронизации проверяются довольно просто, с помощью частотомеров и осциллографов (универсальные приборы).

Экзаменационный билет № 24

1.Комплексы развития.

2. Логический пробник.

Логический пробник контролирует поведение одной точки в системе и с помощью нескольких индикаторов сообщает пользователю о том, находится проверяемая точка в состоянии логической 1, состоянии логического О или имеет промежуточный уровень. Большинство пробников показывают наличие также импульсов в точке схемы вспышками одного из индикаторов. Для показа логического состояния точки применяются либо отдельные индикаторы, либо один индикатор, который ярко светится в состоянии логической 1 и выключен в состоянии логического 0. Если проверяемый узел имеет искаженный логический уровень (завышенный 0 или заниженная 1), единственный индикатор светится вполнакала.

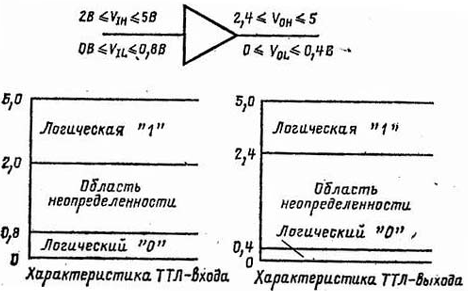

Уровни напряжения, соответствующие логическим сигналам, задаются не фиксированными потенциалами, а диапазонами напряжений.

Номинальное рабочее напряжение ТТЛ-схем составляет 5 В. Диапазоны напряжений, которые представляют два логических состояния на входе и выходе схемы, показаны на рис. 1.3. Когда выходным состоянием ТТЛ-схемы является логический 0, фактическое напряжение на биполярном транзисторе, закорачивающем выходную цепь на землю, зависит от значения отводимого на землю тока. Для ТТЛ-схем максимальное гарантированное напряжение на выходном транзисторе составляет 0,4 В при условии, что число входов, подключенных к данному выходу, не превышает заданного предела. Этот предел называется коэффициентом разветвления элемента по выходу, и для стандартных ТТЛ-схем он равен 10, т. е. выход одного ТТЛ-элемента допускается подключить максимум к 10 входам ТТЛ-элементов.

Рис.

1.3. Характеристики

входного и выходного напряжений в

ТТЛ-элементе

Рис.

1.3. Характеристики

входного и выходного напряжений в

ТТЛ-элементе

ТТЛ-схемы имеют запас помехоустойчивости из-за того, что стандартный ТТЛ-вход воспринимает напряжение до 0,8 В как уровень логического 0. Аналогично минимальный выходной уровень логической 1 составляет 2,4 В, а вход воспринимает как уровень логической 1 напряжение более 2 В.

Для ТТЛ-элемента, представленного на рис. 1.3, определяются следующие напряжения:

Vih — входное напряжение внутри диапазона, отведенного для представления состояния логической 1; обычно указывается минимальное значение, т. е. 2 В для стандартных ТТЛ-схем;

vil — входное напряжение внутри диапазона, отведенного для представления логического 0; обычно определяется максимальное значение, т. е. 0,8 В;

voh — напряжение высокого уровня на выходе; обычно задается минимальное значение, т. е. 2,4 В;

vol — напряжение низкого уровня; обычно указывается максимальное значение, т. е. 0,4 В.

Разности между гарантированными входными и выходными высоким и низким уровнями определяют возможности элемента подавлять возникающие в системе помехи.

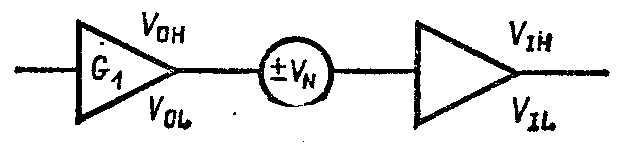

Влияние помех можно показать на простой схеме из двух элементов, приведенной на рис. 1.4. Предположим, что выход элемента G1 формирует низшее гарантированное напряжение voh высокого уровня, т. е. имеет значение 2,4 В. Источник помех, представленный на рис. 1.4 идеальным генератором напряжения vn, включен последовательно с выходом элемента G1, поэтому напряжение на входе элемента g2 равно сумме Vон и vn :

Рис. 1.4. Два ТТЛ-элемента, соединенных линией с помехами

VIH = VOH ± VN.

Напряжение VIH для гарантированной работы элемента G2 должно быть минимум 2 В, поэтому, если vn будет больше —0,4 В, входное напряжение G2 упадет ниже гарантированно входного минимума и может вызвать хаотичное поведение G2. Значение vn, которое вызывает такое нежелательное явление, называется границей помех, и в случае ТТЛ-схем оно равно 0,4В. Другими словами, ТТЛ-схемы допускают уровни наводимых помех 0,4 В и менее, прежде чем будут превышены гарантированные рабочие параметры. Аналогично, если выход G1 имеет низкий уровень, входное напряжение элемента G2 равно:

VIL = VOL ± VN.

Если vol имеет максимальное значение 0,4 В и vn превышает 0,4 В, напряжение vIL будет больше максимального значения 0,8 В, и элемент будет работать вне гарантированных пределов. Граница помех в состоянии логического 0 равна 0,4 В. Следовательно, ТТЛ-схемы в любом логическом состоянии допускают уровни помех до 0,4В, прежде чем будут превышены их рабочие параметры.

Между максимальным напряжением логического 0 и минимальным уровнем логической 1 имеется диапазон напряжений, в котором работа схемы не определена. Обычно при переходе из одного логического состояния в другое вход или выход .быстро проскакивает эту область неопределенности. Если, например, внутренний проводник, соединяющий кристалл с выводом корпуса, оборван, все подключенные к этому выводу входы будут иметь напряжение внутри области неопределенности, что в предельном случае может вызвать генерацию. Логический пробник для исследования ТТЛ-схем должен различать три возможных состояния схемы — 1, 0 и напряжение внутри области неопределенности. Для достижения универсальности пробник должен проверять и КМОП-схемы, логические пороги которых отличаются от порогов ТТЛ-схем. В отличие от ТТЛ-схем, работающих с фиксированным напряжением питания 5 В, КМОП-схемы могут работать при напряжении питания в диапазоне 3—18 В. Пороговые уровни и границы помех обычно задаются в долях номинального напряжения питания Vdd, причем типичное значение для vil равно 0,3 Vdd, а для VIH — 0,7 Vdd. В статическом режиме выходные пороги являются почти идеальными: 50 мВ для Vol и на 50 мВ ниже Vdd для VOH. Типичное значение границы помех для КМОП-схем составляет 45 % от Vdd, что намного больше, чем у ТТЛ-схем. Это объясняет выбор КМОП-схем для применения в условиях с высокими уровнями помех. Однако полное выходное сопротивление КМОП-схем примерно в 10 раз больше, чем у ТТЛ-схем, а это делает их более подверженными наводимым помехам, хотя высокая помехоустойчивость КМОП-схем не приводит к серьезным проблемам.

КМОП-схемы часто предпочитают из-за малого потребления энергии по сравнению с ТТЛ-схемами, что особенно важно при питании от аккумуляторов. Логические элементы работают в динамических схемах, где происходят частые переключения состояний. Потребление энергии КМОП-элементов быстро увеличивается с ростом частоты переключения и на частотах в диапазоне 500 кГц — 2 МГц превышает потребление энергии эквивалентных маломощных ТТЛШ-элементов. Это обстоятельство необходимо учитывать при проектировании систем, рассчитанных на малое потребление энергии, но с высокой частотой переключения, так как КМОП-схемы могут проиграть по сравнению с другими логическими семействами.

Универсальный логический пробник должен работать с ТТЛ- и КМОП-схемами, хотя во многих системах, построенных на основе КМОП-схем, применяется питание 5 В. Пробник должен индицировать логические состояния ВЫСОКИЙ и НИЗКИЙ, а также «плохие» уровни, включая выходы с разрывом и выходы типа открытого коллектора без нагрузочных резисторов. Кроме индикации статических состояний пробник должен показывать пользователю также динамическое поведение узла.

Пробник должен индицировать не только наличие коротких импульсов с высокой частотой повторения, но и прохождение одиночных коротких импульсов. Оба вида динамических сигналов индицируются посредством расширения любого короткого импульса до 50—60 мс, которых достаточно, чтобы пользователь заметил изменение состояния индикатора с «выключено» на «включено» и наоборот.

Рис.

1.5. Простой логический пробник

Рис.

1.5. Простой логический пробник

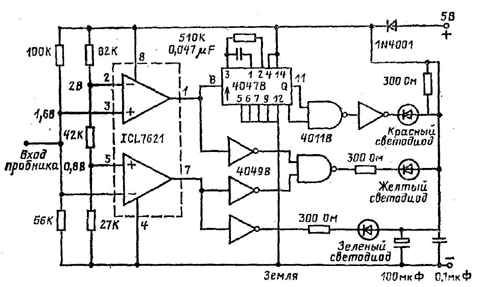

Логические пробники варьируются от простых устройств до сложных приборов, содержащих специально для них разработанные микросхемы. На рис. 1.5 показана схема логического пробника, предназначенного для проверки ТТЛ-схем.

Питание пробника осуществляется через гибкий провод от проверяемой системы. Диод 1N4001 в цепи питания предотвращает повреждение при неправильном подключении питания. С помощью резисторного делителя, незначительно нагружающего узел, вход пробника смещен примерно на уровень 1,6 В, который находится в области неопределенности для ТТЛ-схем. Вход пробника подан на сдвоенный операционный усилитель, выполненный по КМОП-технологии, который сравнивает входное напряжение пробника с фиксированными напряжениями, полученными от делителя.

Выход верхнего операционного усилителя переходит из состояния логического 0 в состояние логической 1, когда входное напряжение превышает 2 В. Выход нижнего операционного усилителя изменяется из состояния логического 0 в состояние логической 1, когда входное напряжение пробника ниже 0,8В. Если вход пробника свободен, выходы обоих операционных усилителей находятся в состоянии логического 0, что вызывает включение желтого светодиода, показывающего «плохой» уровень. Когда напряжение на входе больше 2 В, желтый светодиод выключается, а красный светодиод светится, показывая уровень логической 1. Если входное напряжение ниже 0,8 В, светится только зеленый светодиод, показывая уровень логического 0. Любой импульсный сигнал в проверяемом узле вызывает изменение выхода верхнего операционного усилителя из одного логического состояния в другое. Положительный фронт сигнала от этого операционного усилителя запускает одновибратор 4047 В примерно на 60 мс, что дает вспышку красного светодиода. Таким образом, пробник индицирует статические логические уровни высокого, низкого и промежуточного уровней напряжения, а также прохождение импульсных сигналов в узле. КМОП-схемы обеспечивают малое потребление тока от проверяемой системы (около 12 мА). Вся схема пробника размещается в корпусе с размерами 30x20x140 мм. Основным недостатком схемы является узкая полоса пропускания — 500 кГц, которая ограничивается частотными характеристиками сдвоенных операционных усилителей ICL7621, и поэтому пробник не фиксирует помехи с длительностью в десятки и сотни наносекунд.

Использование логического пробника

Главное назначение логического пробника — проверить подачу питания на микросхемы, проконтролировать статические уровни в логических элементах на правильность функционирования и установить наличие импульсов в проверяемых цепях.

С помощью логического пробника удобно проверить наличие питания на микросхемах. Почти во всех ТТЛ-элементах питание VCC=5 В обычно подается на вывод 14 (корпус DIP с 14 выводами) или на вывод 16 (корпус DIP с 16 выводами). Земля обычно подается на вы воды 7 и 8 соответственно. Впрочем, имеются и исключения из приведенных правил, например микросхема десятичного счетчика 7490, но в подавляющем большинстве ТТЛ-микросхем правила соблюдаются. Если коснуться зондом пробника выводов 14 и 16, его индикатор при наличии питания ярко засветится. Конечно, пробник не показывает значения напряжения питания, а просто сигнализирует о наличии электропитания; фактическое значение напряжения питания можно измерить с помощью цифрового вольтметра. Когда же зонд пробника касается выводов 7 или 8, индикатор должен быть выключен. Если в любом случае индикатор светится «вполнакала», следует предположить обрыв цепей, и необходимо просмотреть печатные проводники от выводов микросхемы к блоку питания.

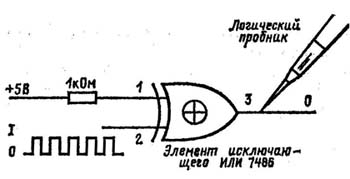

Рис. 1.8. Резервный элемент исключающего ИЛИ работает как инвертор

С помощью логического пробника можно проверить правильность функционирования логического элемента.

Когда место на печатной плате ограничено, вместо попыток разместить на ней дополнительные микросхемы часто оставляют незадействованными (резервными) логические элементы в работающих микросхемах. Рассмотрим, например, элемент исключающего ИЛИ на рис. 1.8. Микросхема 7486 содержит в одном корпусе четыре таких элемента, из которых, возможно, задействованы только три. Если в системе потребуется инвертор, его можно реализовать с помощью резервного четвертого элемента микросхемы. Касание логическим пробником вывода 1 покажет ярким свечением индикатора состояние логической 1, а касание вывода 2 — наличие импульсов. Функция элемента должна быть такой, что на выходе должна получаться инвертированная входная последовательность, поэтому при касании пробником выхода также должно быть индицировано наличие импульсов. Тот факт, что последовательность импульсов инвертирована относительно входной, по индикатору логического пробника определить невозможно. Если вместо сигнализации о наличии импульсов на выходе элемента индикатор остается выключенным, то в схеме имеется отказ, которым может быть либо отказ в самом элементе, либо закорачивание на землю вне элемента. Короткое замыкание может быть вызвано либо неаккуратной пайкой, приводящей к соединению между линией с выхода элемента и землей, либо замыканием на землю входа внутри любой из микросхем, к которой подключен выход элемента. Для определения фактического отказа необходимо либо изолировать выходной вывод либо с помощью индикатора тока установить, через какую микросхему течет ток.

В

микропроцессорной системе логический

пробник удобно применять для первоначального

контроля статических логических

уровней и проверки работоспособности

шины. Следует проверить линии шины

управления, чтобы убедиться в том, что

отказ на одной из критических

управляющих линий не препятствует

работе системы, а это может случиться,

если, например, на входе запроса

прямого доступа к памяти (![]() ),

имеющегося во многих микропроцессорах,

постоянно действует низкий уровень.

С помощью логического пробника можно

проверить и целостность печатных

проводников; если, например, микросхема

памяти не выбирается, следует проверить

наличие импульсов на ее входе

),

имеющегося во многих микропроцессорах,

постоянно действует низкий уровень.

С помощью логического пробника можно

проверить и целостность печатных

проводников; если, например, микросхема

памяти не выбирается, следует проверить

наличие импульсов на ее входе

![]() (разрешение работы кристалла) и

проследить по печатному проводнику до

того выхода дешифратора адреса, на

котором формируется сигнал

.

На печатных платах с высокой плотностью

упаковки микросхем применяются очень

узкие проводники, на которых могут

появляться микроскопические разрывы.

Ведя пробник по проводнику, можно

обнаружить разрыв, незаметный для

невооруженного глаза.

(разрешение работы кристалла) и

проследить по печатному проводнику до

того выхода дешифратора адреса, на

котором формируется сигнал

.

На печатных платах с высокой плотностью

упаковки микросхем применяются очень

узкие проводники, на которых могут

появляться микроскопические разрывы.

Ведя пробник по проводнику, можно

обнаружить разрыв, незаметный для

невооруженного глаза.