ORGANIZATsIYa_EVM

.pdf2)S2 – дополнительно отключается питание КЭШ, системной платы и процессора, но сохраняется состояние оперативной памяти

3)S3 – обесточиваются все компоненты системной платы, кроме оперативной памяти

Примечание: выполнение „SLEEP‟ [S1, S2, S3] может произойти в случае

„shut down‟, когда операционная система обнаруживает аварийную ситуацию.

ЛЕКЦИЯ N6

КЭШ ПАМЯТЬ

Тенденция к повышению производительности работы В.С. привела к необходимости ввода в архитектуру так называемой КЭШ памяти, являющейся дополнительным буфером информации между системной памятью и процессором. КЭШ память по объѐму намного меньше, чем системная память и хранящая копии еѐ ячеек, помимо накопительного блока, для данных, должна содержать индексный или тэговый блок по адресному объѐму равный накопительному. В этом индексном блоке должна храниться информация однозначно определяющая какие конкретные ячейки оперативной памяти отражаются в тех или иных ячейках накопительного блока КЭШ.

Так как системная память является адресным устройством с произвольным доступом, то в качестве тэгов используются адреса ячеек системной памяти

(полный или частичный в зависимости от архитектуры КЭШ)

Различают в основном 3 типа КЭШ:

-полностью ассоциативная,

-прямого отображения

-наборно-ассоциативная.

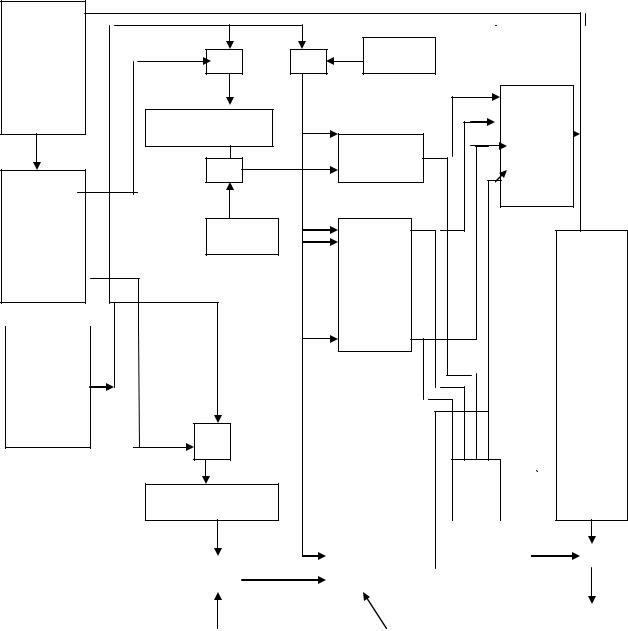

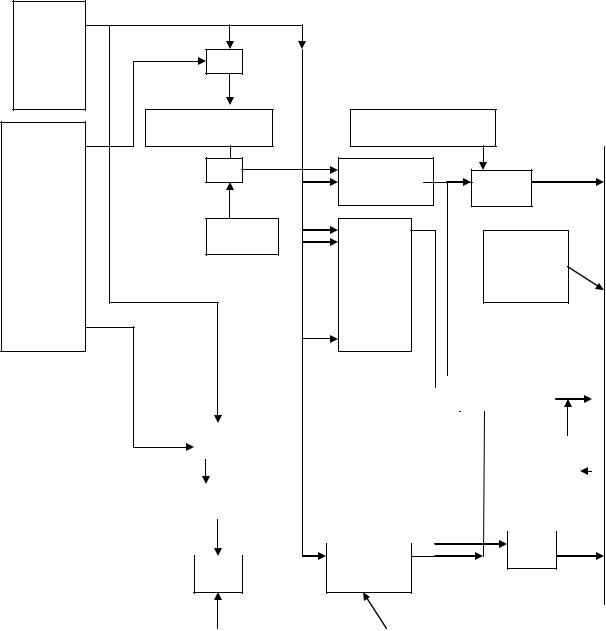

Полностью ассоциативная КЭШ.

Этот тип КЭШ в своей тэговой части содержит полный физический адрес требуемых данных, однозначно определяющий их место в системной памяти.

Поэтому в КЭШ такой архитектуры содержимое любой ячейки системной памяти может быть помещено в любую ячейку КЭШ.

Но с другой стороны схема поиска о наличии данных в таком КЭШ является сложной, так как требует одновременного анализа всех ячеек тэговой части.

Если для малого количества ячеек удается такую схему реализовать, то для большого объема это требует больших аппаратных издержек, то в конечном счѐте применение такой архитектуры является нецелесообразным.

БЛОК-СХЕМА

Как видно из блок схемы в режиме чтения текущий адрес данных подается на схемы сравнения, количество которых определяется количеством ячеек в КЭШ.

На другой вход схем сравнения поступают значения адресов (тэги записанные в каждую из ячеек теговой части в процессе записи в КЭШ).

Та схема сравнения, которая обнаружит совпадения

формирует сигнал, разрешающий выдачу данных из соответствующей ячейки накопительного блока.

Говоря о структуре содержимого ячеек теговой памяти, необходимо отметить, что данные в КЭШ используются не только для чтения но и для их изменения в процессе обработки в процессоре.

Возникает вопрос: «Что делать с такими данными?»

Записывать ли их в КЭШ обратно после обработки или отправлять в системную память, тогда что делать с исходной копией которая подверглась изменению и находтся в КЭШ.

Если эти изменѐнные данные являются промежуточным результатом и используются для дальнейших вычислений, то их можно записать в КЭШ и только получив конечный результат можно отправить в системную память.

Как долго измененные данные могут находится в КЭШ? Это время тоже является очень важным по той же причине, что в системе кроме процессора обычно присутствуют другие агенты, имеющие прямой доступ к памяти

(контроллер жѐсткого диска).

Даже эти вопросы обнажают проблемы, которые необходимо решать при вводе КЭШ в систему.

Отсюда вывод:

Для решения всех этих задач, которые связанны с так называемой когерентностью КЭШ и системной памяти, наличие только адреса данных в тэговой части НЕДОСТАТОЧНО. Необходима дополнительная информация отображающая состояние данных в системе (КЭШ) (биты достоверности).

.

Блок |

|

|

|

|

Форм |

|

|

|

|

Адреса |

И |

И |

чтение |

|

Записи |

|

|

||

|

|

|

|

|

В память |

|

|

|

Блок |

|

|

|

|

|

|

тег строки 0 |

|

|

Форм |

|

|

|

Адреса |

|

|

|

|

Схема |

|

|

|

|

При |

|

|

|

|

сравнеия |

|

|

И |

|

чтении |

|

ДШ |

|

|

||

|

|

|

|

|

Адреса |

|

|

|

|

Записи |

чтение |

|

Схемы |

|

В память |

|

Память |

||

|

|

сравне |

||

|

|

|

||

|

|

|

данных |

|

|

|

|

ния |

|

|

|

|

|

|

|

|

|

строк |

|

|

|

|

1- N-1 |

|

Шина |

|

|

|

|

Адреса |

|

|

|

|

Систем |

|

|

|

|

памяти |

|

|

|

|

|

И |

|

|

|

|

|

|

|

или |

|

Тег строки N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема |

|

|

|

|

|

|

|

и |

|

|

И |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

сравнени |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Регистр |

|

|

чтение |

|

|

В случае совпадения текущего |

данных |

|

|||||||||

|

|

|

|

|

||||||||||

|

|

|

|

адреса и тега при обращении к |

|

|

|

|||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

памяти в режиме чтения на одной |

|

|

|

|||||||

|

|

|

|

из схем сравнения будет лог1 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Адрес |

|

|

|

Строки |

|

|

|

Систем |

И |

|

|

ной |

|

|

|

|

|

|

|

памяти |

|

|

|

Схема |

тег строки 0 |

Данные строки 0 |

|

|

|

|

|

Выбора |

|

|

|

Адреса |

И |

Схема |

И |

Строки |

|

сравнения |

|

|

|

||

При |

|

|

|

записи |

чтение |

Схемы |

|

|

Шина |

||

|

|

сравне |

|

|

|

данных |

|

|

|

ния |

|

|

|

|

|

|

|

строк |

|

|

|

1- N-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

или |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Данные |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В кэш |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тег строки N |

|

Данные строки N |

|

|

|

|

||||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|

|

|

|

|

|

|

Схема |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

И сравнени

сравнени

чтение |

|

В случае совпадения текущего |

|

|

адреса и тега при обращении к |

|

||

|

|

памяти в режиме чтения на одной |

|

|

из схем сравнения будет лог1 |

|

|

|

. |

. |

Адрес, который |

|

процессор |

|

|

формируется в |

|

(регистровая память) |

|

|

|

|

|

|

|

формате команды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

КЭШ память |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

блок |

|

блок |

|

|

|

|

системная |

||

формирования |

|

формирования |

|

|

адреса операции |

|

адреса |

|

память |

|

|

команды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок преобразования логического адреса в реальный

Внешняя

Внешняя

память

ПДПпрямой доступ памяти

канал ввода\вывода

ЛЕКЦИЯ N7

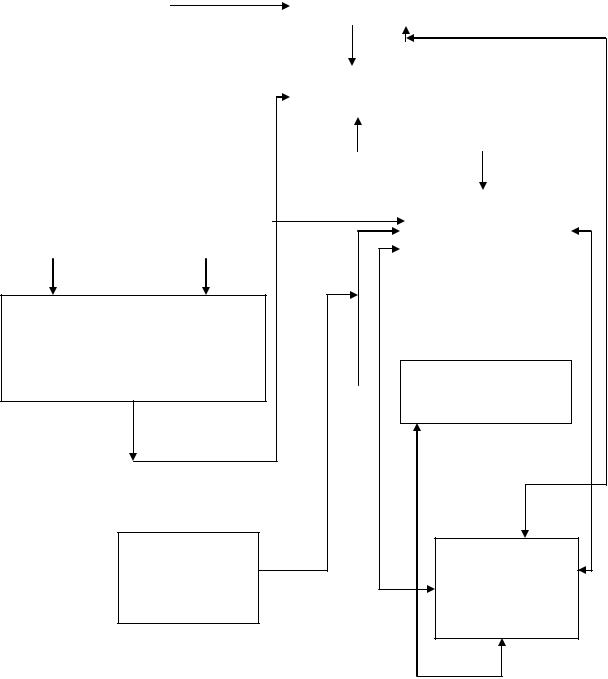

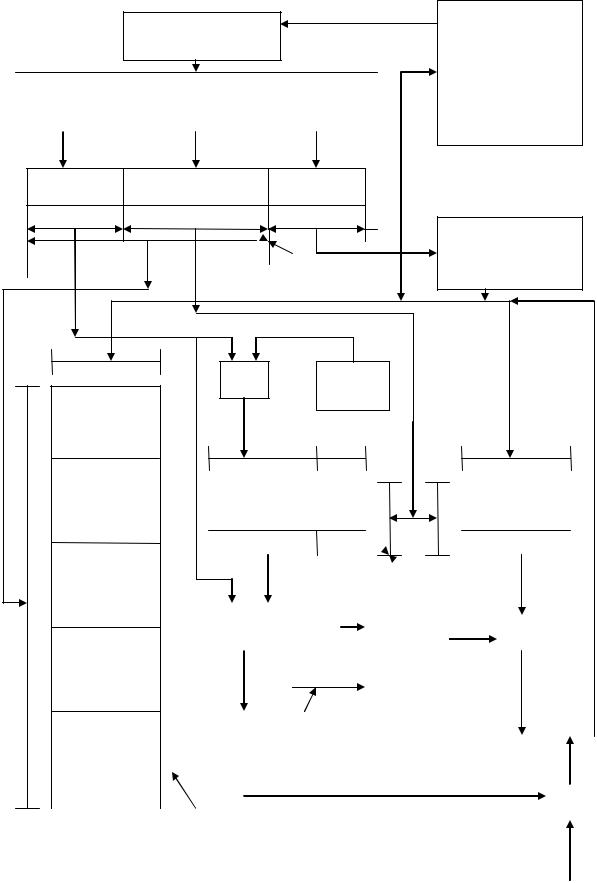

КЭШ-память прямого отображения.

В основу построения КЭШ прямого отображения положен следующий принцип:

Общее пространство оперативной памяти разбивается на равные блоки, размер которых равен размеру КЭШ памяти.

КЭШ память кроме накопительного блока имеет блок хранения тэгов, являющихся признаком наличия запрашиваемых данных в КЭШ.

Размер тэговой памяти равен размеру накопительного блока как в КЭШ полностью ассоциативный. В качестве тэга используется старшие разряды адреса памяти, которые по сути являются номером одного из блоков, на которые разбита основная память. Средняя часть адреса используется для адресации КЭШ и тэговой памяти и определяет адрес строки (страницы, слова) в КЭШ. Младшая часть адреса, не участвующая в выборке строки из кэш количеством своих разрядов определяет ширину выборки из памяти а своим значением смещение то есть место положение первого считываемого или записываемого байта в строке

При такой архитектуре в КЭШ прямого отображения на каждую строку в КЭШ будет претендовать количество строк из основной памяти равное

количеству блоков, на которое разбита основная память, т.е |

- где k- |

количество разрядов тэга. |

|

КРАТКОЕ ОПИСАНИЕ РАБОТЫ КЭШ ПРЯМОГО ОТОБРОЖЕНИЯ ПО БЛОК_СХЕМЕ

При обращении к памяти за данными процессор выставляет адрес на шину адреса .Как было сказано выше и видно из схемы разряды адреса разделены на три группы, о назначении которых мы уже говорили, и используются в соответствующих функциональных блоках кэш, а именно, старшая часть как данные или тег для теговой памяти, записываемые в нее при загрузке данных в кэш и считываемые из нее каждый раз в начале любого цикла обращения к системной памяти независимо от того будет это цикл записи или чтения.

Средняя часть , адресом теговой памяти и кэш подается напрямую на адресные входы памятей без каких либо сигналов управления . Младшая часть адреса ,как видно на блок – схеме определяет ширину выборки данных и для данной архитектуры

ширина шины данных основной памяти и кэш совпадают. В случае, если размер строки в кэш не совпадает и больше ширины выборки из основной памяти то он должен быть ей кратным целому числу чтобы обеспечить полноценный обмен между кэш и основной памятью.

Как только значение адреса фиксируетя на шине адреса с задержкой, определяемой логикой работы схемы сравнения и временем счиывания из теговой памяти формируется сигнал “miss”(промах) или “hit”(совпадение) и с учетом бита достоверности (V=1) определяется нахождение данных в кэш. Если данные в кэш, то соответствующий сигнал разрешает выдачу данных из кэш на шину данных. Если данные в кэш отсуствуют, то формируется запрос к системной памяти и данные считываются из нее в режиме чтения.

Если “ данные в кэш” формируется при записи ,то это значит что процессор брал данные из кэш изменил их и обязан записать их в кэш установив при этом бит V:=0 (грязный) в том случае ,если цикл записи в основную память будет произведен с задержкой(политика обратной записи). Если запись в основную память следует без задержки, то контроллер кэш оставляет бит V в единице,(политика прямой записи) таким образом отслеживая когерентность данных в основной памяти и кэш.

Адрес обращения к системной памяти

ПРОЦЕССОР

Номер блока в |

|

Номер строки |

|

Смещ. |

систем.памяти |

|

в кэш |

|

В строке |

|

|

|

|

|

К-разрядов м-разрядов |

р-разрядов |

разразрядов |

|

|

Шина данных |

|

Ширина шины L |

|

L=2*P |

И |

запись |

Блок 0 |

|

Блок1 |

Теговая память |

|

|

|

|

|

Кэш память |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Тег |

|

|

v |

|

|

|

|

|

|

|

|

|||||

Блок2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Схема |

|

|

|

|

|

Схема |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

И |

|

|

|

|||||

|

|

|

|

сравнения |

|

|

|

|

|

Формир |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

* |

|

|

|

|

|

|

|

|

|

|

|

|

Данные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

* |

|

|

|

|

|

|

|

|

|

|

|

|

в КЭШ |

|

|

|

|

|

|

|

* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

mis |

|

hit |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

si |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сист.память |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

N= 2*к |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|