ORGANIZATsIYa_EVM

.pdfзначений, поступающих на ДШX и ДШY, которые представляют части значения адреса.

Во втором случае используется один дешифратор то есть все биты значения адреса подают на него , который вырабатывает лишь один активный сигнал в каждом случае. Эти сигналы подаются по шинам в память, каждая шина активирует сразу несколько элементов ,подключенных к ней.

В зависимости от применения одного из способов или их совместного применения классифицируют различные структуры учитывая при этом еще и количество шин управления подводимых к элементам данных в памяти.

Исходя из выше сказанных замечаний рассмотрим различные физические структуры адресных запоминающих устройств.

Для того чтобы осуществить запись или чтение в адресные ЗУ к каждому элементу этого ЗУ хранящему минимальную информацию (бит) необходимо подавать управляющую информацию в виде адресных и информационных

(данных) сигналов в зависимости от количества физических линий,

используемых для этих целей и их использование для передачи логических значений сигналов различают структуры 2D,3D, 2.5D, 2DM.

Где D (dimension)- размер

А число - определяющее число линий адресных, и линий записи/считывания подводимы к каждому элементу памяти. Причем при подсчете линий записи и линий чтения принимают за 1. Структура 2D,3D, 2.5D

характерны были при использовании элементов на магнитные сердечники,

которые мы и рассмотрим.

Структура 2DM характерна для современных памятей, при организации матриц из элементов собираемых на базе транзисторов, в которых в качестве запоминающего элемента используется емкость изолированного стока,

выполняющая функцию конденсатора.

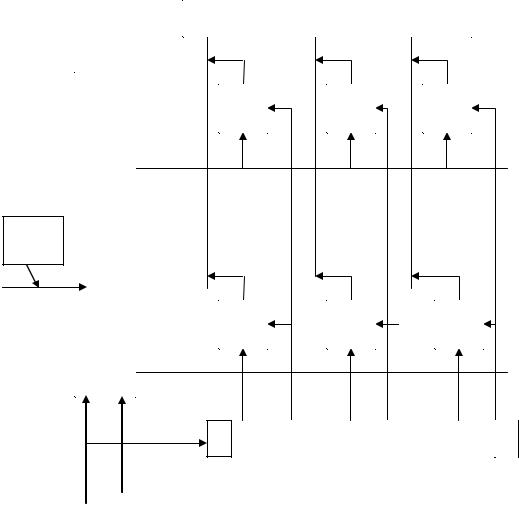

Структура 2D

Запоминающее устройство типа 2D имеет двух координатную выборку, причем только одна координата связана со значением адреса, который определяет адрес выбираемого слова, то есть структура построенная по второму способу. Вторая координата не связанная с шиной адреса используется для управления разрядом в слове при записи и считывании. Координата представляет две

гальванически развязанные шины шину записи и шину считывания, к которым подключены усилители записи и считывания соответственно.

Фсчитыв

Фзап1

|

|

Зап 1 |

|

|

|

|

|

|

|

|

|

|

|

Счит 1 |

Фзапис |

|

|

|

|

|

|

|

|

|

р |

1 |

Фзап1 |

||

|

|

|||

Фадр

Блок –схема памяти 2D

|

Усилитель считывания |

|

|

|

ЗЭ |

ЗЭ |

ЗЭ |

ША |

ДШХ |

|

|

|

ЗЭ |

ЗЭ |

ЗЭ |

|

|

Усилитель записи |

|

Запись Чтение

Врежиме записи и считывания в координатную обмотку подаются токи разного направления, причем ток осуществляющий считывание по величине в два раза больше и должен осуществлять перемагничивание сердечника (перевод его в нулевое состояние)

Вслучае единичного состояния сердечника при считывании в обмотке считывания наводится ЭДС величина тока которой определяет считывание единицы. Если сердечник находился в состоянии нуля, то ток в обмотке считывания отсутствует, так как отсутствует изменение магнитного потока, а ток помехи, возникающий от перемагничивания по частичному циклу усилителем чтения не воспринимается.

Ток записи должен быть по амплитуде равным 1/2

тока чтения и быть направлен в противоположном направлении и только в случае тока записи, подаваемого в обмотку записи разряда и имеющего то же направление, что и ток записи в адресной обмотке по сумме двух токов осуществляется перевод сердечника в состояние “1”.

В случае записи нуля ток в обмотке записи отсутствует, а величина тока записи в адресной обмотке не достаточна чтобы перевести сердечник в состояние „1‟.

Анализируя вышесказанное можно сделать следующий вывод:

Данная структура при использовании в качестве элемента памяти магнитный сердечник при каждом обращении независимо от вида операции (запись или чтение) реализует два смежных цикла ЧТЕНИЕ-ЗАПИСЬ, с той лишь разницей, что при чтении считанные данные возвращаются обратно в память, а при записи, в предварительно обнуленные ячейки в цикле чтения, новые данные управляют усилителями записи.

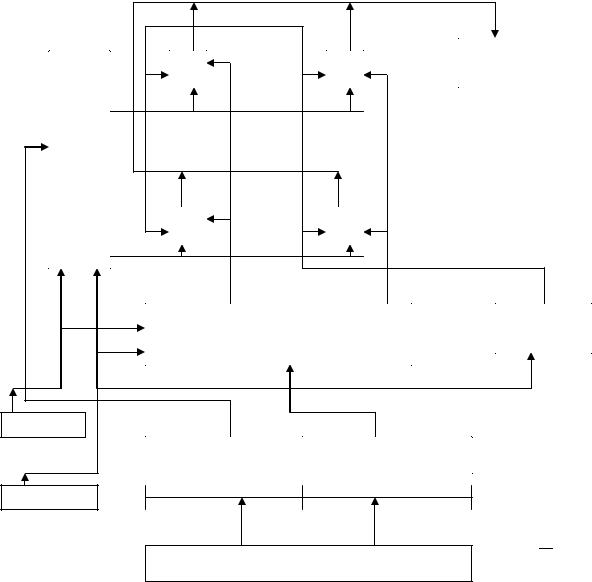

СТРУКТУРА 3D

В этой структуре реализован выбор элемента по первому описанному выше способу то есть для выбора элемента памяти имеются две адресные координаты X и Y и соответственно два дешифратора ДШХ И ДШY.

Структура 3D использовалась при организации памяти на магнитных сердечниках, хотя современные технологии уже позволили разработать подобные архитектуры на полупроводниковых элементах в одном кристалле.

Структура 3D представляет набор одноразрядных матриц, число которых определяет размер считанного слова, поэтому рассмотрим структуру такой матрицы.

зэ |

|

зэ |

Усилитель |

|

чтения |

||

pз |

|

|

|

|

|

|

|

ДШX |

|

|

|

зэ |

|

зэ |

|

|

|

|

Усилитель |

|

ДШY |

|

записи |

ЧТЕНИЕ |

|

|

|

N-1 |

R+1 |

R |

0 |

ЗАПИСЬ |

|

|

|

N РАЗРЯДНАЯ ШИНА АДРЕСА |

|

||

Как видно из блок-схемы обмотки считывания всех элементов соединены последовательно между собой и представляют прошивку, проходящую через все элементы разрядной матрицы.

Такая же топология и обмотки записи.

Считывание информации осуществляется только из одного элемента, находящегося на пересечении адресных координат,

активизированных дешифраторами.

Запись, как и в структуре 2D осуществляется подачей токов выборки в противоположном направлении относительно режима чтения. Ток подаваемый в обмотку разрядной записи в отличии от структуры 2D выполняет компенсационную функцию и имеет противоположное направление токам выборки в случае записи 0 в элемент, таким образом блокируя перемагничивание сердечника в состояние 1.В случае записи 1 ток в обмотке записи отсутствует и элемент переходит в единичное состояние.

Структура 2.5D

Структура 2,5D определяется по режиму работы (участию) координатных обмоток и обмоток управления в режимах записи и считывания, потому что в режиме записи функционирует подобно структуре 2D , а в режиме чтения как 3D, то есть при записи участвуют только две обмотки одна адресная X и другая разрядноадресная ,а при чтении трипри чем разрядно-адресная выполняет функцию координатной и совместно с другой адресной обмоткойX и обмоткой считывания реализует режим считывания как в 3D.

По количеству линий управления 2,5D имеет столько же сколько и 2D с той лишь разницей что линия управления записью ,взяв на себя функцию координатной обмотки в режиме чтения а режиме записи функцию записи 1 или 0 определила структуру матрицы для хранения одного разряда из массива слов , хранящихся в памяти подобно 3D, а никак в 2D,в которой хранится все слова массива.

То есть для организации массива памяти n-разрядных слов необходимо объединение нескольких матриц для их хранения и наличие n ДШY и один ДШX ,где каждый дешифратор ДШY в режиме записи управляет своим разрядом одновременно, выполняя и координатную функцию, а при чтении все дешифраторы работают в одном режиме , обеспечивая считывание всех разрядов слова.

зэ |

зэ |

ДШХ

зэ |

|

зэ |

|

|

|

Разрядно-адресный форм. ДШY

Усилитель

считывани

Вх..инф.

|

|

|

|

|

|

|

|

|

запись |

|

N-1 R+1 |

R |

0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ШИНА АДРЕСА

чтение

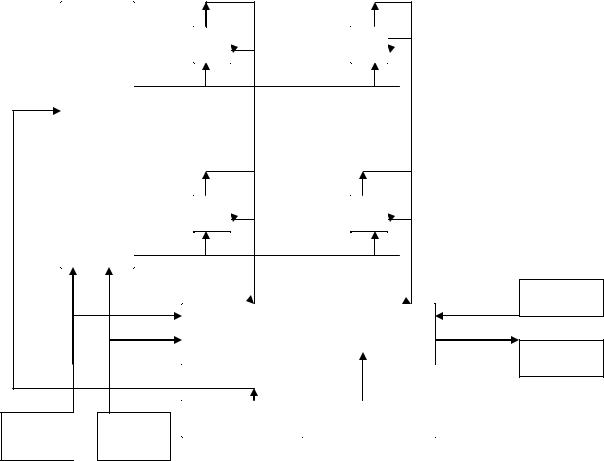

Структура 2DM

Структура 2DM стала представлять дальнейшую модификацию уже существовавших ранее структур 2D и 2,5D.

От архитектуры 2D в 2DM использована возможность одновременной активизации n элементов (слова, страницы); от 2,5D

взята возможность управления поразрядного считывания и записи из матрицы, другими словами говоря в матрице 2DM стали размещать элементы не одного разряда а нескольких как в 2D при чем объединив гальванически три шины в одну ,а именно, координатную Y, разрядной записи и разрядной шины считывания

благодаря использованию в качестве запоминающего элемента транзистора с изолированным стоком, используемого в качестве обкладки накопительного конденсатора. Отметим еще раз что структура 2D на магнитных элементах ,функционирующих на принципе закона электромагнитной индукции такого объединения не допускает.

|

|

зэ |

зэ |

|

ДШХ |

|

|

|

|

зэ |

зэ |

|

|

|

Инф.вх. |

|

|

Разрядный коммутатор ДШY |

|

|

|

|

Инф.вых |

запись |

чтение |

Адрес строки |

Адрес колонки |

|

|

||

Выбор той или иной физической структуры, рассмотренные нами выше, является только частью этапа проектирования памяти. Структура определяет только топологию накопительного блока памяти , число адресных и управляющих шин подводимых к каждому элементу для хранения данных, но не определяет временных параметров и соотношений сигналов, поступающих по этим шинам к элементам. Для того чтобы устанавливать эти параметры(длительность сигналов и и их задержки относительно друг друга) необходимо знать физические процессы, происходящие в накопительном блоке при считывании и записи данных . Проектирование временных диаграмм, определение вида и числа сигналов ,управляющих работой накопительного блока это и есть разработка протокола связи (интерфейса) памяти с вычислительной системой (процессором). Протокол реализуется блоком управления памятью. Конструктивно блок управления памятью может находиться как в составе процессора, так и на системной плате внедренным в системный чипсет, а может находиться и в самой микросхеме (внутренний контроллер). Поэтому прежде чем рассматривать организацию современных памятей с повышенным быстродействием рассмотрим основные моменты работы DRAM и процессы происходящие в ней при считывании и записи данных.

Линия записи/ считывания

Функциональная схема элемента 2DM на базе полупроводникового

прибора

исток |

|

|

сток |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Емкость между стоком |

|

|

|

затвор |

|

|

|||

|

|

|

|

|

|

и схемной землей |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Линия выборки