ORGANIZATsIYa_EVM

.pdf

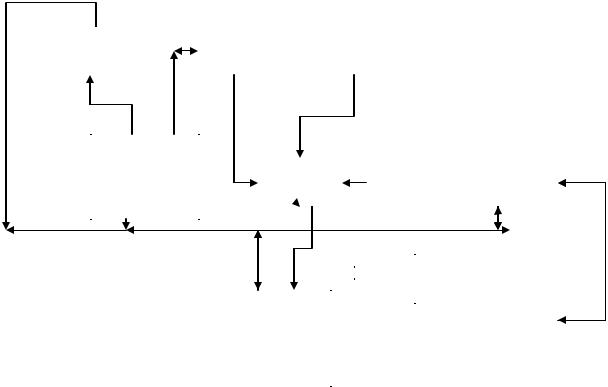

Блок-схема архитектуры Фон-Неймана.

АЛУ |

|

Блок форм |

|

адр пульта |

|

|

Адр опер |

|

|

|

|

|

|

|

|

Блок |

|

|

|

|

|

|

|

|

|

|

|

|

управления |

|

|

асемблер |

|

|

форм адр |

|

Регистр |

|||||

Регистр |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

след ком |

|

связи |

||||

команды |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шинаШина |

|

|

|

|

|

Шина |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

адреса |

|

|

|

|

||

|

команд |

|

Общая |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

данных |

|

|

|

|

|

|

|

Внеш устр |

||||

|

|

память |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

уструстрост |

||||

|

|

|

команд и |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

данных |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Комментарий к блок-схеме архитектуры Фон-Неймана Наличие жестко заданного набора исполняющих команд и программ было

характерно для первых компьютеров, которые конструировались, как теперь принято называть, по Гарвардской архитектуре.

Отличие архитектуры Фон-Неймана заключается в принципиальной возможности работы над управляющей программой точно так же, как и над данными. И для этого необходимо, чтобы программа и данные находились в одной физической памяти или , по-другому, был реализован принцип совместного хранения программ и данных в памяти ЭВМ. Эта особенность архитектуры позволяет наиболее гибко управлять работой вычислительной системы, но имеет недостаток – возможность искажения управляющей программы, что понижает надежность работы системы. Для уменьшения этого используются в данной архитектуре различные механизмы защиты областей памяти.

Как видно из блок-схемы, процессор связан шинами адреса,

команд/данных. Для разделения потока команд и данных внутри процессора используются (в зависимости от архитектуры) как аппаратные, так и микропрограммные средства, реализующие специальные циклы (такты) работы процессора, фиксирующие запросы в оперативную память за командой или данными.

Модернизация архитектуры Фон-Неймана и Гарвардская архитектура

Эти два направления определяют архитектуру вычислительных машин, до сих пор во многих случаях дополняя друг друга при их совместном использовании в рамках одной вычислительной системы или порознь в зависимости от решаемых задач.

Сама идеология модели Фон-Неймана, как было сказано выше, состоит в последовательном выполнении команд программы в процессоре, когда следующая команда поступает на исполнение после завершения предыдущей.

Эта концепция удовлетворяла требованиям до тех пор, пока не потребовались вычислительные системы с производительностью, которую данная архитектура уже не смогла обеспечить. Поэтому модель Фон-Неймана стала подвергаться ревизии на всех этапах выполнения команд.

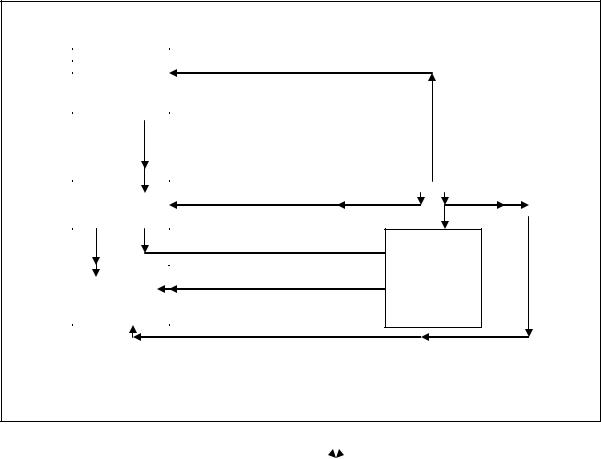

Первоначальной модернизации стал подвергаться этап чтения из выборки команды из процессора путем внедрения дополнительных буферных регистров для последующих команд, а затем и ввода дополнительной памяти для их хранения (БПК, КЭШ команд).

Таким образом, это позволило ускорить выполнение команд в процессоре за счет сокращения числа циклов обращения к оперативной памяти за командами, так как процессор мог уже выбирать не очередную команду,а

порцию очередных команд а блок управления передав очередную команду на выполнение в АЛУ смог продвигать следующую команду к декодерам из буферных регистров уже не обращаясь в оперативную память . Частота обращения за командами в память сократилась с вводом буферной памяти команд и выборка (передача команд из основной памяти) стала производиться только при отсуствии очередной команды в КЭШ или в свободное время когда процессор не обращается к памяти.

С внедрением БПК (КЭШ команд) шина данных и шина команд были разделены внутри процессора. А это уже было частичным внедрением Гарвардской архитектуры, несмотря на то что команды и данные хранились в общей памяти,такая архитектура была в ЕС ЭВМ ряд II.

Общая |

|

|

память |

|

|

команд и |

|

|

данных |

|

Блок |

|

|

|

|

|

управлени |

|

||

|

|

я |

|

|

|

демультип |

|

|

лексор |

|

|

|

|

|

|

Блок |

|

|

памяти |

|

Опер.устр |

||

команд |

||

ор |

|

|

|

|

В дальнейшем уже в архитектуре ПК (Intel) была введена КЭШ данных, и

это уже была модель Гарвардской архитектуры в процессоре. А общая память в вычислительной системе работала по принципу Фон-Неймана, поставляя и принимая команды и данные в процессор по общей шине.

С развитием технологии преобразования аналоговых сигналов в цифровой вид для их обработки в процессоре, гарвардская архитектура завоевала прочные позиции.

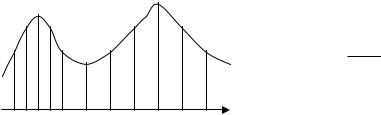

Согласно теории аналоговый сигнал можно идентифицировать с достаточной точностью, если стробировать, его с Т=1/2F, где F - .. частота спектра, передаваемого сигнала.

T 1 ,

2F

т.е. время на обработку квантованных значений входящего сигнала ограничено. И в этом случае принцип Гарвардской архитектуры, как мы убедимся далее, позволяет ускорить обработку таких сигналов.

Как видно из блок-схемы, процессор связан шинами адреса,

команд/данных. Для разделения потока команд и данных внутри процессора используются (в зависимости от архитектуры) как аппаратные, так и микропрограммные средства, реализующие специальные циклы (такты) работы процессора, фиксирующие запросы в оперативную память за командой или данными.

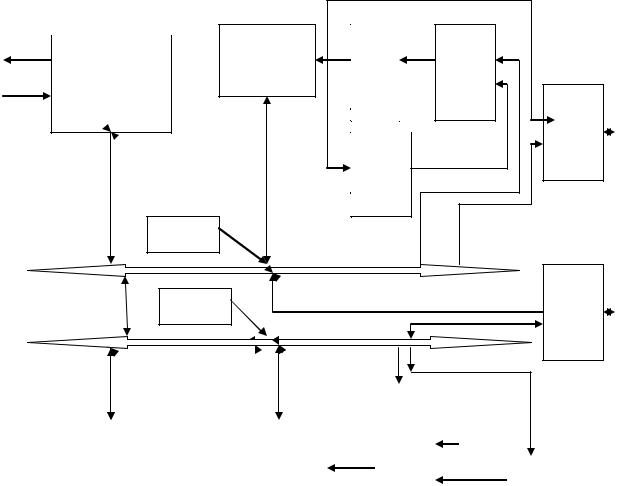

БЛОК-СХЕМА ГАРВАДСКОЙ АРХИТЕКТУРЫ ЭВМ

Блок

управления

|

Регистр |

|

Блок формиров |

|

|

Блок формир |

|

Операционное |

|

|||||||||

|

команд |

|

Адр команд |

|

|

адреса данных |

|

устройство |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Ш К |

|

|

|

|

|

Ш А |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

Ш Д |

||||||||||

|

|

|

Память команд |

|

|

|

|

|

|

Память данных |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Память |

СЧ |

муль |

|

Устройство |

||||

команд |

Адр |

типле |

||

управления |

||||

|

ком |

ксор |

||

|

|

муль

типле

сор

стек

Ш К

муьт

Ш Д ипле ксор

|

|

|

|

|

|

|

|

|

Операционн |

|

Память |

|

Муль |

|

|

|

|

ое |

|

данных |

|

типле |

|

|

|

|

|

|

|

|

регистры |

||||

устройство |

|

|

|

ксор |

|

|

||

|

|

|

|

адрес |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Комментарий к блок-схеме гарвардская архитектура ЭВМ.

В гарвардской архитектуре существует две физически раздельные памяти:

1)память команд

2)память данных

В первом компьютере Эйкена данные считывались с перфоленты а для хранения программы использовались регистры в которые предварительно команды записывались с пульта оператора. Это позволяло одновременно подавать на обработку данные и коды операций над ними в исполнительное устройство.

Как видно из блок-схемы команды считываются из памяти команд в регистр команды процессора ,в котором кодовая часть операции активизирует блок управления , задающий алгоритм работы операционного устройства .

Адресная часть команды в зависимости от вида команды используется для формирования адреса следующей команды или для адресации операндов в памяти данных или того и другого. То есть подобно, как и в фон-неймановской архитектуре. Отличие в том ,что в данной схеме отсутствует ассемблер адреса

,а две отдельные шины адреса для команд и данных направляются к своим памятям.

Операционное устройство получив “приказ” из устройства управления в автономном цикле может производить операции над данными, а командный блок может в это время организовать подготовку к выполнению следующей .

Другими словами говоря данную архитектуру можно рассматривать как двух ступенчатый конвейер.

Недостаток данной схемы –две адресные шины. На практике для сокращения числа шин адреса команд и данных передают по соответствующим шинам используя мультиплексирование.(см. рис.2)

Как видно из блок-схемы для того чтобы осуществлять управление операционным устройством и передавать адресную часть команд в память данных используют для связь между шиной команд и данных. Связь эту также

используют для передачи констант из памяти в операционное устройство,

используемые как операнды.

Данная архитектура используется в микропроцессорах предназначенных для цифровой обработки аналоговых сигналов.

Рассмотрим кратко назначение узлов на блок-схеме.

Счетчик команд представляет автоинкрементный счетчик с параллельной загрузкой либо из стека либо с шины команд. Автоинкремент используется на линейном участке программы. Загрузка счетчика команд с младших разрядов шины команд осуществляется при условных и безусловных переходах.

Стек используется для возврата из подпрограмм.

В данной архитектуре имеется две возможности адресовать ячейки памяти данных . При первом способе адрес указывается в команде а при втором (

косвенная адресация ) адрес берется из регистра предварительно загруженного значением адреса обращения к памяти. Имеется возможность производить инкрементацию или декрементацию (увеличение или уменьшение на единицу)

значения этих регистров, что позволяет их использовать для организации циклических участков программы. Кроме того эти регистры могут использоваться для хранения данных считанных из памяти.

RISC и CISC

По виду используемых команд процессоры делятся на :

А) с CISC архитектурой, (с полным набором команд, выполняемых по сложным алгоритмам);

Б) с RISC архитектурой (с командами, выполняемыми за 1-2 такта процессора)

Появление процессоров с набором CISC команд явилось следствием модернизации формата команд в процессорах с архитектурой Фон-Неймана.

Как известно, первоначальный формат команды состоял из кода операции и адресной части, указывающей расположение операнда в оперативной памяти.

Целью модификации было упрощение алгоритма программы, то есть расширение функциональных возможностей команды, код которой мог бы на уровне аппаратных средств реализовать не только функции обработки операндов, но и их чтение из оперативной памяти, и обратно запись результата.

Такая структура удовлетворяла требованиям до внедрения конвейерной обработки команд в процессоре.

С внедрением конвейерной обработки операндов стало ясно, что для производительной работы конвейера необходимо исходные данные держать в регистрах самого процессора, а не извлекать из оперативной памяти, так как последнее явилось причиной простоя конвейера из-за необходимости ожидания доставки данных из оперативной памяти по запросу процессора.

Если в нескольких словах идея RISC архитектуры состояла в том, что в процессоре имеется достаточно большой регистровый файл, ячейки которого проходят непосредственное обращение из команд и результат записывается обратно в регистровый файл. Записи из регистрового файла в оперативную память и обратно cтали осуществляется командам, которые не связаны с обработкой данных в процессоре. Т.е. команды осуществляющиеся в CISC

архитектуре обращение к памяти за операндами выполняющие операции над ними разделили на 2группы команд( команды класса RR и команды класса

LOAD и STORE выполняющих запись данных из оперативной памяти в регистровый файл и запись из регистрового файла а в память ).

Так все арифметические операции в RISC архитектуре используют только