ORGANIZATsIYa_EVM

.pdfрегистровый формат RR, а команды MOV (пересылки) осуществляют перемещение только из регистра в регистр или обмен между группами регистров.

Если в CISC архитектуре существуют команды, которые кроме операций на сумматоре активизируют работу сдвигателя, осуществляя сдвиг операции,

то в RISC архитектуре таких команд нет, а есть отдельные команды арифметики и сдвига. Как сказано выше связь процессора с оперативной памятью в RISC архитектуре осуществляется посредством команд LOAD или

STORE, выполняющих загрузку и выгрузку регистровых файлов из/в

процессор.

С вводом механизмов базирования и индексирования, а далее механизма динамического преобразования адресов обращения к памяти, время выборки данных увеличилось, но в целом архитектура ЭВМ выиграла в производительности, во-первых, за счет того, что выше указанные механизмы явились основными элементами организации многопрограммного режима ЭВМ, а во-вторых, из-за того, что программный код (последовательность команд) на линейном участке выполняется в пределах страницы и сегмента.

Необходимости производить полный цикл преобразования адреса из логического в физический, каждый раз нет а делать это только при изменении значения страницы или сегмента, если параметры преобразования текущей страницы и сегмента сохранять в регистрах процессора или в специальных буферных памятях, т.е. «опускать» этапы преобразования адресов, используя их.

Другим средством для ускорения вычислительного процесса было введение регистровой памяти. Это направление, в конечном счете привело к созданию RISC архитектуры процессора.

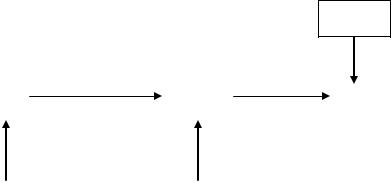

CISC архитектура

1.Большой набор команд.

2.Команды достаточно сложны, со сложной структурной адресацией

операндов, зачастую имеют нефиксированный формат от 1 до 16 байт.

3. Имеют действия с операндами, находящимися как в общих

(программных) регистрах процессора, так и в формате команды или оперативной памяти, адреса которых формируются на основании кодировки,

указанной в самой команде (байт-модификатор)

4. Выполняются в зависимости от формата от нескольких единиц до десятков и сотен тактов процессора.

|

|

|

|

|

БУ |

|

Формат RR, RX, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

команда содержит адрес ОП |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и адрес регистра |

ОП |

|

РФ |

|

|

ОУ |

||

|

|

|

|

||||

|

|

|

|

|

|

|

|

БУ – блок управления РФ – регистровый файл ОУ – оперативное устройство ОП – оперативная память

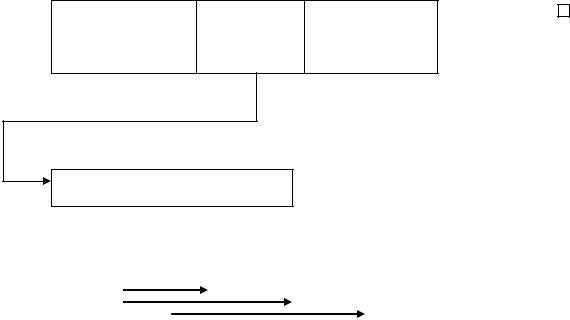

RISC архитектура

1.Команды простые, выполняются за 1, 2 тактов компьютера.

2.Формат фиксирован, что упрощает управление потоком команд в процессоре.

3.Процессорное ядро содержит регистровый файл, формат команд RR.

4.Для доставки данных из памяти и записи результата в память используются команды LOADи STORE.

БУ

(1) формат RR

(3) |

|

|

|

|

(2) формат STORE |

||

|

|

|

|

|

|

(3) формат LOAD |

|

ОП |

|

РФ |

|

ОУ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2) |

(1) |

СТРУКТУРЫ И ФОРМАТЫ КОМАНД И ДАННЫХ В ПРОЦЕССОРЕ.

Одним из важных факторов, учитываемых при проектировании и выборе архитектуры процессора, является определение набора команд, видов обрабатываемых данных их форматы и структура.

Именно вышеперечисленные исходные параметры определяют микроархитектуру процессора.

Команда-это своего рода информационный блок или двоичный код в котором кодируется выполняемая операция над данными , их местонахождение в вычислительной системе и где будет сохранен результат операции. Следовательно команды, их двоичный код являются конечным результатом преобразований всех уровней в иерархической вычислительной системе, стоящими выше уровня микроархитектуры процессора.

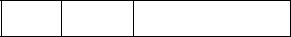

По характеру выполняемых операций различают следующие основные группы команд

Классификация команд по виду выполняемых операций

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Арифметические |

|

|

|

Логические |

|

|

|

Передачи |

|

Команды |

||||||

с фиксированной |

|

|

|

операции |

|

|

|

управления |

|

ввода |

||||||

и плавающей |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вывода |

|

точкой |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Команды |

|

|

|

Команды |

|

|

|

||||||||

|

передачи кодов |

|

управления |

|

|

|

||||||||||

|

(пересылки |

|

режимом работы |

|

|

|

||||||||||

|

данных |

|

|

|

процессора |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Исходя из определения команды, код ее должен в общем случае состоять из двух частей : операционной и адресной для которых в формате команды отводят группы разрядов(поля). Если операционная часть во многих случаях определяется одним полем, то адресная часть состоит из нескольких полей.

Наличие нескольких полей в адресной части дает возможность кодировать одно, двух и трех адресные команды и различные способы адресации с использованием механизмов базирования и индексирования.

Когда говорят о формате команды, то имеют в виду ее структуру то есть разметку с указанием номеров разрядов, определяющих границы отдельных полей,с указанием числа разрядов(бит) в каждом поле. Форматы команд могут быть постоянной или переменной длины в рамках одной системы команд.

При использовании команд переменной длины в структуру команд закладывают код длины команды для которого используют или отдельные биты или косвенное кодирование указывая длину ,например, значением разрядов кода операции.

И так код поля операции и количество разрядов в поле определяет множество выполняемых команд в системе.

Адресная часть, указывающая адрес операнда содержит в общем случае не абсолютный физический адрес памяти, как это было в первой фон-

неймановской модели, а так называемое смещение относительно некоторого физического (логического при использовании динамического преобразования адреса) адреса в оперативной памяти так как в противном случае при большом объеме памяти для указания абсолютного адреса пришлось бы использовать слишком длинные адресные поля.

С другой стороны выбирая длину команд необходимо учитывать чтобы длины команд были в согласовании с элементами данных выбираемых из памяти для обработки и равны байту, полуслову, слову, и так далее с целью упрощения аппаратной логики выборки информации из памяти.

Что же касается наличия числа адресных полей в формате команд, то наиболее простым вариантом было бы использование четырех полей:

Два поля для источников операндов Поле для хранения результата операции

Поле для указания адреса следующей команды в программе То есть использовать принудительный порядок выборки команд.

Такая технология на уровне программного кода не используется а используется в микропрограммах, для которых характерны алгоритмы с детерминированными связями между операторами.

Использование трех адресных команд было характерно для первых ЭВМ команды которых имели вид:

ОП[A3] : =ОП[A2] *ОП[A1]

Операция производится над содержимым ячеек с адресами A1 и A 2

Результат записывается в память по адресу A3.

Формирование адреса следующей команды в системах с трех адресной организацией на линейном участке программы происходит автоматически увеличиваясь на длину выполненной команды, а командах управления кодируется обычно в одном из адресных полей.

Для сокращения длины команды используют двух адресный формат ОП[A1] : = ОП[A1]* ОП[A2]

Применение одноадресного формата команды, в которой указывается адрес одного операнда целесообразно использовать для обработки данных с размещением по последовательным адресам в памяти для которой оператор имеет следующий вид:

АККУМ : = АККУМ*ОП[A1]

То есть в процессе обработки данные считываются из памяти,

обрабатываются в процессоре и результат обработки используется в последующем цикле, как второй операнд при этом формат команды указывает на адрес начала массива и содержит код длины массива.

Определив формат команды далее необходимо разработать технологию формирования адреса обращения к данным или по другому способы адресации в командах. Поэтому выбор способов адресации, формирование исполнительного адреса и преобразование адресов является одним из важных вопросов при разработке и выборе архитектуры процессора.

Разнообразие способов адресации усложняет аппаратную логику блока формирования адреса с одной стороны, а с другой расширяет функциональные возможности команд и соответственно дает возможность более гибкого управления вычислительным процессом.

Так что при разработке архитектуры процессора необходимо учитывать этот фактор, фактор который в свое время стал одним из определяющих в направлениях развития CISC и RISC архитектур процессоров.

Способы адресации. 1. Непосредственная.

КОП R1 CONSTANTA

Операнд размещается в формате команды

R1: = [R1]* const.

2. Прямая.

Аисп = [A] где [A]-содержимое поля адресной части команды.

Использовалась в первых ЭВМ. Может быть реализована как частный случай относительной адресации, если базирование не используется.

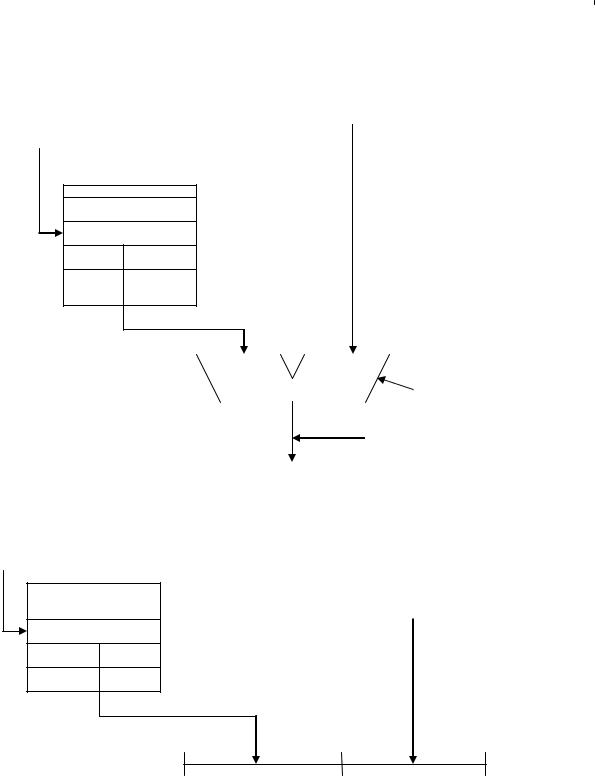

3. Относительная адресация

Aисп = Aбазы + Aсмещ

Абазы – адрес значение которого может находится в одном из общих или специально выделенных регистрах для хранения значения базового адреса , при

нулевом значении содержимого базового регистра относительная адресация

трансформируется в прямую.

Варианты относительной адресации

|

|

|

|

|

B |

D |

|

|

|

|

|

|

|

|

|

Базовый адрес

Некоторые |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

архитектуры |

|

|

|

|

|

|

|

сумматор |

|

реализуют вариант по |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

следующему |

|

|

|

|

|

|

|

|

|

алгоритму |

|

|

|

|

|

|

|

|

|

|

|

|

|

Aисп |

|

||||

В/=0 Аисп=[B]+D |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

B=0 Аисп=D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

B |

D |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Базовый адрес

Индексная адресация.

Реализуется также как относительная, с той лишь разницей, что в индексной ячейке хранится не базовый адрес а индекс(смещение) величина которого используется для модификации адреса данных(увеличения или уменьшения в зависимости от режима индексирования) при выполнении команды.

Данный режим используется при обработке массива данных при организации циклических вычислений.

Поле адреса Регистра индекса

смещение

смещение

смещение

А |

А+m |

A+2m |

|

|

|

|

|

|

|

|

|

|

|

|

|

Косвенная адресация.

Адрес операнда указывается косвенно через указатель, который находится в формате команды. В случае использования регистра в качестве указателя адреса содержимое этого регистра и будет адресом операнда в памяти. Такая форма косвенной адресации носит название косвенной регистровой, может быть использован и другой режим когда указателем адреса операнда может служить ячейка оперативной памяти.

Форматы данных.

В ЭВМ применятся две формы представления чисел с фиксированной и

плавающей точкой .При представлении чисел с фиксированной точкой диапазон представления чисел зависит от расположения точки в разрядной сетке числа. Если точка располагается слева от старшего разряда, диапазон

чисел определится |

2*-(n-1) <v=[х] <v=1-2*-(n-1) |

|

В случае расположения фиксированной точки справа от младшего разряда |

||

диапазон |

-2*n-1 <v=х<v=2*n-1 -1 |

|

Где n –количество разрядов числа.

Представление чисел с плавающей точкой в общем случае имеет вид

Х=S*p х q

S*p- характеристика числа q-мантисса ,дробное число.

p-порядок числа, может быть как положительным так и отрицательным

числом.

Для упрощения операций над порядками вводят так называемый

смещенный порядок pсмещ=p+A A=2*k где к -число разрядов порядка

То есть pсмещ является положительным числом

Для отображения числа с плавающей точкой разрядная сетка делится на два поля:

Поле порядка Поле мантиссы

Знак числа указывается в крайнем левом разряде разрядной сетки числа Для повышения точности вычислений используют нормализацию

основанную на том, что при фиксированном числе разрядов мантиссы любая величина в машине представляется с наибольшей точностью нормализованным числом, оно считается нормализованным, если мантисса будет выражаться значением

1/s <v=q<1

В случае двоичного представления чисел это означает: ½<v=q<1.