ORGANIZATsIYa_EVM

.pdf

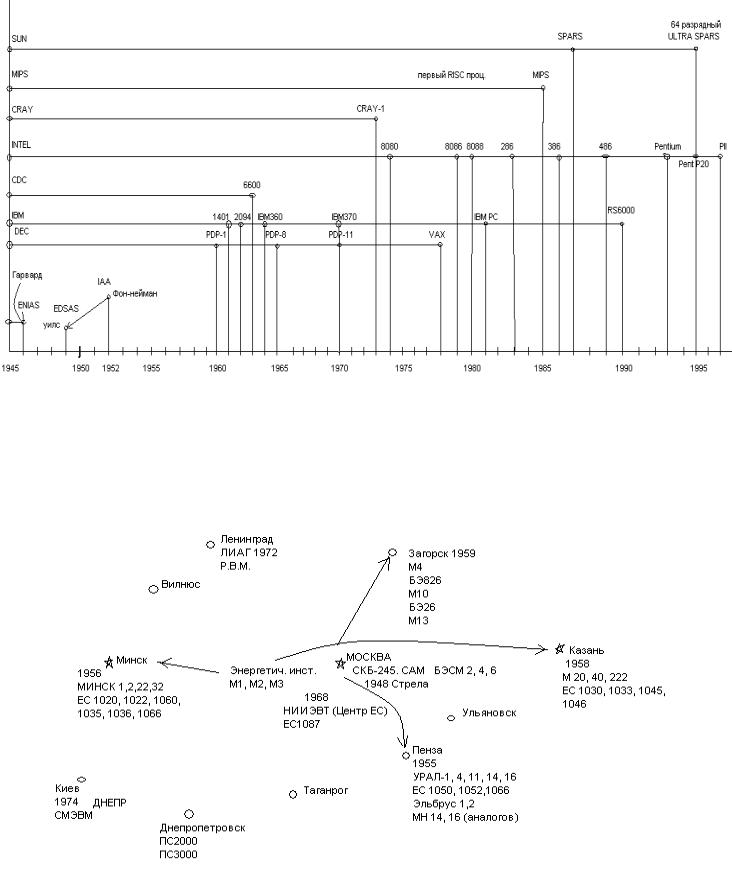

Многоуровневая организация компьютера.

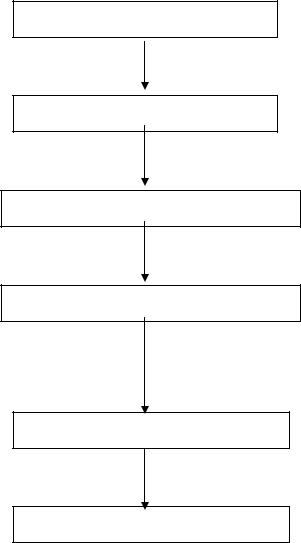

Ур. 5

Ур. 4

Ур. 3

Ур. 2

Ур. 1

Ур. 0

Язык высокого уровня

трансляция (компилятор)

Уровень языка ассемблера

трансляция (ассемблер)

Уровень операционной системы

трансляция (ассемблер)

Уровень архитектуры команд

интерпретация (микропрограмма)

или непосредственное выполнение

Микроархитектурный уровень

аппаратное обеспечение

Цифровой логический уровень

Компьютер проектируется как иерархическая структура уровней, каждый из которых надстраивается над предыдущим. Каждый уровень представляет собой определѐнную совокупность объектов и операций над ними. Набор типов данных, операций и особенностей каждого уровня называется архитектурой.

Совокупность архитектур каждого уровня и составляет архитектуру вычислительной системы, или по-другому «организацию».

ЦЛУ является низшим уровень в многоуровневой организации вычислительных систем.

Задачей этого уровня является разработка и проектирование логических элементов, выполняющих элементарные логические операции и – не, и – или – не, на базе физических элементов: транзисторов, диодов, конденсаторов и т.д.

Элементарным элементом для построения более сложных структур (триггеров, дешифраторов, сумматоров, сдвигателей), которые являются основными узлами для построения сложных структур ЭВМ, является элемент «и – не». Этот элемент построен на базе диодно-транзисторной логики ДТЛ или транзисторнотранзисторной логики ТТЛ.

ВЭВМ 1-го поколения на электронных лампах в качестве инвертирующего элемента использовались триоды, которые в ЭВМ 2-го поколения были заменены транзисторами.

Всовременных ЭВМ используются БиС и СБиС. Но в основе их по-прежнему используются «классический вентель» и – не, на базе которых и проектируются вышеуказанные структуры.

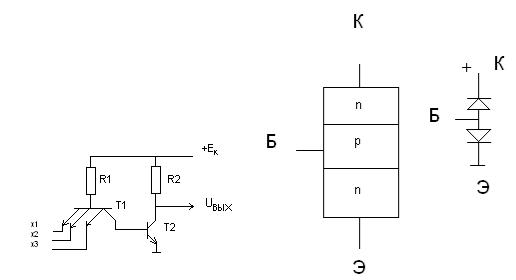

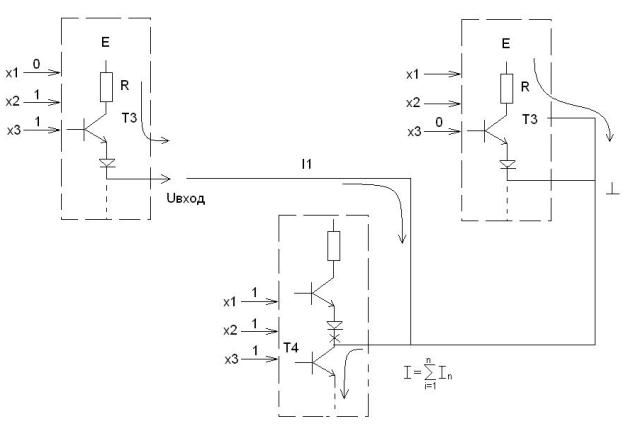

Для понимания работы ЭВМ на цифровом логическом уровне рассмотрим в общих чертах работу элемента и – не в структуре ТТЛ:

В качестве логической сборки, выполняющей функции «и» используется многоэмиттерный транзистор Т1. Функцию инвертирования выполняет Т2. Данный элемент собран на транзисторах типа n-p-n.

Основное структурное отличие многоэмитерного транзистора (МЭТ) от обычного заключается в том, что он имеет несколько эмиттеров, расположенных таким образом, что прямое взаимодействие между ними исключается, что и позволяет реализовать функцию «и».

Рассмотрим работу схемы.

Как видно из схемы переход базы – эмиттер работает в режиме прямого смещения, а переход базы - коллектор в обратном.

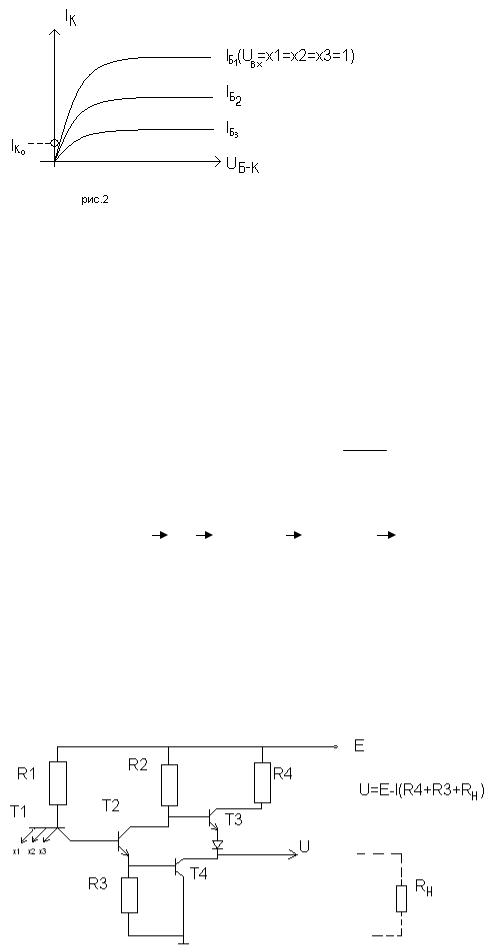

Вольт-амперная характеристика для коллектора.

Токи для данного включения имеют следующий вид.

При подаче хотя бы на один из ходов Х1, Х2, Х3 сигнала низкого уровня будет открыт один из переходов Б-Э в многоэмиттерном транзисторе. Из-за малой величины сопротивления RБ-Э. В прямом направлении UБ ≡ 0,8.

Основной ток будет стекать во входящую схему через переход Б-Э в многоэмиттерном транзисторе. Ток, втекающий в базу Т2 практически отсутствует, т.к. напряжения у Б = 0,8 будет не достаточным, чтобы открыть переход Б-К - Т2, и значение его будет IКО – равное обратному току коллектора в закрытом режиме,

вследствие чего потенциал на базе Т2 у Б=IБ * RБ-Эпрям. ≡ 0 и Т2 будет закрыт (см. также вольтамперную характеристику (рис. 2).

Так как транзистор Т2 закрыт, то напряжение выходное

Uвых = ЕК – IК ×RК

Ввод IК ≡ 0, будет иметь значение высокого уровня близкого к источнику питания, т.е. данный режим будет реализован как у=Х1 Х2 Х3

В случае всех единичных уровней на входе |

|

|

Х1 = Х2 = Х3 = 1 |

|

|

Элитерные переходы Т1 |

будут закрыты, вследствие чего потенциал базы в Т1 то |

|

организует цепь тока ЕК R1 |

RБ-КпрямТ1 RБ-ЭпрямТ2 |

0 |

Увеличение тока базы в Т2 (см. в амперной характеристике) «поднимет» потенциал базы Т2 и откроет транзистор Т2. Величина IК будет соответствовать ВАХ

IБ при Х1 = Х2 = Х3 = 1, т.е Т2 будет открыт и Uвых = ЕК – IК ×RК≡ 0.

Выше рассмотренный вариант схемы «и-не» является упрощенным и не используется из-за низкой помехоустойчивости. Данный вариант схемы используется только в схеме с «общим коллектором» для реализации монтажного, или «по низкому уровню», а также для включения элементов индикации.

Принципиальная схема стандартного элемента, используемая в серии ТТЛ представлена на рисунке.

Как видно из схемы, при наличии на одном из входов низкого уровня Т2 как и в предыдущем примере закрыт, потенциал UБТ3 ≡ UК, что приводит к его открытию и потенциал на Uвых.

Uвых ≡ Ек , т.к. нет цепи тока от источника питания на землю из-за того, что транзистор Т4 закрыт, из-за того, что Т2 закрыт UБТ4 ≡ 0

При наличии Х1 = Х2 = Х3 = 1, Т2 – открыт, Т3 – закры, Т4 – открыт, являясь в этом Uвых ≡ 0 случае приемником исходных цепей нагрузки.

Данную схему нельзя без дополнительной доработки использовать для объединения выходов для организации монтажа «или» по низкому уровню, т.к. в этом случае транзистор Т4 в элементе Uвых ≡ 0 может выйти из «строя», т.к. в этом случае где этот транзистор потечет суммарный ток всех элементов, соединенных в монтаж «или» у которых Хi1 × Хi2 × Хi3 = 0

Для того, чтобы использовать данный вариант элемента для объединения по выходу «дополнительная доработка» заключается в дополнительном сигнале ОЕ – output Enable при подаче на вход которого ОЕ = 1, выходные транзисторы Т3 и Т4 переводятся в закрытое состояние. Таким образом элемент отключается от внешней схемы не оказывая влияния на работу других по другому организуя «обрыв» своего выхода.

Альтернативным решением объединения элементов по выходам является схема с общим коллектором.. Суть заключается в том, что «выходной» транзистор, управляемый входной логикой имеет «свободный» выход коллектора не подключенный к внутренним цепям элемента. Для обеспечения работы этот выход подсоединяется к внешнему сопротивлению RК через который подсоединяется к

источнику питания объединяя группу таких элементов и подсоединяя их к общему сопротивлению получаем схему монтажную «или» по низкому уровню.

Получим F= X1X 2 X 3X 4

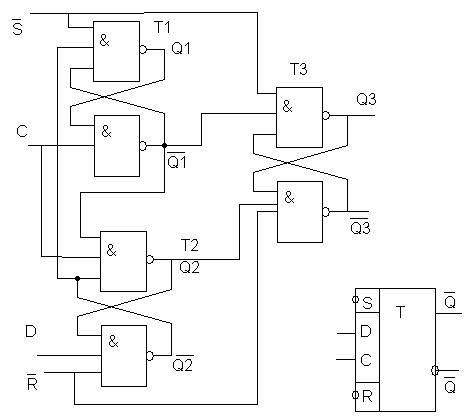

Типовые элементы построены на стандартных элементах И-НЕ

R-S тригер

Динамический DC тригер

Микроархитектурный уровень.

Микроархитектурный уровень определяет в целом архитектуру процессора, взаимосвязь процессора с памятью, структуру и тракты движения информационных потоков (команд и данных), интерпретацию выполняемых команд, взаимодействие процессора с внешними устройствами (архитектуру систем ввода/вывода).

Так по месту хранения и доступа к данным и командам архитектура бывает Фон-Нейманской или Гарвардской. По набору и сложности выполнения команд

– RISC(Reduced Instruction Set Computer) и CISC(Complicated Instruction Set

Computer)

По технологии интерпретации команд в процессоре с жѐсткой логикой и микропрограммным управлением.

По технологии (способу) связи с ВУ – с каналами ввода/вывода или

«общая шина».

Микроархитектурный уровень операционного устройства в начальный этап развития ЭВМ был представлен по меньшей мере тремя регистрами:

двумя регистрами для хранения операндов, поступающих на схему обработки

(АЛУ) и регистром хранения результата с использованием в последующих операциях или для получения и записи конечного результата в оперативную память. Дальнейшее увеличение числа регистров привело к появлению так называемой локальной (системной) памяти процессора и соответственно к расширению набора команд на втором уровне.

Регистры и интерфейс, обеспечивающий связь их с оперативной памятью формируют тракт данных, по которому данные поступают на обработку в АЛУ.

Контроль за обработкой данных осуществляет блок управления и в зависимости от его схемного решения интерпретирует выполнение либо микропрограммными средствами, либо аппаратными. Современная архитектура процессора сочетает зачастую оба этих способа, выполняя одну часть операций аппаратными средствами, а другую – микропрограммными.

Так, например, в Z архитектуре нет обязательно выделенной памяти

микропрограмм, что характерно для ранее разработанных систем с микропрограммным управлением, а микрокод представляет собой набор специальных системных команд, который находится в постоянном распределении части системной памяти HAS – и загружается в процессе загрузки системы из сервисного процессора. В отличие от других ЭВМ выполняющие в процессоре команды микрокоды имеют доступ к части аппаратных средств, доступ к которой закрыт основным командам. Микрокоды используют для выполнения таких стандартных операций, как обработка прерываний и ошибок в системе. Такая архитектура позволяет за счет интерпретации микрокодом определенных ситуаций в процессоре осуществлять не только контроль и управление за стандартными операциями,

но и расширить функции набора системных команд за счет добавления команд микрокода, т.е. ..

2.Уровень архитектуры команд.

Состоит из набора машинных команд, реализуется или аппаратными

средствами, или интерпретацией микрокоманд. Определяет RISC или CISC

архитектуру процессорного ядра.

3.Уровень операционной системы.

Появление этого уровня было связано с необходимостью автоматизации

выполняемых вычислений процессора, а также для организации многопрограммного режима ЭВМ.

Этот уровень считается гибридным, так как язык его содержит команды,

интерпретирующиеся не только средствами второго уровня, но и так называемые макрокоманды (макросредства),которые интерпретируются самой

операционной системой . Для выполнения, например, |

команд ввода-вывода, |

которые относятся к классу привилегированных и |

выполняются под |

управлением СУПЕРВИЗОР (раздел операционной системы, выполняющий организацию ввода вывода) используется макрокоманда SVC.

Уровень операционной системы позволяет организовать работу в режиме

разделенного времени, позволяющем одновременно работу нескольких пользователей по запросам с терминалов, который в дальнейшем способствовал появлению режиму «Виртуальных машин».

4.Уровень языка ассемблер.

Представляет собой символьную форму одного из языков более низкого уровня. Программы на этом уровне пишутся и транслируются на уровне 2

специальной программой, называемой ассемблером. Поэтому он называется уровнем языка ассемблера.

5.Уровень языков высокого уровня.

Предназначен для прикладных задач.