- •Архитектура вычислительных систем

- •Лекция №2 Многоуровневые организации памяти.

- •Иерархия памяти в вычислительной системе.

- •Классификация полупроводниковых зу по способу доступа к данным и хранению.

- •Краткая характеристика памяти

- •Память fifo

- •Циклическая память

- •Средства повышения быстродействия памяти

- •Полностью ассоциативная кэш.

- •Последовательная обработка команд в процессоре.

- •Классификация блоков управления по способам реализации выполнения команд: c жесткой логикой, микропрограммное управление

- •Блок микропрограммного управления

- •Идеология организации без упорядоченного выполнения

- •Переключение задачи.

ОРГАНИЗАЦИЯ ЭВМ И МНОГОПРОЦЕССОРНЫХ СИСТЕМ

КУРС ЛЕКЦИЙ

Лекция N1

Тема лекции:

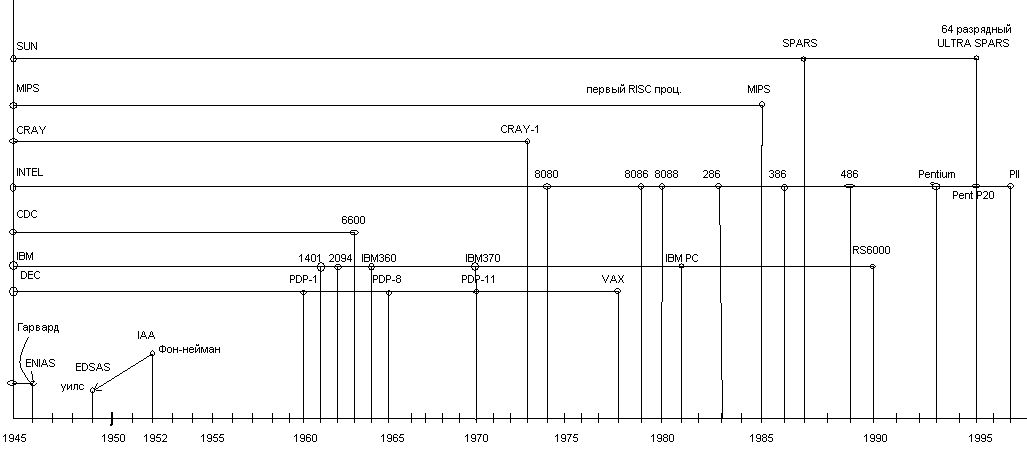

Эволюция развития ВТ

2-1. Цифровой Логический Уровень.

а) Реализация логических элементов и структур аппаратными средствами.

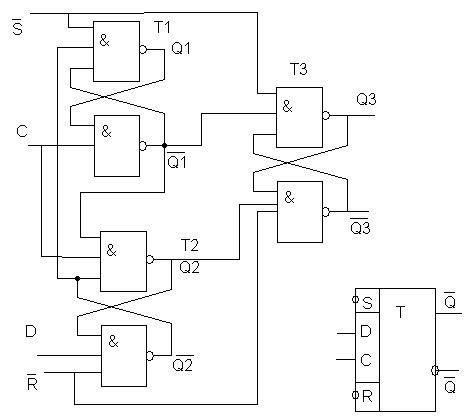

б) Построение типовых элементов триггеры, счетчики, сдвигатели на базе стандартных ветвей «и-не»

3-2. Микроструктурный уровень

Классификация В.С.

а) по способу хранения программ и данных

б) по набору исполняемых команд

в) по топологии (связи) межблочных связей

Классификация В.С.

по назначению (универсальные. специализированные.)

по производительности (мало, средне и высокопроизводительный)

Начало развития вычислительной техники.

Началом развития вычислительной техники считается период 30-х годов 19 в. Именно в этот период в 1833 г. английский математик Ч. Бэббидж предложил проект счетно-аналитической машины. Архитектура этой С.А.М. была во многом схожа с архитектурами современных компьютеров, которая должна была иметь память, вычислительное устройство, устройство ввода вывода информации. Машина естественно должна была быть механической. Проект до конца так и не был реализован и только спустя 100 лет идеи Бэббиджа были реализованы вначале на релейных элементах, а затем на электронных.

Первая попытка создания релейной машины была сделана немецким математиком Конрадом Зусом (ZиЗе) в Германии в 1938 году. Зус конструировал свою машину, не зная о разработках и идеях Бэббиджа.

Первым кто воспользовался идеями Бэббиджа был Говард Айкен под руководством которого была создана электронно-механическая цифровая вычислительная машина «MARK-1» ( в 1937-1944 гг. 1937-1944 гг.).

Машина была релейного типа, содержала 72 23-х разрядных десятичных числа для обработки (память данных). Программа для обработки этих чисел вводилась с перфокарт, т.е. по сути, были две независимые памяти: команд и данных.

Первой электронной цифровой машиной стала машина EHIAC (Electronic Humerical Integrator and Computer) – разработанная под руководством Моушли в США.

Работа над машиной была закончена в 1946 году и практически не эксплуатировалась, т.к. заказ на ее разработку сделало Министерство Обороны США для военных целей, и необходимость ее использования к этому моменту отпала.

Архитектура этой машины была подобна архитектуре релейной машины Говарда Айкена и была использована в проекте EDVAC (Electronic Discrete Viziable Computer), которому суждено было не реализоваться.

Но результаты исследований и наработок в области Ц.В.М. не прошли даром. Интерес к этой области возрос благодаря пропаганде Моушли и его помощника Экерта.

Были разработаны другие Ц.В.М.

EDSAC (1949) автор Морис Уилкс (Кембридж)

ILLIAC - Университет Иллинойс

IYANIAC – Лаборатория Лос Алмос

WEIZAC - Институт Вайцмана (Израиль)

В то время когда Моушли с Экертом работали над проектом EDVAC один из участников проекта, Фон-Нейман, ушел из группы и решил создать свою собственную версию EDVAC, которую назвал IAS – Immediate Adress Storage.

Основной проект, который Фон-Нейман хотел реализовать в своей машине, содержал два радикальных новшества, которые определили принципиальные отличия от предшествующей архитектуры.

Во-первых, Фон-Нейман предложил отказаться от представления чисел в десятизначной форме, где каждый разряд информации представлялся 10 электронными лампами, и использовать двоичную арифметику.

Во-вторых, и это было, по сути, революционным решением

- использовать общую физическую память для хранения программ и данных, тем самым упростить систему доставки кодов команд и данных из памяти в операционное устройство (АЛУ), используя для этого общий тракт.

Именно благодаря этим новшествам, которые впервые в полном объеме были использованы в машине EDSAC Морисом Уилксом, архитектура этой машины стала называться фон-неймановской.

Архитектура же с раздельным хранением программ и данных стала называться гарвардской по названию университета, где была создана «MARK-1».

Справедливости ради, следует отметить, что гарвардская архитектура была востребована через десятилетия, когда обнаружились недостатки модели фон-Неймана при решении задач, связанных с обработкой информации в реальном времени (обработка данных радиолокации наблюдений).

Именно этот класс задач требовал повышенной производительности ЭВМ, которую не смогла обеспечить фон-неймановская архитектура.

Вот тогда-то Гарвардская модель с раздельным хранением данных дала возможность одновременной выборки данных и команд и подачи их в операционное устройство, а это позволило организацию 2-х ступенчатого конвейера в котором совмещалась обработка операции в АЛУ и выборка следующей команды из памяти команд.

Таким образом, решалась проблема повышения производительности ЭВМ.

1948 год в истории развития вычислительной техники считается производительным. Помимо EDSAC, которая практически была создана, в Манчестере был запущен компьютер с 1-ой программой, который положил начало развитию программного обеспечения и языков программирования.

В этом же году фирма IBM выпустила свой первый компьютер SSEC – Selectiv Seguence Electronic Calculator и анонсировала свой первый электронный калькулятор IBM 604. По настоящему, фирма IBM стала заниматься разработкой компьютеров с 1953 года, выпустив компьютер IBM 701. Он стал первым компьютером, лидирующим на рынке в течение следующих 10 лет.

Этот год считается началом развития вычислительной техники в СССР, хотя первая электронная машина была выпущена под руководством Лебедева в 1947 г.

История развития вычислительной техники в СССР

Вычислительная техника развивалась по мере возникновения потребности использования ее в той или иной отрасли. В связи с этим и производились разработки разного класса машин.

Начальным этапом развития В.Т. в настоящее время считается 1948 год, когда по специальному приказу ЦК был организован СКБ 2-45 при заводе САМ г. Москва. Именно этому К.Б. было поручено разработка средств вычислительной техники для целей обороны и научно-технических целей Академией Наук СССР. Это промежуточный класс ЭВМ для этих целей.

Дальнейшее развитие средств В.Т. было связано с целесообразностью применения их в управлении технологическим процессом при решении задач экономического характера. Так появился класс управленческих машин и машин универсального подкласса. Центром развития управленческих машин стал г. Киев, руководитель акад. Глушков.

Развитие средств В.Т. связывают с несколькими поколениями, которые характеризуются не только архитектурными решениями, но технологической элементной базой:

- электронные лампы

- полупроводники

-микросхемы

-Бис

Следует отметить, что многие идеи и архитектурные решения средств В.Т. опережали развитие элементной базы, и полностью были реализованы позже, и были в полной мере использованы в последующих поколениях.

Так что, рассматривая архитектуру современных микропроцессоров и компьютеров, нужно иметь ввиду, что многие архитектурные решения , реализованные в них, были предложены намного раньше в предыдущих поколениях.

Такие приемы как расслоение памяти, использование КЭШ, конвейерная обработка, используемые в современных микропроцессорах были использованы в отечественных машинах 2-го поколения БЭС 2,4, (преимущественно) позволили увеличить в несколько раз производительность (БЭСМ) до 1 млн.опер./сек

Развитие средств радиолокации, решение задач метеорологии и прогноза погоды потребовало разработки специализированных высокопроизводительных ЭВМ, которые положили начало разработки суперкомпьютеров, используемых для векторных и матричных исчислений, которые впоследствии стали так и называться и относиться к классу SIMD – Sin Inst Mub Datа в классификации компьютеров с параллельными вычислениями.

Так были созданы ЭВМ «Погода» для Гидрометцентра, которые производили вычисление сумм произведений (векторные операции), «Полет» для управления летательными аппаратами и «Кристалл» для Ф.Х.И. им. Карпова для исследования структур кристаллов.

Для обработки радиолокационных данных были созданы специальные компьютеры. Среди них 5786, передвижной вариант имеющий Гарвардскую архитектуру.

Среди мощных суперкомпьютеров, выполняющих векторные и матричные операции следует отметить систему М9 и ее числовую часть М10.

За счет разнообразия признаков вычислений и многомашинной организации производительность компьютера достигла 1 млрд.опер/сек. Это при технологической базе 2-го поколения.

Расширялась не только номенклатура средств В.Т., но и география устройств разработки средств. Так уже в 1955 году был организован филиал СКБ 2-45 ВНИИМК в г.Пензе на производственной площади завода САМ (ВЭМ) была создана целая серия вычислительных машин серии УРАЛ (4,11,66).

Отмечая этот факт, следует заметить, что эта серия представляет высокопроизводительные ЭВМ, программно совместимые имеющие развитую систему прерывания до 64 уровней. Их одноадресная архитектура была использована для задач обработки больших массивов данных. По сути, эти ЭВМ предназначались для решения задач с технологией SIMD, они были ни векторными, ни матричным процессорами, но их одноадресная архитектура команд и возможность обращения к массиву в одной команде, начиная с УРАЛ 14, позволило решать вышеуказанный класс задач. Основной заказ был Министерства обороны. Кроме того машины этого класса (УРАЛ 11, 14, ) имели возможность подключения к существующим тогда стандартным каналам связи, а механизм многоканальных переключателей для устройств управления внешним устройством (компьютеры) и объединение ЭВМ в многомашинные комплексы не только на уровне внешних устройств, но и межпроцессорных связей, позволяло создавать многомашинные комплексы и многопроцессорные комплексы географически распределенные на разных территориях страны.

Так устройство сопряжения с каналом связи обеспечивает пропускную способность до 1 мб/сек. Ни одна ЭВМ не имела таких устройств.

Поэтому эти ЭВМ, вначале используемые в оборонных целях, были использованы для организации системы «Банк» в СССР. Представляют программно-аппаратный комплекс с распределительной структурой (региональными центрами) по всей стране, обеспечивающей контроль и управление движения финансовых потоков по всей территории.

Центрами разработки универсальных вычислительных машин различного класса производительности, выполняющих как задачи экономического характера, так и программы научно-технического характера стали г. Минск, г. Казань, в последствии, г. Ереван.

Серия машин Минск ЭВМ 2-го поколения стала основной для оснащения вычислительных центров по всей стране, создаваемых на предприятиях (АСУП) в 70-е годы.

Это была серия, подобно УРАЛ, программно-совместимых машин.

Отмечая возможности этой серии, следует указать, что МИНСК-32 последняя модель этой серии (М2-М22-М3) была многопрограммной ЭВМ с развитой операционной системой и системой ввода-вывода на базе каналов ввода-вывода (процессор в/выв). Эта система в/выв. обеспечивала подключение больше пар внешних устройств, имеющих широкий диапазон по емкости хранения информации и скорости передачи между ЭВМ и внешней памятью.

Наличие средств передачи данных на дальние расстояния (М.П.Д.) по телеграфным каналам пусть с наименьшей скоростью (к операционному устройству можно было подключить 32 телеграфных канала) давало возможность работать с удаленными терминалами, с которых информация поступала в центр обработки (В.Ц.). Машины М-32 имели возможность подключить и организовать межмашинный комплекс (кольцо из 8 ЭВМ).

Заканчивалась эра машин 2-го поколения. К этому времени отечественная отрасль В.Т. имела разнообразные виды ЭВМ от суперкомпьютеров (БЭСМ-6), специализированных ЭВМ 57826, «Погода», «Кристалл», серии УРАЛ, машины со своими архитектурными решениями, обеспечивающими программную совместимость, многопрограммный режим и возможность организации многомашинных комплексов с объединением их в сеть (класс управляющих машин Днепр).

Начало периода ЭВМ 3-го поколения для развития средств В.Т. в стране было связан не только с элементной базой, но и коренными изменениями архитектуры ЭВМ. Дальнейшее отечественное развитие таких серий как Минск, Урал, М-22 были прекращены. Отрасль была переориентирована на архитектурные разработки американской фирмы IBM, в то время не имеющей конкурентов на Западном рынке средств В.Т. Базовой моделью стала IBM-360 со своим набором команд, форматом данных.

Причины этих перемен были как объективного, так и субъективного характера.

В качестве объективных причин выдвигалась программная несовместимость наших ЭВМ и форматов данных, предусмотренных международным стандартам, в результате чего нельзя было использовать программные продукты наших ЭВМ.

Программные продукты наших ЭВМ не имели также широкого ассортимента и распространения. Это то и определило переориентацию на упомянутую архитектуру.

Так как архитектура ЭВМ не патентуется, патентуется только аппаратная реализация и компьютерный программный продукт, а не система команд, было принято решение на создание серии ЕС ЭВМ в разработку которой включены страны социалистического лагеря: ГДР, Венгрия, Болгария, Польша.

Центром разработки в СССР стал ВНИЦВ.Т. органов в 1968 г.

Начался период выпуска ЕС ЭВМ, которые по архитектурным решениям классифицировали на I, II, III.

Несмотря на копирование архитектуры в ЕС ЭВМ с IBM 360,370 следует отметить оригинальную разработку аппаратных средств в наших ЭВМ в этот период развития В.Т. В частности заслуживает внимания магистральная структура ЕС 1033, микроархитектурный уровень ЕС 1045,1046 в частности реализация микропрограмм управления и комплекс микропрограмм и создание на базе ЕС 1045, 1046 вычислительного комплекса ВК из 2-х ЭВМ.

В серию ЕС ЭВМ Ряд I вошли отечественные разработки ЕС 1020, ЕС 1030, ЕС 1050 соответственно с производительностью 20,100 и 500 тыс.опер./сек.

ЕС 1033 за счет магистральной структуры дала производительность до 200 тыс. опер./сек

За счет конверсии организации в ЭВМ 1050 была достигнута производительность до 500 тыс. опер./сек.

Серия ЭВМ Ряд II имела новшества в архитектурном решении. Это и наличие КЭШ (буфер памяти), и организация виртуальной памяти, реализуемой средством динамической переадресации (IBM 370), загружающего микропроцессора. К этому классу относится ЕС 1035, ЕС 1045, ЕС 1060.

ЭВМ Ряд III ЕС 1046, ЕС 1036, ЕС 1066 кроме упомянутых архитектурных решений в ряду II, имели аппаратную поддержку в виде набора микропроцессоров реализующим группу системных команд для реализации режима виртуальных машин.

Развитая системы диагностики с использованием системы, отображающей текущее состояние ЭВМ не на пульте инженера, а с использованием сервисного процессора на экране монитора повысила производительность инженерных работ при наладке и эксплуатации а автоматизированная система обнаружения неисправностей в ТЭЗАХ способствовал выполнению этих работ.

Был разработан проект ЭВМ Ряд IV, которому не суждено было осуществиться. Этим проектом предусматривалось дальнейшее усовершенствование архитектуры, в частности канальной системы с использованием очередей запросов, которая сейчас успешно используются в архитектуре серверов IBM (Z-архитектура Z9,7 990). А также организация систем виртуальных машин не на платформе одной операционной системы, а с использованием многообразия операционного режима (LPAR) которые также используются сейчас в серверах Z-apxитектуры.. Проекту не суждено было сбыться. Как причина – отсутствие технологической базы, так и по этическим мотивам (развал СССР). Единственной ЭВМ в исходном варианте стала ЕС 1187 (архитектура 1066 на элемент базе матричной бис)

В период развития ЕС ЭВМ (70-80 годы) развивались и другие направления средств В.Т.

Особое внимание следует уделить машинам класса СМ с магистральной структурой и агрегатного типа, которые давали возможность построения многопроцессорных систем взамен дорогостоящих суперкомпьютеров.

Так, используя стандартный модуль СМ, были разработаны многопроцессорные комплексы ПС 2000 и ПС 3000.

Так, ПС 2000 представлял комплекс обрабатывающих устройств, каждый из которых содержал от 130 8 процессорных унифицированных блоков на базе СМ с блоком малой оперативной памяти. О.Ц. были соединены магистралью для управления со стороны управляющих устройств представляли тогда ЭВМ СМ серии. Помимо того каждый О.Ц. имел доступ к системе в/вывода и внутренней магистрали для межблочных связей для обмена данных между собой.

По сути это был матричный процессор, имеющий архитектуру одномерной матрицы в узлах которой и находились О.Ц.

За счет параллельной обработки этот многопроцессорный комплекс достиг производительности 200 млн. опер./сек. Комплекс был успешно использован для обработки данных геологоразведки и сейсмических данных.

Само направление машин класса СМ имело цель производства малых машин, являющихся базовой структурой для производства А.Р.М. Решение о производстве малых машин было принято в 1974 году. По всей архитектуре машин этого класса имелись зарубежные аналоги ЭВМ PDP II DEC компании DEC

В заключение следует еще сказать о так называемых Р.В.М. – рекурсивных вычислительных системах.

Разработка их была начата при отсутствии высокопроизводительных компьютеров (разработки М9, М10 были закрыты и предназначались только для оборонных целей), а потребность систем подобных ПС 2000 была достаточно острой.

Так в основании рекурсивной вычислительной системы была сеть, состоящая из узлов, в состав которой входит процессорный модуль с многоканальным модулем связи.

По сути это был связной или коммуникационный процессор, который был в дальнейшем разработан фирмой «MOTOROLA» или транскомпьютер, разработанный в Англии. Начало разработки было положено в 1972 году (в 1973 году была создана М10).

Архитектура Р.В.М. очень схожа с архитектурой современных управляющих компьютеров, а также суперкомпьютеров.

BLU-G имеет подобную архитектуру в узлах которой стоят элементы, подобные тем, которые были использованы в Р.В.М.

|

|

1936 |

Z1 |

Цузе |

|

Гарвардская архитектура |

1944 |

HARK1 |

Айкен (Гарвард. арх.) |

|

1946 |

EHIAC |

Моушли/Эккерт | |

|

1949 |

EDSAC |

Уилкс (Кэмбридж) | |

|

|

1952 |

EAS |

фон-Нейман |

|

|

1960 |

PDP |

|

……………..

EHIAC – Electronic Humerical Integrator and Computer

IAS - Immediate Address Storadge

EDSAC – Electronic Discret Storage address Computer

Поколение

44-55 - Электрон лампы I

55-65 – Транзисторные II

65-80 – Интегральные микросхемы III

Идея программного управления вычислительным процессом была существенно развита американским математиком ДК фон Нейманом, который в 1945 году придумал принцип построения вычислительной машины с хранимой в памяти программой. Первые ЭВМ с программным управлением и хранением в памяти программ поставить практически одновременно в Англии, США и СССР.

IBM 604

1948

SSEC- Selectiv Seguence Electronic Calculator

Архитектура вычислительных систем

1. По способу хранения информации

а) Архитектура Фон Неймана

совместимость хранения команд и данных

б) Горвордская архитектура

раздельное хранение и параллельный (одновременный) доступ к командам и данным.

2. По виду использования команд.

а) Процессор с полным набором команд, выполняемый по сложным алгоритмам

CISC архитектура

б) Процессор с RISC архитектурой.

Набор простых команд выполняют за 1-2 такта процессора.

3. По топологии объединения блоков между собой

а) Шинная организация

б) Метод межблочных связей

Началом развития вычислительной техники считается период 30-х - 40-х годов, хотя первой попыткой создания счетно-аналитической машины считается в 1834 г. Ч. Бебиджем английским математиком профессором Кэмбриджа.

Архитектура этой С.А.М. должна была схожа с архитектурой современных компьютеров, которая должна бы иметь память, вычислительное устройство, устройство ввода и вывода. Машина была механическая и только спустя 100 лет идеи Бэбиджа были реализованы вначале на релейных элементах, а затем на электронных лампах.

Первая попытка создания релейных автоматических машин была сделана немецким математиком Конрадом Зусом (Zuse) в Германии. Еще в 1940 году он создал первую свою машину Z2. (До этого в 1938 году он создал Z1

Далее вставка

Зус конструировал свои машины не зная об разработках и идеях Бэбиджа.

В 1940 году Zuse идея

Первым кто воспользовался идеями Бэбиджа был Говорд Айкен, который был из Гарвардского университета, который начал работу с конца 30-х годов и закончил в 1944. Машины эти были релейные. Содержали 72 23-х разрядных десятичных числа, программой для обработки которых вводилась с перфокарт, т.е. в этой машине по сути были две независимые памяти: команд и данных, которые поставляли свою информацию в вычислительное устройство, время выполнения одной команды в созданной им машине занимало 6 секунд.

К моменту создания им варианта МагК II эра релейных систем устарела и появилась новая элементная база – электро-вакуумные приборы.

Одной из первых созданных вычислительных машин считается EHIAC автором разработки которой является Дж. Моушли и Экерт.

Характеристика.

Машина содержала около 18000 электроламп

1500 электромагнитных реле

20 10-разрядных регистров с десятичной системой

Работа над машиной была закончена в 1966 году и практически не эксплуатировалась, т.н. заказ на ее разработку был сделан Министерством Обороны США для военных целей, но архитектура этой машины была подобна архитектуре линейной машины Говарда Айкена и была использована в проекте другой разработки EDVAS, тем же автором.

Многоуровневая организация компьютера.

Язык высокого

уровня

Ур. 5

трансляция (компилятор)

Уровень языка

ассемблера

У р.

4

р.

4

трансляция (ассемблер)

Уровень операционной

системы

У р.

3

р.

3

трансляция (ассемблер)

Уровень архитектуры

команд мпьютера

У р.

2

р.

2

интерпретация (микропрограмма)

или непосредственное выполнение

Микроархитектурный

уровень

У р.

1

р.

1

аппаратное обеспечение

Цифровой логический

уровень

Ур. 0

Компьютер проектируется как иерархическая структура уровней, каждый из которых надстраивается над предыдущим. Каждый уровень представляет собой определённую совокупность объектов и операций над ними. Набор типов данных, операций и особенностей каждого уровня называется архитектурой. Совокупность архитектур каждого уровня и составляет архитектуру вычислительной системы, или по-другому «организацию».

ЦЛУ является низшим уровень в многоуровневой организации вычислительных систем.

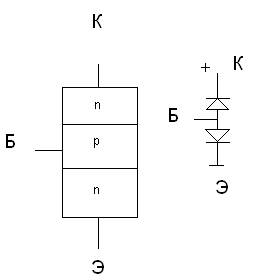

Задачей этого уровня является разработка и проектирование логических элементов, выполняющих элементарные логические операции и – не, и – или – не, на базе физических элементов: транзисторов, диодов, конденсаторов и т.д.

Элементарным элементом для построения более сложных структур (триггеров, дешифраторов, сумматоров, сдвигателей), которые являются основными узлами для построения сложных структур ЭВМ, является элемент «и – не». Этот элемент построен на базе диодно-транзисторной логики ДТЛ или транзисторно-транзисторной логики ТТЛ.

В ЭВМ 1-го поколения на электронных лампах в качестве инвертирующего элемента использовались триоды, которые в ЭВМ 2-го поколения были заменены транзисторами.

В современных ЭВМ используются БиС и СБиС. Но в основе их по-прежнему используются «классический вентель» и – не, на базе которых и проектируются вышеуказанные структуры.

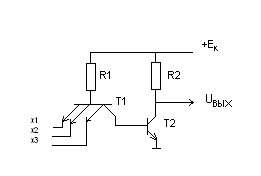

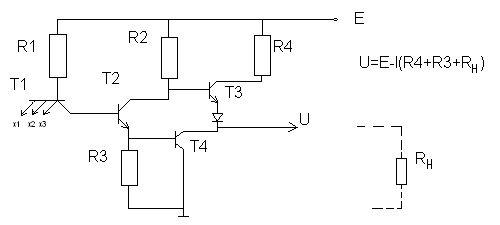

Для понимания работы ЭВМ на цифровом логическом уровне рассмотрим в общих чертах работу элемента и – не в структуре ТТЛ:

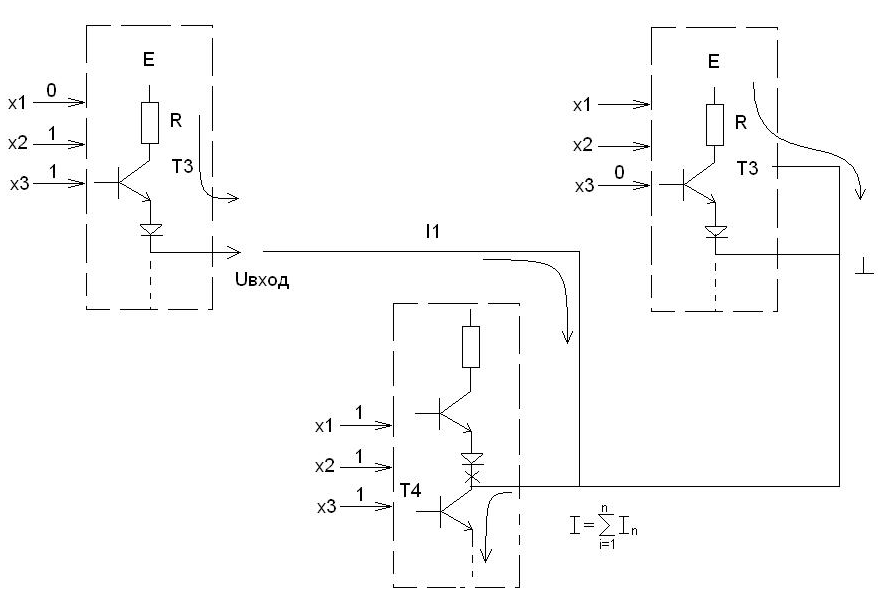

В качестве логической сборки, выполняющей функции «и» используется многоэмиттерный транзистор Т1. Функцию инвертирования выполняет Т2. Данный элемент собран на транзисторах типа n-p-n.

Основное структурное отличие многоэмитерного транзистора (МЭТ) от обычного заключается в том, что он имеет несколько эмиттеров, расположенных таким образом, что прямое взаимодействие между ними исключается, что и позволяет реализовать функцию «и».

Рассмотрим работу схемы.

Как видно из схемы переход базы – эмиттер работает в режиме прямого смещения, а переход базы - коллектор в обратном.

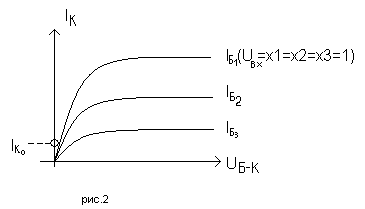

Вольт-амперная характеристика для коллектора.

Токи для данного включения имеют следующий вид.

При подаче хотя бы на один из ходов Х1, Х2, Х3 сигнала низкого уровня будет открыт один из переходов Б-Э в многоэмиттерном транзисторе. Из-за малой величины сопротивления RБ-Э. В прямом направлении UБ ≡ 0,8.

Основной ток будет стекать во входящую схему через переход Б-Э в многоэмиттерном транзисторе. Ток, втекающий в базу Т2 практически отсутствует, т.к. напряжения у Б = 0,8 будет не достаточным, чтобы открыть переход Б-К - Т2, и значение его будет IКО – равное обратному току коллектора в закрытом режиме, вследствие чего потенциал на базе Т2 у Б=IБ * RБ-Эпрям. ≡ 0 и Т2 будет закрыт (см. также вольтамперную характеристику (рис. 2).

Так как транзистор Т2 закрыт, то напряжение выходное

Uвых = ЕК – IК ×RК

В водIК

≡ 0, будет

иметь значение высокого уровня близкого

к источнику питания, т.е. данный режим

будет реализован как у=Х1

Х2 Х3

водIК

≡ 0, будет

иметь значение высокого уровня близкого

к источнику питания, т.е. данный режим

будет реализован как у=Х1

Х2 Х3

В случае всех единичных уровней на входе

Х1 = Х2 = Х3 = 1

Э

литерные

переходы Т1

будут закрыты, вследствие чего потенциал

базы в Т1 то

организует цепь тока ЕК

R1

RБ-КпрямТ1

RБ-ЭпрямТ2

0

литерные

переходы Т1

будут закрыты, вследствие чего потенциал

базы в Т1 то

организует цепь тока ЕК

R1

RБ-КпрямТ1

RБ-ЭпрямТ2

0

Увеличение тока базы в Т2 (см. в амперной характеристике) «поднимет» потенциал базы Т2 и откроет транзистор Т2. Величина IК будет соответствовать ВАХ IБ при Х1 = Х2 = Х3 = 1, т.е Т2 будет открыт и Uвых = ЕК – IК ×RК≡ 0.

Выше рассмотренный вариант схемы «и-не» является упрощенным и не используется из-за низкой помехоустойчивости. Данный вариант схемы используется только в схеме с «общим коллектором» для реализации монтажного, или «по низкому уровню», а также для включения элементов индикации.

Принципиальная схема стандартного элемента, используемая в серии ТТЛ представлена на рисунке.

Как видно из схемы, при наличии на одном из входов низкого уровня Т2 как и в предыдущем примере закрыт, потенциал UБТ3 ≡ UК, что приводит к его открытию и потенциал на Uвых.

Uвых ≡ Ек , т.к. нет цепи тока от источника питания на землю из-за того, что транзистор Т4 закрыт, из-за того, что Т2 закрыт UБТ4 ≡ 0

При наличии Х1 = Х2 = Х3 = 1, Т2 – открыт, Т3 – закры, Т4 – открыт, являясь в этом Uвых ≡ 0 случае приемником исходных цепей нагрузки.

Данную схему нельзя без дополнительной доработки использовать для объединения выходов для организации монтажа «или» по низкому уровню, т.к. в этом случае транзистор Т4 в элементе Uвых ≡ 0 может выйти из «строя», т.к. в этом случае где этот транзистор потечет суммарный ток всех элементов, соединенных в монтаж «или» у которых Хi1 × Хi2 × Хi3 = 0

Д ля

того, чтобы использовать данный вариант

элемента для объединения по выходу

«дополнительная доработка» заключается

в дополнительном сигнале ОЕ –output

Enable

при подаче на вход которого ОЕ = 1, выходные

транзисторы Т3

и Т4

переводятся в закрытое состояние. Таким

образом элемент отключается от внешней

схемы не оказывая влияния на работу

других по другому организуя «обрыв»

своего выхода.

ля

того, чтобы использовать данный вариант

элемента для объединения по выходу

«дополнительная доработка» заключается

в дополнительном сигнале ОЕ –output

Enable

при подаче на вход которого ОЕ = 1, выходные

транзисторы Т3

и Т4

переводятся в закрытое состояние. Таким

образом элемент отключается от внешней

схемы не оказывая влияния на работу

других по другому организуя «обрыв»

своего выхода.

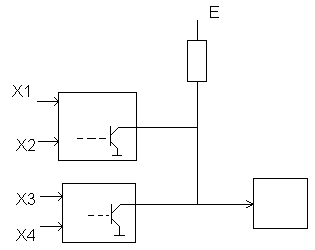

Альтернативным решением объединения элементов по выходам является схема с общим коллектором.. Суть заключается в том, что «выходной» транзистор, управляемый входной логикой имеет «свободный» выход коллектора не подключенный к внутренним цепям элемента. Для обеспечения работы этот выход подсоединяется к внешнему сопротивлению RК через который подсоединяется к источнику питания объединяя группу таких элементов и подсоединяя их к общему сопротивлению получаем схему монтажную «или» по низкому уровню.

Получим F=![]()

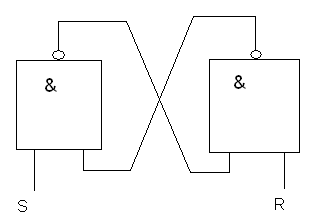

Типовые элементы построены на стандартных элементах И-НЕ

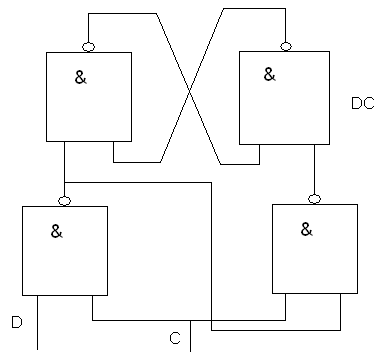

R-S тригер

Динамический DC тригер

Микроархитектурный уровень.

Микроархитектурный уровень определяет в целом архитектуру процессора, взаимосвязь процессора с памятью, структуру и тракты движения информационных потоков (команд и данных), интерпретацию выполняемых команд, взаимодействие процессора с внешними устройствами (архитектуру систем ввода/вывода).

Так по месту хранения и доступа к данным и командам архитектура бывает Фон-Нейманской или Гарвардской. По набору и сложности выполнения команд – RISC(Reduced Instruction Set Computer) и CISC(Complicated Instruction Set Computer)

По технологии интерпретации команд в процессоре с жёсткой логикой и микропрограммным управлением.

По технологии (способу) связи с ВУ – с каналами ввода/вывода или «общая шина».

Микроархитектурный уровень операционного устройства в начальный этап развития ЭВМ был представлен по меньшей мере тремя регистрами: двумя регистрами для хранения операндов, поступающих на схему обработки (АЛУ) и регистром хранения результата с использованием в последующих операциях или для получения и записи конечного результата в оперативную память. Дальнейшее увеличение числа регистров привело к появлению так называемой локальной (системной) памяти процессора и соответственно к расширению набора команд на втором уровне.

Регистры и интерфейс, обеспечивающий связь их с оперативной памятью формируют тракт данных, по которому данные поступают на обработку в АЛУ.

Контроль за обработкой данных осуществляет блок управления и в зависимости от его схемного решения интерпретирует выполнение либо микропрограммными средствами, либо аппаратными. Современная архитектура процессора сочетает зачастую оба этих способа, выполняя одну часть операций аппаратными средствами, а другую – микропрограммными.

Так, например, в Z архитектуре нет обязательно выделенной памяти микропрограмм, что характерно для ранее разработанных систем с микропрограммным управлением, а микрокод представляет собой набор специальных системных команд, который находится в постоянном распределении части системной памяти HAS – и загружается в процессе загрузки системы из сервисного процессора. В отличие от других ЭВМ выполняющие в процессоре команды микрокоды имеют доступ к части аппаратных средств, доступ к которой закрыт основным командам. Микрокоды используют для выполнения таких стандартных операций, как обработка прерываний и ошибок в системе. Такая архитектура позволяет за счет интерпретации микрокодом определенных ситуаций в процессоре осуществлять не только контроль и управление за стандартными операциями, но и расширить функции набора системных команд за счет добавления команд микрокода, т.е. ..

2.Уровень архитектуры команд.

Состоит из набора машинных команд, реализуется или аппаратными средствами, или интерпретацией микрокоманд. Определяет RISC или CISC архитектуру процессорного ядра.

3.Уровень операционной системы.

Появление этого уровня было связано с необходимостью автоматизации выполняемых вычислений процессора, а также для организации многопрограммного режима ЭВМ.

Этот уровень считается гибридным, так как язык его содержит команды, интерпретирующиеся не только средствами второго уровня, но и так называемые макрокоманды (макросредства),которые интерпретируются самой операционной системой . Для выполнения, например, команд ввода-вывода, которые относятся к классу привилегированных и выполняются под управлением СУПЕРВИЗОР (раздел операционной системы, выполняющий организацию ввода вывода) используется макрокоманда SVC.

Уровень операционной системы позволяет организовать работу в режиме разделенного времени, позволяющем одновременно работу нескольких пользователей по запросам с терминалов, который в дальнейшем способствовал появлению режиму «Виртуальных машин».

4.Уровень языка ассемблер.

Представляет собой символьную форму одного из языков более низкого уровня. Программы на этом уровне пишутся и транслируются на уровне 2 специальной программой, называемой ассемблером. Поэтому он называется уровнем языка ассемблера.

5.Уровень языков высокого уровня.

Предназначен для прикладных задач.