- •Архитектура вычислительных систем

- •Лекция №2 Многоуровневые организации памяти.

- •Иерархия памяти в вычислительной системе.

- •Классификация полупроводниковых зу по способу доступа к данным и хранению.

- •Краткая характеристика памяти

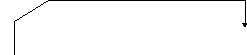

- •Память fifo

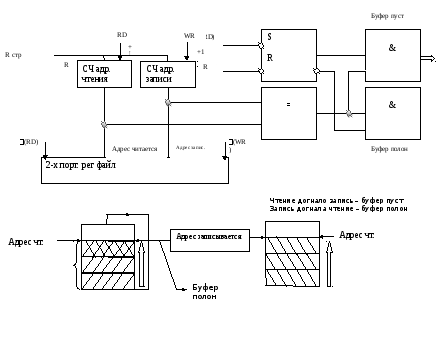

- •Циклическая память

- •Средства повышения быстродействия памяти

- •Полностью ассоциативная кэш.

- •Последовательная обработка команд в процессоре.

- •Классификация блоков управления по способам реализации выполнения команд: c жесткой логикой, микропрограммное управление

- •Блок микропрограммного управления

- •Идеология организации без упорядоченного выполнения

- •Переключение задачи.

Память fifo

Циклическая память

Лекция N 3

Тема лекции :

1.Физические структуры адресных запоминающих устройств и их классификация.

2. Динамическая память DRAM . Функционирование, физические процессы при записи /считывании данных, временные параметры и характеристики .

В основу концепции физической организации адресных запоминающих устройств заложен принцип однозначного соответствия между каждым элементом данных из области данных и соответствующим ему элементом(адресом) из области адресного пространства .

Значение адреса выражают величиной двоичного n-разрядного числа, то есть всевозможные комбинации этого числа, определяемые как N=2*n будут определять число элементов данных по- другому ее объем.

Так что же представляет собой элемент данных в памяти

Минимальным элементом в двоичном коде является бит значение которого принимает 0или1.

Вычислительная система а по другому ее программно –аппаратный комплекс оперирует в основном не каждым битом (хотя такие операции существуют) а над их группами( символы ,байты , слова) поэтому в качестве минимального элемента к которому организуют обращение со стороны процессора к памяти почти во всех современных вычислительных системах используют байт.

И так обращаясь за байтом в оперативную память мы в тоже время обращаемся ко всем битам входящим в состав байта а это возможно только в случае ,если все биты байта адресовать одним и тем же значением адреса.

В случае обращения за группой байт мы обязаны откинуть (не учитывать) младшие разряды адреса в количестве p=logn по основанию2 а n-количество одновременно выбираемых байт.

Технологически решить эту задачу можно по разному.

Можно организовать физическую структуру, в которой происходит обращение к одному биту и объединить несколько таких структур с запараллеливанием их соответствующих адресных входов.

А можно организовать обращение к нескольким элементам памяти одновременно внутри самой структуры путем их подключения к одной и той же линии выборки.

В первом случае физическая организация памяти строится по матричному способу подобно декартовой системе координат которой как известно каждой точке определены значения координат X и Y, так и в матричной структуре местонахождение элемента данных (бита) определяется однозначно на пересечении двух линий выборки по X и Y.Активизация этих линий происходит при дешифрации значений, поступающих на ДШX и ДШY, которые представляют части значения адреса.

Во втором случае используется один дешифратор то есть все биты значения адреса подают на него , который вырабатывает лишь один активный сигнал в каждом случае. Эти сигналы подаются по шинам в память, каждая шина активирует сразу несколько элементов ,подключенных к ней.

В зависимости от применения одного из способов или их совместного применения классифицируют различные структуры учитывая при этом еще и количество шин управления подводимых к элементам данных в памяти.

Исходя из выше сказанных замечаний рассмотрим различные физические структуры адресных запоминающих устройств.

Для того чтобы осуществить запись или чтение в адресные ЗУ к каждому элементу этого ЗУ хранящему минимальную информацию (бит) необходимо подавать управляющую информацию в виде адресных и информационных (данных) сигналов в зависимости от количества физических линий, используемых для этих целей и их использование для передачи логических значений сигналов различают структуры 2D,3D, 2.5D, 2DM.

Где D (dimension)- размер

А число - определяющее число линий адресных, и линий записи/считывания подводимы к каждому элементу памяти. Причем при подсчете линий записи и линий чтения принимают за 1. Структура 2D,3D, 2.5D характерны были при использовании элементов на магнитные сердечники, которые мы и рассмотрим.

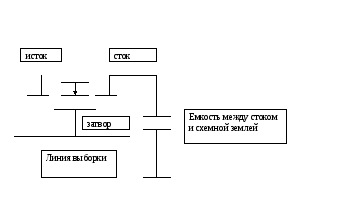

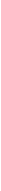

Структура 2DM характерна для современных памятей, при организации матриц из элементов собираемых на базе транзисторов, в которых в качестве запоминающего элемента используется емкость изолированного стока, выполняющая функцию конденсатора.

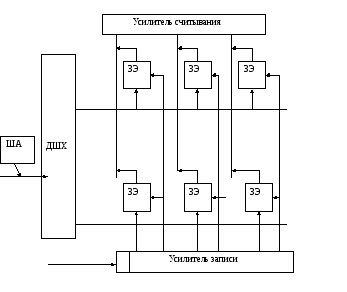

Запоминающее устройство типа 2D имеет двух координатную выборку, причем только одна координата связана со значением адреса, который определяет адрес выбираемого слова, то есть структура построенная по второму способу. Вторая координата

не связанная с шиной адреса используется для управления разрядом в слове при записи и считывании. Координата представляет две гальванически развязанные шины шину записи и шину считывания, к которым подключены усилители записи и считывания соответственно.

Ф

Фзап1

Зап 1

Счит 1

Фзап1

1

Блок –схема памяти 2D

Запись Чтение

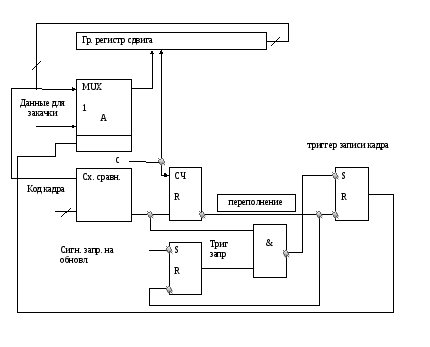

В режиме записи и считывания в координатную обмотку подаются токи разного направления, причем ток осуществляющий считывание по величине в два раза больше и должен осуществлять

перемагничивание сердечника (перевод его в нулевое состояние)

В случае единичного состояния сердечника при считывании в обмотке считывания наводится ЭДС величина тока которой определяет считывание единицы. Если сердечник находился в состоянии нуля, то ток в обмотке считывания отсутствует, так как отсутствует изменение магнитного потока, а ток помехи, возникающий от перемагничивания по частичному циклу усилителем чтения не воспринимается.

Ток записи должен быть по амплитуде равным 1/2

тока чтения и быть направлен в противоположном направлении и только в случае тока записи, подаваемого в обмотку записи разряда и имеющего то же направление, что и ток записи в адресной обмотке по сумме двух токов осуществляется перевод сердечника в состояние “1”.

В случае записи нуля ток в обмотке записи отсутствует, а величина тока записи в адресной обмотке не достаточна чтобы перевести сердечник в состояние ‘1’.

Анализируя вышесказанное можно сделать следующий вывод:

Данная структура при использовании в качестве элемента памяти магнитный сердечник при каждом обращении независимо от вида операции (запись или чтение) реализует два смежных цикла ЧТЕНИЕ-ЗАПИСЬ, с той лишь разницей, что при чтении считанные данные возвращаются обратно в память, а при записи, в предварительно обнуленные ячейки в цикле чтения, новые данные

управляют усилителями записи.

СТРУКТУРА 3D

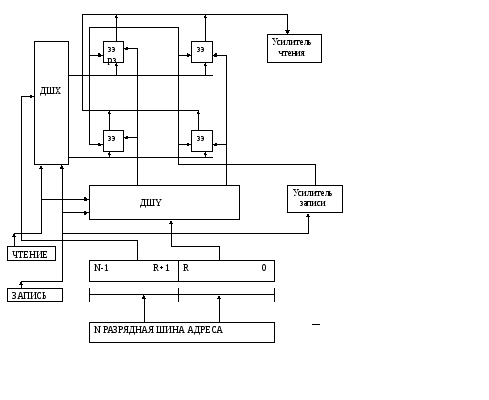

В этой структуре реализован выбор элемента по первому описанному выше способу то есть для выбора элемента памяти имеются две адресные координаты X и Y и соответственно два дешифратора ДШХ И ДШY.

Структура 3D использовалась при организации памяти на магнитных сердечниках, хотя современные технологии уже позволили разработать подобные архитектуры на полупроводниковых элементах в одном кристалле.

Структура 3D представляет набор одноразрядных матриц, число которых определяет размер считанного слова, поэтому рассмотрим структуру такой матрицы.

Как видно из блок-схемы обмотки считывания всех элементов соединены последовательно между собой и представляют прошивку, проходящую через все элементы разрядной матрицы.

Такая же топология и обмотки записи.

Считывание информации осуществляется только из одного элемента, находящегося на пересечении адресных координат,

активизированных дешифраторами.

Запись, как и в структуре 2D осуществляется подачей токов выборки в противоположном направлении относительно режима чтения. Ток подаваемый в обмотку разрядной записи в отличии от структуры 2D выполняет компенсационную функцию и имеет противоположное направление токам выборки в случае записи 0 в элемент, таким образом блокируя перемагничивание сердечника в состояние 1.В случае записи 1 ток в обмотке записи отсутствует и элемент переходит в единичное состояние.

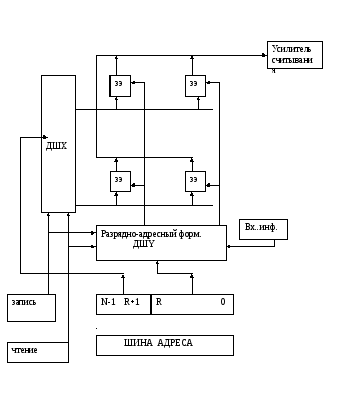

Структура 2.5D

Структура 2,5D определяется по режиму работы (участию) координатных обмоток и обмоток управления в режимах записи и считывания, потому что в режиме записи функционирует подобно структуре 2D , а в режиме чтения как 3D, то есть при записи участвуют только две обмотки одна адресная X и другая разрядно-адресная ,а при чтении три- при чем разрядно-адресная выполняет функцию координатной и совместно с другой адресной обмоткойX и обмоткой считывания реализует режим считывания как в 3D.

По количеству линий управления 2,5D имеет столько же сколько и 2D с той лишь разницей что линия управления записью ,взяв на себя функцию координатной обмотки в режиме чтения а режиме записи функцию записи 1 или 0 определила структуру матрицы для хранения одного разряда из массива слов , хранящихся в памяти подобно 3D, а никак в 2D,в которой хранится все слова массива.

То есть для организации массива памяти n-разрядных слов необходимо объединение нескольких матриц для их хранения и наличие n ДШY и один ДШX ,где каждый дешифратор ДШY в режиме записи управляет своим разрядом одновременно, выполняя и координатную функцию, а при чтении все дешифраторы работают в одном режиме , обеспечивая считывание всех разрядов слова.

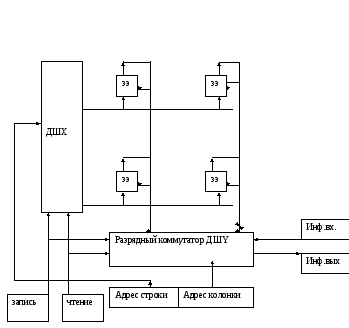

Структура 2DM

Структура 2DM стала представлять дальнейшую модификацию уже существовавших ранее структур 2D и 2,5D.

От архитектуры 2D в 2DM использована возможность одновременной активизации n элементов (слова, страницы); от 2,5D взята возможность управления поразрядного считывания и записи из матрицы, другими словами говоря в матрице 2DM стали размещать элементы не одного разряда а нескольких как в 2D при чем объединив гальванически три шины в одну ,а именно, координатную Y, разрядной записи и разрядной шины считывания

благодаря использованию в качестве запоминающего элемента транзистора с изолированным стоком, используемого в качестве обкладки накопительного конденсатора. Отметим еще раз что структура 2D на магнитных элементах ,функционирующих на принципе закона электромагнитной индукции такого объединения не допускает.

Выбор той или иной физической структуры, рассмотренные нами выше, является только частью этапа проектирования памяти. Структура определяет только топологию накопительного блока памяти , число адресных и управляющих шин подводимых к каждому элементу для хранения данных, но не определяет временных параметров и соотношений сигналов, поступающих по этим шинам к элементам. Для того чтобы устанавливать эти параметры(длительность сигналов и и их задержки относительно друг друга) необходимо знать физические процессы, происходящие в накопительном блоке при считывании и записи данных .

Проектирование временных диаграмм, определение вида и числа сигналов ,управляющих работой накопительного блока это и есть разработка протокола связи (интерфейса) памяти с вычислительной системой (процессором). Протокол реализуется блоком управления памятью. Конструктивно блок управления памятью может находиться как в составе процессора, так и на системной плате внедренным в системный чипсет, а может находиться и в самой микросхеме (внутренний контроллер). Поэтому прежде чем рассматривать организацию современных памятей с повышенным быстродействием рассмотрим основные моменты работы DRAM и процессы происходящие в ней при считывании и записи данных.

Линия записи/ считывания

К3

СЛ

К1

К0

Усилитель счит.

1.В режиме хранения ЛВ пассивна транзистор закрыт.

При выборке элемента на линию выборки подается напряжение, открывающее транзистор.

2. Перед активизацией выборки элемента на линию ЛЗС через ключ 3 подается напряжение V/2. Как только будет подан сигнал на линию выборки (ЛВ) ключ к3 размыкается.

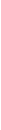

С момента подключения С заряда к линии записи/считывания начинается процесс перезаряда выравнивание потенциалов между С лзс и С заряда. Предположим что С заряда была разряжена до 0(запись 0) тогда т.к С лзc была заряжена напряжением V/2 то

Qлзс=Слзс*V/2

После перезаряда исходя из закона сохранения заряда Qлзс=(Cлзс+С3)*(V/2-∆U)

Откуда величина ∆U=V*Cзаряда/2*Слзс

Величина ∆U тем больше, чем меньше Слзс. В случае записи 1 в элементе Слзс будет подзаряжено до величины V/2+∆U

Для повышения уровня ∆U в технологии изготовления матриц в структуре 2DM с элементом памяти полупроводников также используют следующие технологические приемы:

А) увеличение емкости С заряда за счет диэлектрика, имеющего высокую диэлектрическую постоянную.

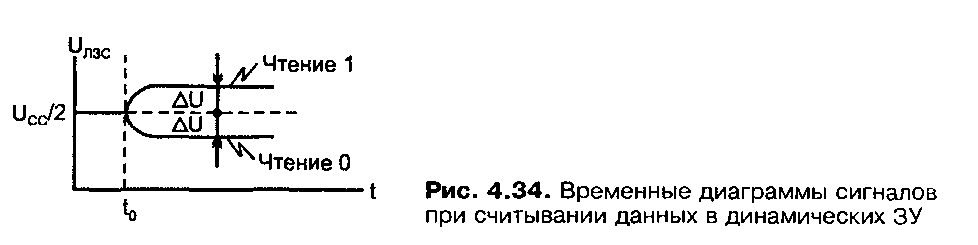

Б) уменьшение емкости ЛЗС за счет разрезания ЛЗС на 2 части и распределение запоминающих элементов поровну между ними. При этом для считывания данных из элементов памяти в разрыв включают дифференциальный усилитель, формирующий выходной сигнал считывания на значении разности потенциалов поступающих на его 2 входа.

В качестве примера рассмотрим работу

схемы усилителя-регенератора используемого

в памяти 2DM.

качестве примера рассмотрим работу

схемы усилителя-регенератора используемого

в памяти 2DM.

Схема представляет триггерный усилитель, функционирующий при подачи на затворы Т1П и Т2П сигнала «Подготовка», который формируется при считывании данных из запоминающего элемента с линий ЛЗСА или ЛЗСВ. Переключение триггера будет зависеть от значений потенциалов формирующихся при считывании, т.к. активной будет только одна линия, другая всегда будет сохранять значение предварительного перезаряда, которым были заряжены обе линии перед считыванием.

И так если с ЛЗСА если 1 то

Vлза=V/2+∆i

Vлзсв=V/2

Триггер принимает состояния Т2-отрытый, Т1- закрытый, формируя на Vлзсв=0, Vлзса=V, осуществляя регенерацию на линии считывания ЛЗСА, откуда производилось считывание, т.е. элемент считывания будет дозаряжен до значения V. Если с ЛЗСА был считан 0, то триггер принимает состояние противоположное выше описанному. Т1 будет открыт, а Т2 закрыт т.к. Vлзса=V/2-∆U, Vлзсв=V/2

И запоминающий элемент будет разряжен до 0. При считывании информации с линии ЛЗСВ например 1

Vлзсв=V/2+∆U, Vлзса=V/2 и состояние триггера будет такое же как при считывании 0 к линии ЛЗСА и при считывании 0 будет такое же как при считывании 1 с ЛЗСА.

Для того чтобы иметь однозначные значения триггера независимо от считываемой линии организуют инверсионную запись информации в одну из линий, Таким образом фиксируя значения триггера при считывании 0 или 1 независимо от линий считывания

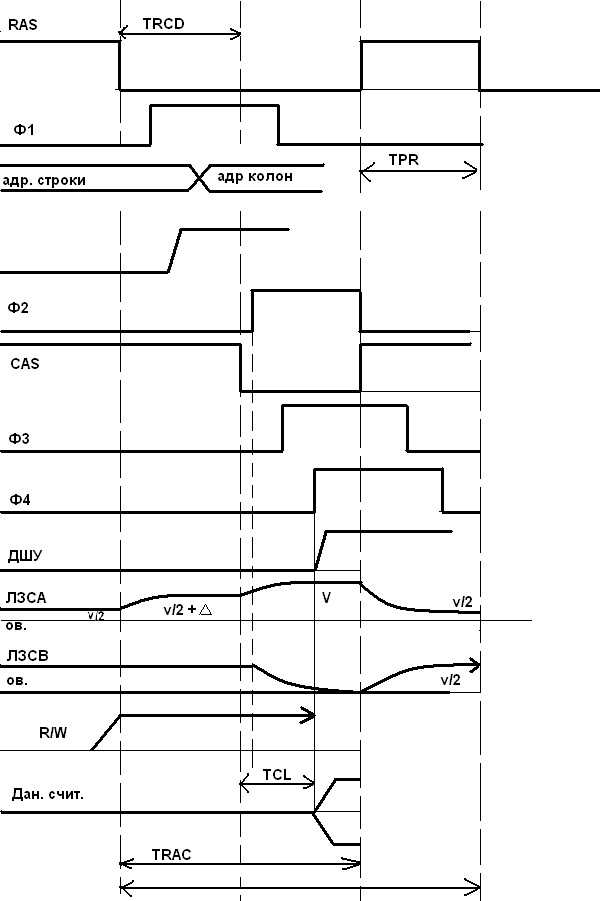

Ознакомившись с процессами, происходящими в памяти при записи и считывании, рассмотрим ее функционирование и временную диаграмму ее работы.

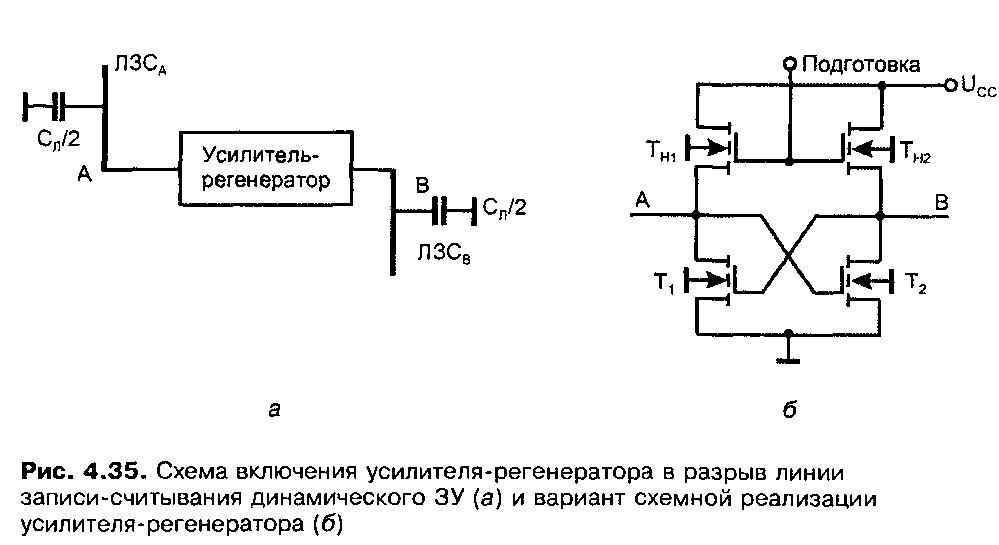

Современная архитектура памяти с произвольным доступом имеет матричную организацию массива запоминающих элементов. Адрес для выбора соответствующего элемента, хранящего информацию, подаётся на модуль памяти за 2 такта (адрес строки, и адрес столбца) с целью экономии числа адресных имен, использую мультиплексирование.

1. Выбор (доступ к

элементу памяти) начинается с подачи

![]() ,

по которому во внутреннем контроллере

памяти запускается формирователь ФТС1,

формирующий

,

по которому во внутреннем контроллере

памяти запускается формирователь ФТС1,

формирующий ![]() и

и![]() .

По

.

По ![]() осуществляется приём адреса строки в

буферный регистр и активация ДШХ, на

выходе которого активизируется одна

из линий выборки в результате чего

осуществляется подключение запоминающих

элементов к линиям ЛЗСА или ЛЗСВ

осуществляется приём адреса строки в

буферный регистр и активация ДШХ, на

выходе которого активизируется одна

из линий выборки в результате чего

осуществляется подключение запоминающих

элементов к линиям ЛЗСА или ЛЗСВ

2. Одновременно

сигнал ![]() блокирует ключи КЛ1

блокирует ключи КЛ1

1) Снимая ![]() с ЛЗСА и ЛЗСВ, потенциал одной из которых

будет определяться значением потенциала

,которым обладает информационная емкость

С , а другая (пассивная) сохранять

значение

с ЛЗСА и ЛЗСВ, потенциал одной из которых

будет определяться значением потенциала

,которым обладает информационная емкость

С , а другая (пассивная) сохранять

значение ![]()

3. Формируется

сигнал ![]() по которому подается питание на усилитель-

формирователь триггерного типа . С

этого момента начинается процесс

регенерации и потенциал активной линии

ЛЗСА

по которому подается питание на усилитель-

формирователь триггерного типа . С

этого момента начинается процесс

регенерации и потенциал активной линии

ЛЗСА ![]() V,

а пассивной ЛЗСВ

V,

а пассивной ЛЗСВ![]() 0

(считывание 1 с ЛЗСа)

0

(считывание 1 с ЛЗСа)

4. К моменту ![]() должен при высоком

должен при высоком ![]() запускается ФТС2 и формируются

запускается ФТС2 и формируются ![]() в результате действия которых

осуществляется прием кода столбца его

дешифрация в результате чего на одном

из выходов дешифратора появится активный

уровень ,открываются ключи 2 и считанная

информация при условии, что открыт ключ

4 поступает на внешнюю шину.

в результате действия которых

осуществляется прием кода столбца его

дешифрация в результате чего на одном

из выходов дешифратора появится активный

уровень ,открываются ключи 2 и считанная

информация при условии, что открыт ключ

4 поступает на внешнюю шину.

5.Состояние

триггерного усилителя- формирователя

сохраняется в течении длительности

![]() ,

которая должна быть достаточной для

приёма информации из модуля следующим

звеном передачи информации в процессор.

,

которая должна быть достаточной для

приёма информации из модуля следующим

звеном передачи информации в процессор.

6

.

Сигнал

.

Сигнал![]() выполнив свою функцию совместно с

выполнив свою функцию совместно с ![]() становятся высокими,, подготавливая

модуль памяти для следующего обращения.

становятся высокими,, подготавливая

модуль памяти для следующего обращения.

Время между двумя

![]() должно быть достаточным для того, чтобы

восстановить на ЛЗСА, ЛЗСВ значение

должно быть достаточным для того, чтобы

восстановить на ЛЗСА, ЛЗСВ значение

![]() .

Для того, чтобы можно было обратиться

к

.

Для того, чтобы можно было обратиться

к ![]() строке.

строке.

Дадим определения основным временным параметрам работы памяти.

ТRСD- время ,определяющее задержку подачи сигнала CAS относительно RAS.Эта задержка необходима для дешифрации адреса строки , активизации линии выборки и отключения линий ЛЗС от источника предзаряда.

TCL- время появления данных на линиях записи считывания от начала активизации сигнала CAS. Время отводимое для приема адреса столбца на дешифрацию и переключение ключа КЛ4,разрешающего выдачу данных с шин ЛЗС

TRAS-полное время цикла записи считывания данных из памяти.

TPR- время предзаряда шин ЛЗС, по другому, время необходимое для восстановления значения напряжения на линиях ЛЗС до величины V/2 в нашем случае , определяется временем срабатывания ключей КЛ1 и постоянной заряда линий ЛЗС

TRAS + TRP- минимальное время, через которое возможно следующее обращение к памяти.

.

ЛЕКЦИЯ N4

Тема лекции:

Организация памяти повышенного быстродействия.

Архитектура SDRAM- итог поиска архитектурных решений в предшествующих видах памятей FPM и EDO.

Модульное построение памяти. Методика проектирования памяти большого объема на стандартной элементной базе. Определение конфигурации памяти при инициализации системы .

1. Одним из первых методов повышения быстродействия памяти была технология расслоения данных в физической структуре памяти и применения метода чередования адресов обращения за данными в такой памяти. Поэтому прежде чем рассматривать другие методы, а в частности те ,что используются в современных архитектурах, отдавая дань первым разработкам, остановимся подробнее на этом методе.

Этот метод основан на модульном построении памяти ,технологию которого рассмотрим позже, и является одним из частных случаев построения памяти с физической организацией памяти в банки. Физическим банком принято считать модуль или группу модулей памяти, которые устанавливаются одновременно для обеспечения ширины выборки данных из памяти на системную шину .

Такая организация позволяет управлять размером области информационного пространства системной памяти , добавляя или удаляя модули из памяти.

При построении памяти с использованием банков из разрядной сетки адреса выделяют разряды для адресации номера банка, к которому производится обращение . В зависимости от весов этих разрядов ( местоположения в адресной сетке) формируются различные конфигурации банков.

Так ,например, выбрав для адреса банков младший разряд адреса обращения к памяти мы размещаем четные элементы в одном банке а нечетные в другом а используя технологию чередования адресов обращения к памяти повышаем ее производительность.

И так - расслоение оперативной памяти.- это метод многомодульного построения с веерной адресацией (чередованием) при которой смежные адреса информационных единиц, соответствующих ширине выборки (слова, двойные слова, и т.д.) принадлежат (размещаются) разным модулям.

Следовательно, размещая четные слова в одном, а нечетные в другом модуле при записи и организуя чтение их одновременно, при выборке получим в случае последовательного обращения по адресам увеличение производительности работы памяти. При этом будет необходим коммутатор (мультиплексор) который будет выдавать по системную шину требуемое слово.

Рег адр чтен

Модуль чет адресов D MUX

1

А D

D

D

Модуль нечет адресов

Рег адр зап D

Схема выбора модуля

Чтение/запись