- •Архитектура вычислительных систем

- •Лекция №2 Многоуровневые организации памяти.

- •Иерархия памяти в вычислительной системе.

- •Классификация полупроводниковых зу по способу доступа к данным и хранению.

- •Краткая характеристика памяти

- •Память fifo

- •Циклическая память

- •Средства повышения быстродействия памяти

- •Полностью ассоциативная кэш.

- •Последовательная обработка команд в процессоре.

- •Классификация блоков управления по способам реализации выполнения команд: c жесткой логикой, микропрограммное управление

- •Блок микропрограммного управления

- •Идеология организации без упорядоченного выполнения

- •Переключение задачи.

Средства повышения быстродействия памяти

Как следует из

анализа работы схемы, и временной

диаграммы работы памяти строка находится

в активном состоянии на протяжении

всего времени длительности сигнала

![]() ,

а величины потенциалов

,

а величины потенциалов ![]() определяются значениями выходов триггера

усилителя - регенератора пока на него

подаётся питание во время длительности

Ф2.

определяются значениями выходов триггера

усилителя - регенератора пока на него

подаётся питание во время длительности

Ф2.

V

V

ЛЗСА ЛЗСВ

Ф2

И так если

предположить, что оставляя состояние

![]() длительное время, строка будет активной

и Ф2 зафиксировать на триггере, а подавая

серию

длительное время, строка будет активной

и Ф2 зафиксировать на триггере, а подавая

серию ![]() ,

и адреса столбцов в модуль памяти,

получим увеличение быстродействия.

Именно в таком режиме работает FPM.

,

и адреса столбцов в модуль памяти,

получим увеличение быстродействия.

Именно в таком режиме работает FPM.

![]()

FPM

FPM

CAS

счит.данных

Частота следования

![]() ,

определяет время необходимое для

передачи данных из памяти в процессор.

,

определяет время необходимое для

передачи данных из памяти в процессор.

Так вот если ввести

буферный регистр, который будет сохранять

данные, то частоту следов. ![]() можно

увеличить.

можно

увеличить.

RAS

CAS

ш А

А

row col1 col2

row col1 col2

ШД

date1 date2

В памяти ЕДО серия

![]() поступает из контроллера памяти в

модуль.

поступает из контроллера памяти в

модуль.

Д альнейшее

увеличение быстродействия было

реализованоBEDO-

Best

External

Data

Out

путём введения в модуль счётчика

альнейшее

увеличение быстродействия было

реализованоBEDO-

Best

External

Data

Out

путём введения в модуль счётчика ![]() число импульсов которого определяется

длинной пакета,

а адрес

колонки передается в память

только при

первом обращении.

число импульсов которого определяется

длинной пакета,

а адрес

колонки передается в память

только при

первом обращении.

R AS

AS

C

AS ВЕDО

AS ВЕDО

. row col1

row col1

Ш

А

А

внутрен счетчикcas

ш

ина

данных

ина

данных

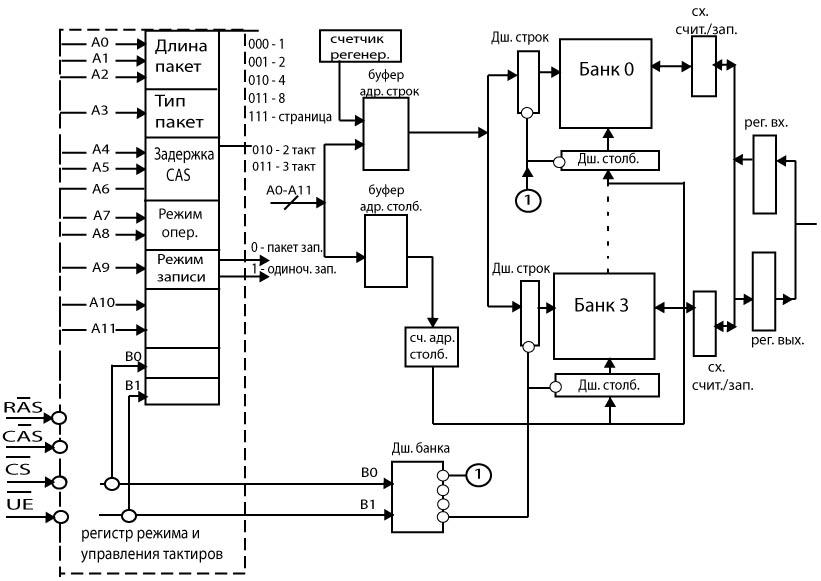

Архитектура памяти SDRAM.

Хотя SDRAM содержит внутри память DRAM, работающую как EDO, принцип управления модулем SDRAM совершенно другой, а улучшение производительности достигнуто путем “ скрытой” внутренней работы DRAM специальными методами по другому внедрением аппаратных средств, а именно:

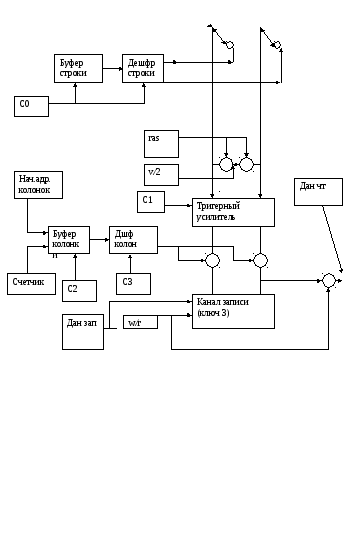

1.Синхронизация всех операций в памяти тактовой частотой системной шины .

2.Разделение микросхемы SDRAM на внутренние банки (логические) . Такое решение позволило реализовать режим чередования страниц, давший возможность исключить задержки, связанные с регенерацией, и организовать непрерывность потока данных.

3.Конвейерная обработка данных позволила производить обращение по новому адресу столбца в каждом тактовом цикле, кроме того подобно EDO микросхема SDRAM имеет внутренний счетчик потока, определяющий количество слов в потоке, и устанавливаемый из регистра режима.

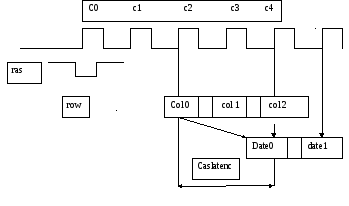

4.Регистр режима предназначен не только для хранения размера потока но и информации о типе потока(последовательное считывание или с чередованием) то есть SDRAM является устройством с программируемыми параметрами, которые и заносятся в выше упомянутый регистр.

Запись в него осуществляется в специальном цикле из внешнего контроллера памяти, данные передаются по адресной шине.

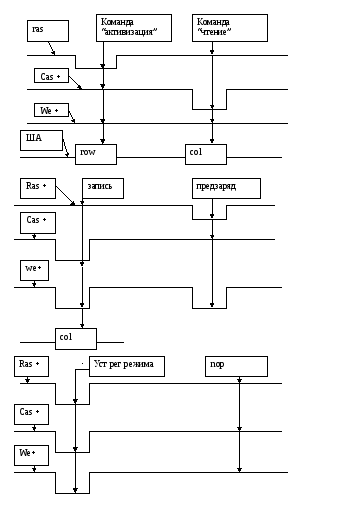

После такта записи в регистр режима следует обязательно пустой такт NOP. По окончании двух тактов инициализации начинается цикл обращения к памяти с команды “активизация”, во время выполнения которой из внешнего контроллера в SDRAM передается адрес внутреннего банка по шинам адреса и адрес строки в банке.

Указав на архитектурные особенности SDRAM,остановимся на них подробнее. Ну , во-первых, в архитектуре SDRAM вводится понятие логического банка. Вначале мы упоминали о модульном построении памяти , так вот распространяя выше упомянутую технологию на внутреннюю архитектуру самой микросхемы памяти мы приходим к понятию логический банк.

По сути физическая организация микросхемы, в которой хранятся данные (матрица) в случае организации логических банков с технологической точки зрения можно представить как набор независимых друг от друга матриц ,на которые разрезали одну большую матрицу микросхемы ,сохранив подачу одних и тех разрядов адреса строк и колонок на их дешифраторы, дополнительно подавая значения номера банка для активизации суббматрицы ,хранящей информацию того или иного банка.

Возникает вопрос. Так почему же эти внутренние банки микросхемы назвали логическими.

Ответить можно на него ссылаясь, например, на аналогичное понятие как логический диск. Логический диск-это часть дискового пространства(цилиндры или несколько дорожек) физического диска видимых вышестоящему уровню операционной системы как независимый управляемый объект, так же и логический банк, находящийся внутри микросхемы для программы видится как отдельный объект со своей памятью, к которой можно производить обращение.

Такое разрезание сделало независимыми строки разных банков, что позволило открывать последовательностью команд “активизация” их в банках в каждом цикле работы памяти и производить независимые обращения .

Если внешний контроллер “знает,” какие данные следует передать в банк, и в каком банке они находятся в случае их размещения в одном и том же физическом банке, то он может организовать обмен данными между логическими банками с задержкой в один цикл.

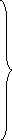

Реализация конвейера при считывании данных из памяти иллюстрируется на вышеприведенной схеме и временной диаграмме. Суть заключается в том что прием адреса столбца в буферный регистр и активизация дешифратора осуществляются двумя сериями синхронизации, смещенными во времени на такт поэтому регистр адреса столбца, передав информацию на входы дешифратора в течение текущего такта, становится свободным для приема следующего адреса колонки к началу фронта следующего синхроимпульса; а в это же время начинается дешифрация адреса предыдущей колонки таким образом данные из памяти будут выдаваться в каждом следующим такте системной шины.

Как видно из схемы для организации пакетного режима из внешнего контроллера необходимо передать адрес первой колонки(начало пакета) и значение загружаемое в счетчик(длину пакета) . Из вышесказанного следует что для организации пакетного режима требуется подготовительная операция ,которая и осуществляется в специальной команде “установка регистра режима”из внешнего контроллера.

Внешний контроллер в свою очередь для реализации протокола связи с модулем памяти имеет свой регистр режима, управляемый как внутренней аппаратной логикой, так и выше стоящим уровнем (программой) через процессор из которого и поступает тот или иной приказ на установку режима работы.

Каким образом осуществляется связь процессора с внешним контроллером памяти мы разберем в дальнейшем, а сейчас отметим то ,что регистр режима внешнего контроллера реализует следующие режимы по коду получаемому из программы или от внутренней логики

сброс(cаморегенерация)-000

nop(нет операции) -001

все банки закрыть -010

уст регистра режима -011

регенерация - 110

нормальная операция - 111

Блок-схема памяти SDRAM

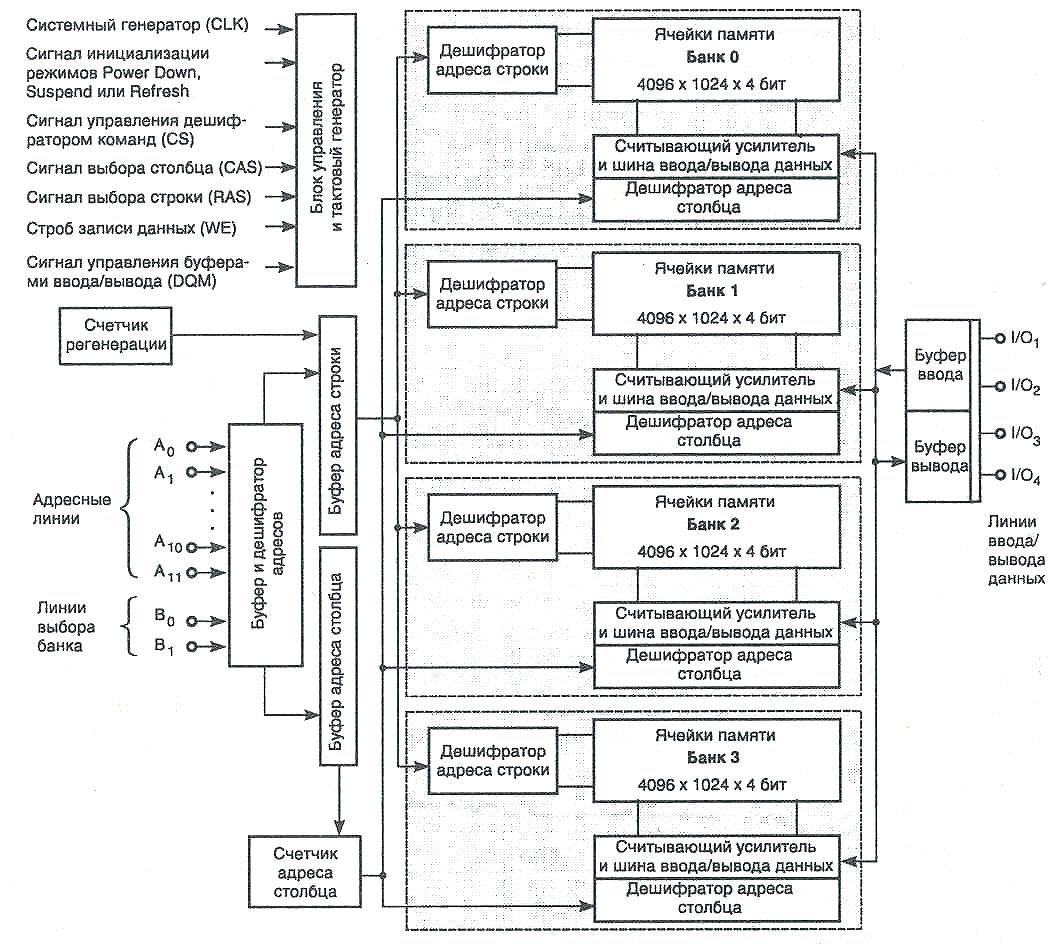

1.Память SDRAM имеет модульную структуру. В качестве исходного модуля используются микросхемы с матричной организацией хранения элементов(бит) информации со структурой 2DM.

Как обсуждалось раньше данная структура позволила активизировать одноименные строки в каждой микросхеме, которые в совокупности составляют страницу, количество слов в которой определено количеством колонок в каждой из них другим словом.

Nслов=2n

Где n-количество разрядов адреса предназначенных для адресации колонок.

2.Память SDRAM использует банковскую организацию исходных микросхем. Для выделения разрядов под адреса банков используют разряды адреса памяти с тем расчетом чтобы обеспечить определенный размер страницы. Два этих обстоятельства позволяют увеличить производительность деятельности за счет открытия нескольких банков памяти и одноименных или разноименных в них страницах. Как было указано ранее, считывание информации из разных страниц в одном банке требуют выполнения команды «Закрытие страницы и предзаряда в матрицах памяти». Для ускорения этого процесса с целью освобождения внешнего контролера от этих функций используют автоматический режим предзаряда, который устанавливают при выполнении команды “ установка регистра режима” или при передаче адреса первой колонки пакета по шине A10 т.к. этот разряд д ля адресации колонки не используют из-за ассиметричной структуры матрицы

В заключение рассмотрим виды команд, используемых для работы с памятьюSDRAM, внешним контроллером

ЛЕЦИЯ N5

ИНИЦИАЛИЗАЦИЯ И ОПРЕДЕЛЕНИЕ ТИПА

И РАЗМЕРА ПАМЯТИ.

Перед началом функционирования вычислительной системы производится определение ее конфигурации то есть определение наличия аппаратных средств ,входящих в состав.

Так ,например, в состав аппаратных средств могут входить узлы(тезы) в которых фиксируется текущая конфигурация системы: объем памяти, типы и наличие каналов ввода/вывода, идентификатор, тип и номер процессора и другая информация ,необходимая для работы операционной системы; вся эта информация считывается при включении питания или при необходимости во время работы микропрограммными или программными средствами в зависимости от архитектуры системы.

При определении объема памяти используется во многих системах метод параллельной идентификации. Суть этого метода заключается в том ,что оперативная память (адресное пространство) разбивается на блоки(при модульном построении и на соответствующие физические ) коды которых представлены старшими разрядами шины адреса и количество которых определяется размерами блоков. При наличии данного блока памяти путем перемычек код адреса блока жестко фиксируется ,кроме того используется дополнительный сигнал “блок включен”.

Текущий адрес обращения к памяти(старшие разряды, определяющие обращение к блоку) одновременно подаются на схемы сравнения ,на которые подаются кодированные значения номеров блоков с перемычек; при активном сигнале “блок включен”формируется активный сигнал обращения к блоку.

Если блок выключен, сигнал обращения остается пассивным.

Такой метод с использованием перемычек применим , если конфигурация памяти подвергается изменению в редких случаях(ограничение размера памяти в случае неисправности или ее увеличения)

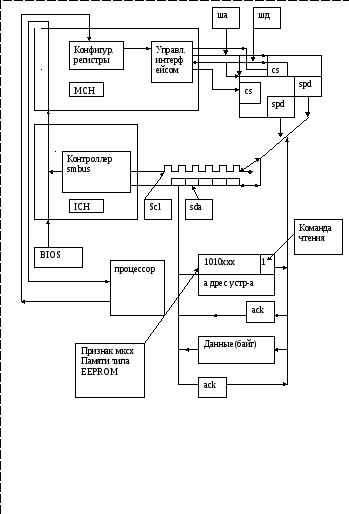

Данный метод можно использовать несколько в в другом варианте. Так в модулях SIMM-30 фирмы IBM в свое время были использованы два дополнительных вывода и по заземленным (на модуле) сигналам системная плата могла распознавать наличие и объем устанавливаемой памяти, считывая эти коды с модулей. Этот метод не выдержал конкуренции, так как для более детальной информации об архитектуре модуля нужно было увеличить число выводов и INTEL решила эту проблему по- другому, используя стандартный интерфейс i2c и энергонезависимую память, устанавливаемую на каждый модуль. В эту память при изготовлении заносится вся необходимая информация, которая считывается BIOS Ом во время инициализации. На основании ее BIOS устанавливает в конфигурационных регистрах внешнего контроллера памяти всю необходимую информацию для функционирования интерфейса.

Один из таких регистров , а точнее группа регистров, фиксируют старшие разряды адреса памяти, доступной на соответствующем физическом модуле.

Собственно говоря, используется часть выше упомянутой технологии, только заполнение содержимого номеров блоков происходит не за счет установленных перемычек а программно, используя выше упомянутый канал связи

Модуль памяти (микросхема SPD) >i2c>ICH>MCH(конфигурационный регистр внешнего контроллера памяти)

2. МОДУЛЬНОЕ ПОСТРОЕНИЕ ПАМЯТИ

Так как микросхемы памяти по глубине своего адресного пространства, которое определяется числом входов подаваемых на адресные входы микросхем не обеспечивает в большинстве случаев объем системной памяти, то при расчете в первую очередь проводят расчет субмодуля - узла из количества микросхем, обеспечивающих ширину выборки.

![]()

:

:

:

![]() m

m

L/m – количество микросхем,

![]() емкость

субмодуля

емкость

субмодуля

![]()

:

: m

![]()

Ввиду того, что из памяти считывается L разрядов одновременно, где количество считываемых байт равно L/8, а в памяти адресуется каждый байт, то для адресации одновременно считываемых байт из памяти мы обязаны откинуть справа в адресной сетке «Р» разрядов.

![]() .

Или

.

Или

![]() - количество одновременно считываемых

байт. Оставшиеся разряды будут использованы

следующим образом:

- количество одновременно считываемых

байт. Оставшиеся разряды будут использованы

следующим образом:

![]() - число субмодулей

- число субмодулей

![]() -

емкость микросхем

-

емкость микросхем

![]() - шина выборки

- шина выборки

![]() +

+![]() - емкость субмодуля

- емкость субмодуля

![]()

![]()

![]()

t разрядов k p

Субмодуль

(2^k)хе

e

e

ДШ

С таршие

таршие

t разрядов : :

: :

Субмодуль

(2^k)хе

e

РЕГЕНЕРАЦИЯ ПАМЯТИ

Динамическая память требует восстановления информации после обращения в неё за данными и в процессе хранения ввиду саморазряда конденсаторов, которые используют в качестве запоминающего элемента.

Как было рассмотрено при анализе DRAM и SDRAM, для регенерации достаточно активизировать только строки, при этом происходит автоматическое восстановление информации во всей строке. Т.е. через определённое время каждый элемент памяти требует к нему обращения с целью восстановления хранимой в нём информации. Различные системы реализуют этот процесс по-разному.

Так в системах с шинной организацией, где на шине данных и адреса кроме данных находятся другие агенты шины, контролер шины вынужден через определенные промежутки времени организовывать запрос к процессору на владение шиной.

Так в свое время в режиме регенерации был задействован один из каналов DMA (прямого доступа памяти), в котором хранилась информация адреса, на котором останавливался предыдущий цикл.

Б лок-схема

лок-схема

Генератор вырабатывает импульсы и через делитель частоты организует импульсы запросов на регенерацию процессор. В случае подтверждения устанавливает ТРЕГ=1, разрешая работу счетчика, формирующего адреса регенерации (строк) и сопровождающиеся сигналом RAS. На время регенерации блокируются сигналы RAS и CAS от процессора. Цикл регенерации определяет время работы счетчика и заканчивается по сигналу переполнения. Для подачи адреса строки на модуль используется мультиплексор, управляющий триггером регенерации.

В архитектуре современных компьютеров с шинной организацией, в которых интегрированная память, контроллер выделен. Схема управления регенерацией организована как во внешнем контроллере, так и частично во внутреннем контроллере (микросхема памяти). Внешний контроллер выдает только команду регенерации CBR, которая формируется через определенное время, обозначенное циклом регенерации.

Поскольку обращение к памяти к различным ее ячейкам происходит в случайном порядке, то для динамической памяти для сохранности информации необходимы циклы регенерации.

Memory Refresh.

Циклы регенерации могут быть организованы различными способами. Классическим способом является цикл без импульса CAS, сокращенно ROR (RAS only refresh)

Вторым распространенным способом является CBR (CAS before RAS). Данный способ в частности используется в SDRAM, т.к. последовательный ROR в этой памяти воспринимается как команда «АКТ» - активизация строки. Кроме организации циклов регенерации со стороны внешнего контроллера используется режим само регенерации. Адрес регенерируемой строки берется из внешнего контролера для цикла ROR и из внутреннего счетчика регенерации для цикла CBR. Т.е. для SDRAM адрес регенерируемой строки хранится в самой микросхеме памяти. Активизация циклов CBR из внешнего контролера происходит через определенные промежутки времени.

Само регенерация.

Режим само регенерации организуется в микросхеме при переводе сигнала CKE(clock enable) в низкий уровень со стороны внешнего контролера.

В режиме само регенерации микросхемы периодически выполняют циклы регенерации по внутреннему таймеру и не реагируют на внешние сигналы, поэтому внешняя синхронизация может быть остановлена. Причинами остановки синхронизации могут быть следующие обстоятельства:

1) выполнение инструкции HULT в процессоре. В результате процессор переходит в состояние S1

S1 – останавливает таймеры системной платы , но сохраняются данные в системной памяти.

2) S2 – дополнительно отключается питание КЭШ, системной платы и процессора, но сохраняется состояние оперативной памяти

3) S3 – обесточиваются все компоненты системной платы, кроме оперативной памяти

Примечание: выполнение ‘SLEEP’ [S1, S2, S3] может произойти в случае ‘shut down’, когда операционная система обнаруживает аварийную ситуацию.

ЛЕКЦИЯ N6

КЭШ ПАМЯТЬ

Тенденция к повышению производительности работы В.С. привела к необходимости ввода в архитектуру так называемой КЭШ памяти, являющейся дополнительным буфером информации между системной памятью и процессором. КЭШ память по объёму намного меньше, чем системная память и хранящая копии её ячеек, помимо накопительного блока, для данных, должна содержать индексный или тэговый блок по адресному объёму равный накопительному. В этом индексном блоке должна храниться информация однозначно определяющая какие конкретные ячейки оперативной памяти отражаются в тех или иных ячейках накопительного блока КЭШ.

Так как системная память является адресным устройством с произвольным доступом, то в качестве тэгов используются адреса ячеек системной памяти (полный или частичный в зависимости от архитектуры КЭШ)

Различают в основном 3 типа КЭШ:

- полностью ассоциативная,

- прямого отображения

- наборно-ассоциативная.