ORGANIZATsIYa_EVM

.pdfЛекция №2

Многоуровневые организации памяти.

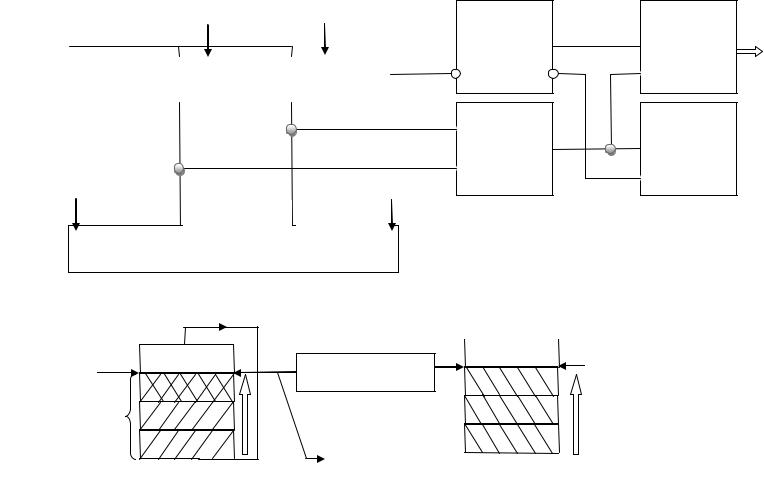

Прежде чем рассматривать классификацию памяти в вычислительных системах, отметим что она имеет многоуровневую организацию. Если «двигаться» от процессора в сторону системной памяти, то:

на 1ом уровне в самом процессоре существует регистровая память. Она может быть физически организована как отдельные регистры или как регистровый файл, обращения к регистровой памяти осуществляется из команд по адресу регистра, находящимся в соответствующем поле формата команды.

на 2ом уровне может быть представлена как буферная (или кэш) память с соответствующими подуровнями 1, 2, 3. Данная память предназначена для хранения частей «копий» основной или системной памяти. Обращение к ней осуществляется по значению физических адресов, после преобразования логического адреса в физический. Кэш память имеет сложный блок управления (контроля) в функции которого входит кроме формирования циклов чтения/записи анализ наличия в данный момент затребованных данных в самой кэш и их достоверность. Содержимому в оперативной памяти.

3й уровень эта сама системная память, обращение к которой (адресация) имеет достаточно долгую историю развития от указания абсолютного адреса, указанного в команде (Фон - Нейман) до использования механизмов базирования, индексирования и механизмов динамического преобразования адресов, используемых при организации виртуальной памяти в системе.

4й уровень - внешняя память. Это внешнее устройство хранения данных с достаточно широким спектром как по способам доступа, так и способом хранения, основными видами которой является до сего момента устройства хранения на магнитных лентах и дисковых подсистемах.

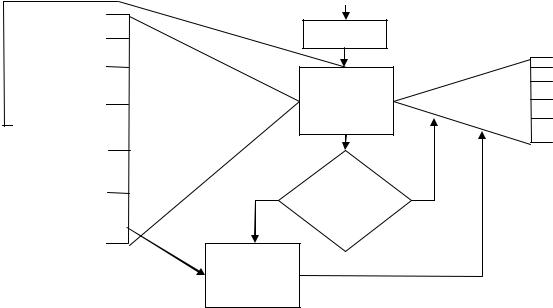

Архитектуру виртуальной памяти в общих чертах можно представить следующим образом.

1.Имеется область адресного пространства, определяемая числом бит входящих в разрядную сетку шины адреса. А=2n. А – число элементов минимального размера, хранящегося в виртуальной памяти (биты), где n – число разрядов в шине адреса.

2.Эта область адресного пространства не связана с размером физической памяти в процессоре и намного ее больше.

3.Область этого адресного пространства предоставлена пользователю полностью в его распоряжение, т.е. каждый пользователь работает в своей виртуальной памяти. При одном условии, что память эта разбивается на более «крупные» элементы, страницы и сегменты.

4.Физически содержимое виртуальной памяти размещается в вычислительной системе в области физической памяти процессора (та часть, которая выбирается процессором или в скором времени будет обработана) и основная ее часть на внешней памяти.

5.Имеется аппаратно программируемы комплекс преобразования виртуальных (логических) адресов в реальные (физические) при выполнении программ. Программа, программный код, работает с логическими адресами.

6.Существует системы контроля наличия информации (страница, сегмент) соответствующему тому или иному логическому адресу в данный момент в опустевшей памяти процессора, при отсутствии осуществляется подкачка с внешнего носителя страницы или сегмента в оперативную память .

Внешняя |

Лог. адрес |

|

|

|

|

память |

|

|

|

Программно |

Оперативная |

|

память |

|

|

аппаратный |

|

|

комплекс |

|

|

преобразования |

|

Сегм, стран. в операт. памяти

Подкачка. Осущ. подкачку в оп. память

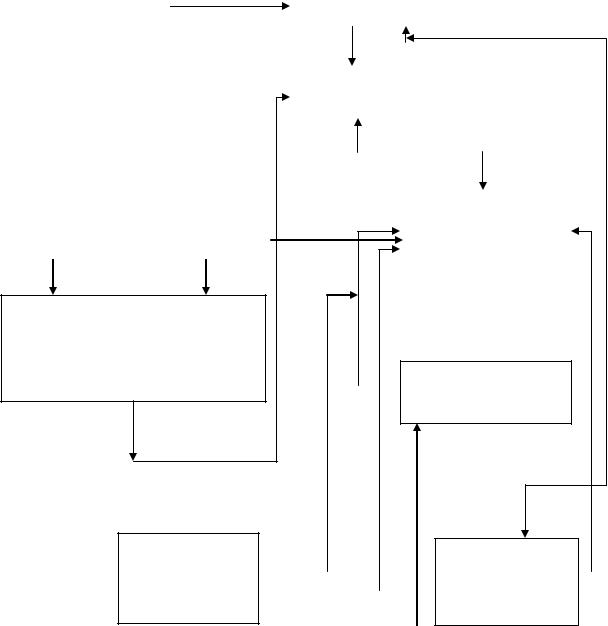

Иерархия памяти в вычислительной системе.

Адрес, который |

|

процессор |

|

|

формируется в |

|

(регистровая память) |

|

|

|

|

|

|

|

формате команды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

КЭШ память |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

блок |

|

блок |

|

|

|

|

системная |

||

формирования |

|

формирования |

|

|

адреса операнда |

|

адреса |

|

память |

|

|

команды |

|

|

|

|

|

|

|

Блок преобразования логического адреса в реальный

Внешняя

Внешняя

память

ПДПпрямой доступ памяти

канал ввода\вывода

шд

ша

Память в ЭВМ имеет иерархическую структуру. На верхнем процессорном уровне представлена как регистровая память информация в которую поступает или из системной памяти или из КЭШ. Адресуется номер регистра из формата команды на следующем уровне КЭШ является отображением (копией) части системной памяти. Адресуется как и системная память при наличии механизма виртуализации адреса после преобразования виртуального адреса в реальный.

Нижний уровень внешней памяти более ѐмкий. Связь внешней памяти с системной зависит от архитектуры системы. Различают 2 основных метода: 1) Метод прямого доступа ПДП

2)Канальная система

Врежиме ПДП обмен между внешней памятью и системной осуществляется непосредственно используя внешний контроллер на шине или встроенный в контроллер внешнего устройства в зависимости от архитектуры системы.

Врежиме канала, канал поступает посредником, используя программы и поддерживая 2 протокола.

1)Протокол канал - ВУ

2) Протокол канал - память.

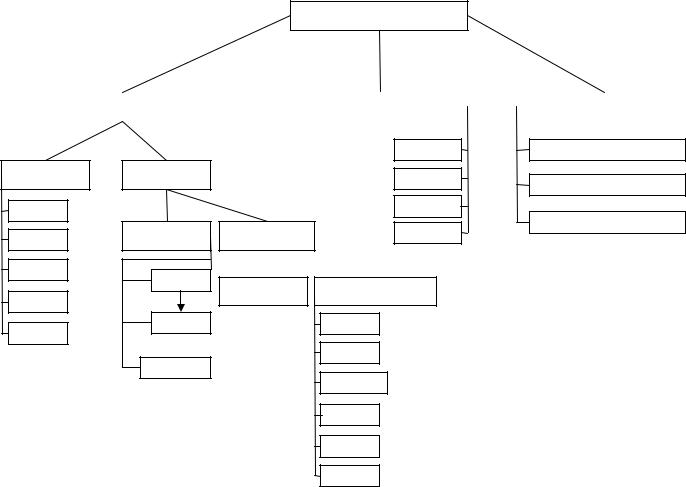

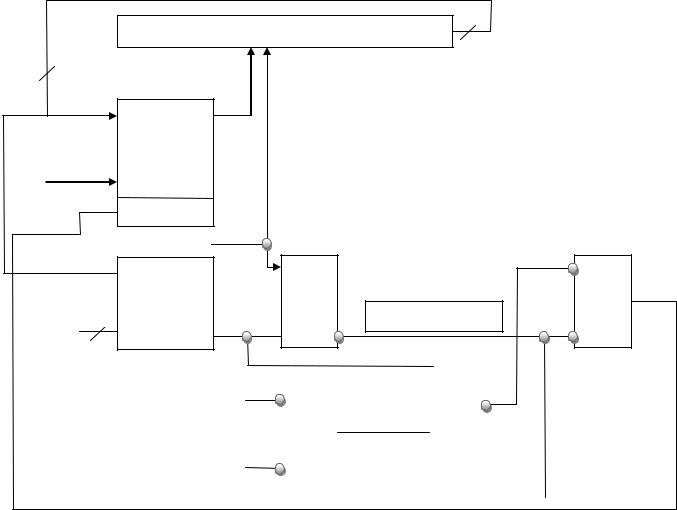

Классификация полупроводниковых ЗУ по способу доступа к данным и хранению.

По зап. устройства вычис.

Адресные |

|

Последовательностные |

|

Асоциативные |

|

|

|

|

|

|

|

|

FIFO |

Полностью асоциативная |

ПЗУ (ROM) |

RAM |

|

стековая |

|

|

|

|

С прямым размещением |

|

|

|

|

|

|

ROM |

|

|

фаловая |

|

|

|

|

|

|

|

|

|

|

Наборноасоциативная |

PROM |

Статическая |

Динамическая |

циклич. |

|

|

|

|

|

|

EPROM |

|

|

|

|

|

асинхр |

Стандартная |

Кон. повыш. быстр |

|

|

|

|

||

EEPROM |

|

|

|

|

|

тактир. |

|

FPM |

|

FLASH |

|

|

|

|

|

|

|

EDORA |

|

|

синхр. кон |

|

|

|

|

|

|

BEDORA |

|

SDRAM

RDRAM

DRRAM

Краткая характеристика памяти

Постоянно запоминающие устройства (ПЗУ)

ROM – Read Only Memory

(ПЗУ) – постоянно запоминающее устройство PROM – программируемое ЗУ (ППЗУ)

EPROM – перепрограммируемое ЗУ с ультрафиолетовым стиранием EEPROM – перепрограммируемое ЗУ с электрическим стиранием

EEPROM по структуре и технологическим особенностям выделен в отдельный класс.

Статические.

В качестве запоминающего элемента применяют триггерные схемы. Разделяются на синхронные и асинхронные предполагают реакцию микросхем памяти на вход сигнал CS (по фронту или уровню)

Последовательные.

По способу хранения могут входить в категорию как статические так и динамической памяти. Доступ осуществляется по последовательным адресам изменяющимся на  при обращении в зависимости от цикла записи или чтения.

при обращении в зависимости от цикла записи или чтения.

FIFO – первый пришел, первый ушел определяет алгоритм работы, т.е. первая запись в память сразу становиться доступной для чтения.

Стековая или LIFO – последний пришел, первый ушел характеризует алгоритм записи и чтения в/из памяти доступ к первой записанной ячейке в случае нескольких последовательных циклов записей возможно только при выборке (чтении) всех последующих ячеек, в которых производилась запись.

Реализация может быть в обычной памяти структуры RAM при соответствующем алгоритме изменения значения адреса ячеек при записи и чтении.

Файловая память аналогичная FIFO, с той лишь разницей, что доступ к первой ячейке, в которую была произведена запись возможно только после заполнения буфера.

Циклическая память используется в видео системах для отображения кадров на экране монитора. Может быть реализована на основе адресной памяти и так же на статических элементах (триггерах) организованных как регистры сдвига.

В случае использования адресной памяти, счетчик адреса работает в циклическом режиме, обеспечивающим обращение к ячейкам ЗУ с периодом кадровой развертки.

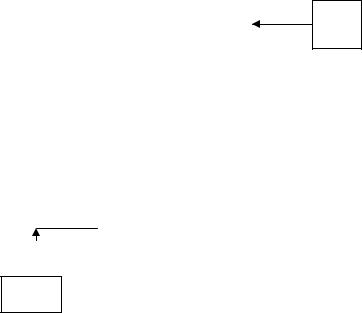

Память FIFO

|

|

|

RD |

|

|

|

WR (RD) |

|

|

|

|

|

+ |

|

+1 |

||

R стр |

|

|

|

|

||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

(WR) |

|

|

|

|

|

|

|

||

|

|

|

СЧ адр. |

|

|

СЧ адр. |

|

R |

|

|

|

|

|

|

|||

|

|

|

чтения |

|

|

записи |

|

|

|

|

|

|

|

|

|

|

|

Буфер пуст

S

& R

& R

|

|

= |

& |

(RD) |

Адрес запис. |

(WR) |

|

Адрес читается |

|

Буфер полон |

2-х порт. рег файл

Чтение догнало запись – буфер пуст Запись догнала чтение – буфер полон

Адрес чт. |

Адрес записывается |

Адрес чт. |

|

|

Буфер полон

Циклическая память

Гр. регистр сдвига

|

МUХ |

|

Данные для |

1 |

|

закачки |

||

А |

||

|

триггер записи кадра

С |

|

|

|

Сх. сравн. |

СЧ |

|

S |

Код кадра |

R |

|

R |

|

переполнение |

||

|

|

|

|

|

|

Триг |

& |

|

Сигн. запр. на |

|

S |

|

||

|

запр |

|

|

||

обновл. |

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Лекция N 3

Тема лекции :

1.Физические структуры адресных запоминающих устройств и их классификация.

2. Динамическая память DRAM . Функционирование, физические процессы при записи /считывании данных, временные параметры и характеристики .

Воснову концепции физической организации адресных запоминающих устройств заложен принцип однозначного соответствия между каждым элементом данных из области данных и соответствующим ему элементом(адресом) из области адресного пространства .

Значение адреса выражают величиной двоичного n-разрядного числа, то есть всевозможные комбинации этого числа, определяемые как N=2*n будут определять число элементов данных подругому ее объем.

Так что же представляет собой элемент данных в памяти Минимальным элементом в двоичном коде является бит значение которого принимает 0или1.

Вычислительная система а по другому ее программно –аппаратный комплекс оперирует в основном не каждым битом (хотя такие операции существуют) а над их группами( символы ,байты , слова) поэтому в качестве минимального элемента к которому организуют обращение со стороны процессора к памяти почти во всех современных вычислительных системах используют байт.

И так обращаясь за байтом в оперативную память мы в тоже время обращаемся ко всем битам входящим в состав байта а это возможно только в случае ,если все биты байта адресовать одним и тем же значением адреса.

Вслучае обращения за группой байт мы обязаны откинуть (не учитывать) младшие разряды адреса в количестве p=logn по основанию2 а n-количество одновременно выбираемых байт. Технологически решить эту задачу можно по разному.

Можно организовать физическую структуру, в которой происходит обращение к одному биту и объединить несколько таких структур с запараллеливанием их соответствующих адресных входов.

А можно организовать обращение к нескольким элементам памяти одновременно внутри самой структуры путем их подключения к одной и той же линии выборки.

Впервом случае физическая организация памяти строится по матричному способу подобно декартовой системе координат которой как известно каждой точке определены значения координат X и Y, так и в матричной структуре местонахождение элемента данных (бита) определяется однозначно на пересечении двух линий выборки по X и Y.Активизация этих линий происходит при дешифрации