ORGANIZATsIYa_EVM

.pdf

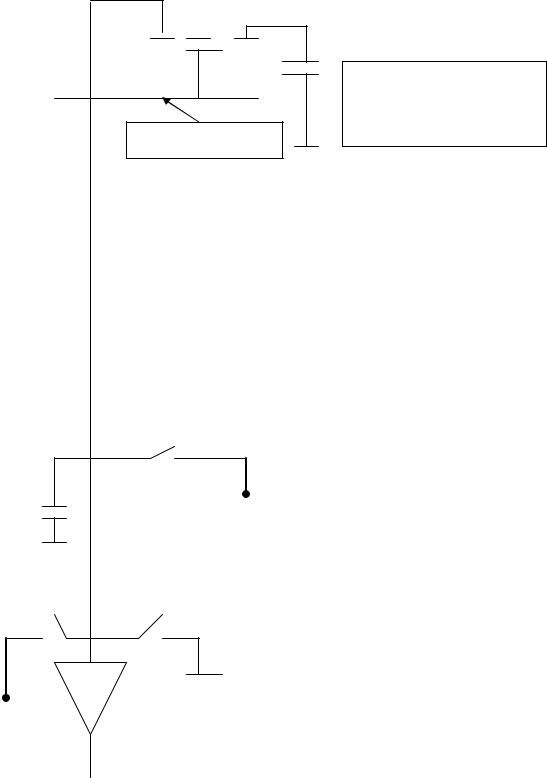

Конденсатор для хранения заряда (бита информации)

Линия выборки

|

СЛ |

|

К3 |

К1 |

К0 |

Усилитель счит.

1.В режиме хранения ЛВ пассивна транзистор закрыт.

При выборке элемента на линию выборки подается напряжение,

открывающее транзистор.

2. Перед активизацией выборки элемента на линию ЛЗС через ключ 3

подается напряжение V/2. Как только будет подан сигнал на линию выборки

(ЛВ) ключ к3 размыкается.

С момента подключения С заряда к линии записи/считывания начинается процесс перезаряда выравнивание потенциалов между С лзс и С заряда.

Предположим что С заряда была разряжена до 0(запись 0) тогда т.к С лзc была заряжена напряжением V/2 то

Qлзс=Слзс*V/2

После перезаряда исходя из закона сохранения заряда

Qлзс=(Cлзс+С3)*(V/2-∆U)

Откуда величина ∆U=V*Cзаряда/2*Слзс

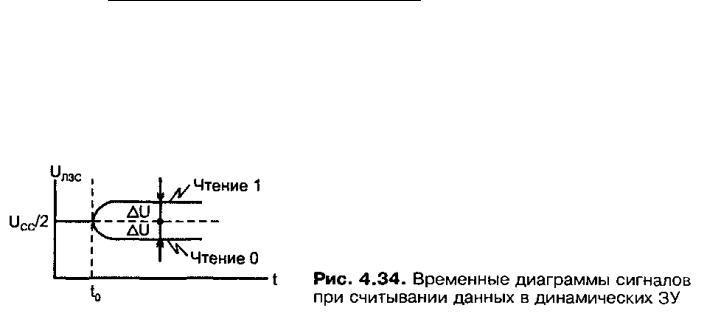

Величина ∆U тем больше, чем меньше Слзс. В случае записи 1 в элементе Слзс будет подзаряжено до величины V/2+∆U

Для повышения уровня ∆U в технологии изготовления матриц в структуре

2DM с элементом памяти полупроводников также используют следующие технологические приемы:

А) увеличение емкости С заряда за счет диэлектрика, имеющего высокую диэлектрическую постоянную.

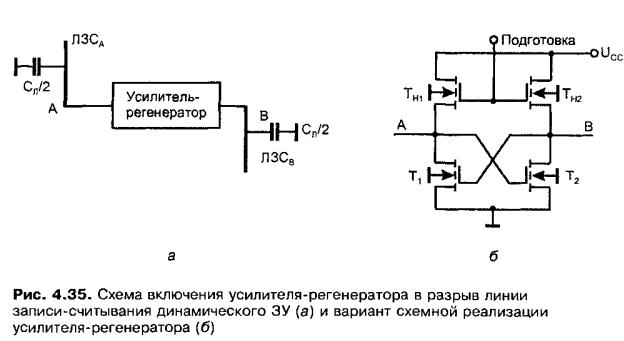

Б) уменьшение емкости ЛЗС за счет разрезания ЛЗС на 2 части и распределение запоминающих элементов поровну между ними. При этом для считывания данных из элементов памяти в разрыв включают

дифференциальный усилитель, формирующий выходной сигнал считывания на значении разности потенциалов поступающих на его 2 входа.

В качестве примера рассмотрим работу схемы усилителя-регенератора используемого в памяти 2DM.

Схема представляет триггерный усилитель, функционирующий при подачи на затворы Т1П и Т2П сигнала «Подготовка», который формируется при считывании данных из запоминающего элемента с линий ЛЗСА или ЛЗСВ.

Переключение триггера будет зависеть от значений потенциалов формирующихся при считывании, т.к. активной будет только одна линия,

другая всегда будет сохранять значение предварительного перезаряда, которым были заряжены обе линии перед считыванием.

И так если с ЛЗСА если 1 то

Vлза=V/2+∆i

Vлзсв=V/2

Триггер принимает состояния Т2-отрытый, Т1закрытый, формируя на

Vлзсв=0, Vлзса=V, осуществляя регенерацию на линии считывания ЛЗСА,

откуда производилось считывание, т.е. элемент считывания будет дозаряжен до значения V. Если с ЛЗСА был считан 0, то триггер принимает состояние противоположное выше описанному. Т1 будет открыт, а Т2 закрыт т.к.

Vлзса=V/2-∆U, Vлзсв=V/2

И запоминающий элемент будет разряжен до 0. При считывании информации с линии ЛЗСВ например 1

Vлзсв=V/2+∆U, Vлзса=V/2 и состояние триггера будет такое же как при считывании 0 к линии ЛЗСА и при считывании 0 будет такое же как при считывании 1 с ЛЗСА.

Для того чтобы иметь однозначные значения триггера независимо от считываемой линии организуют инверсионную запись информации в одну из линий, Таким образом фиксируя значения триггера при считывании 0 или 1

независимо от линий считывания Ознакомившись с процессами, происходящими в памяти при записи и

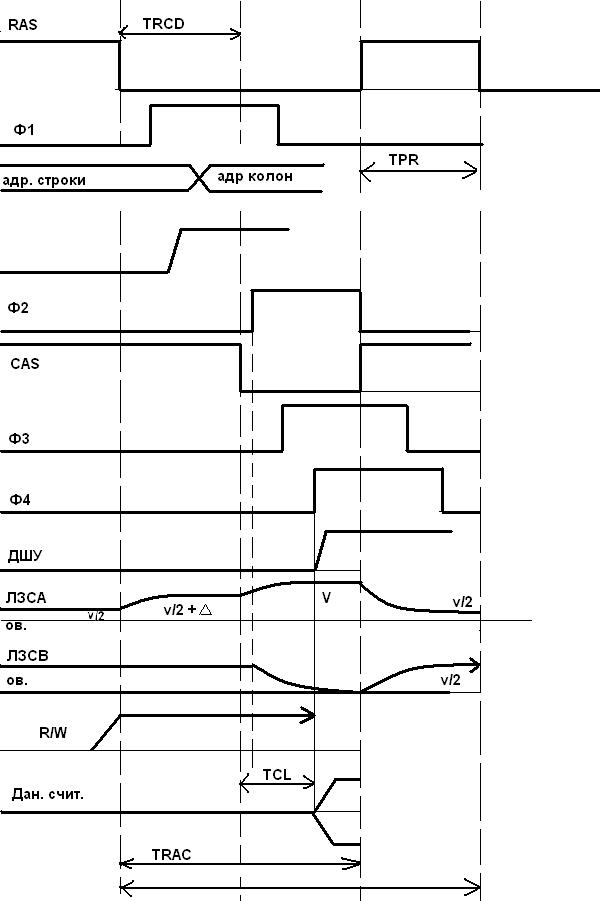

считывании, рассмотрим ее функционирование и временную диаграмму ее работы.

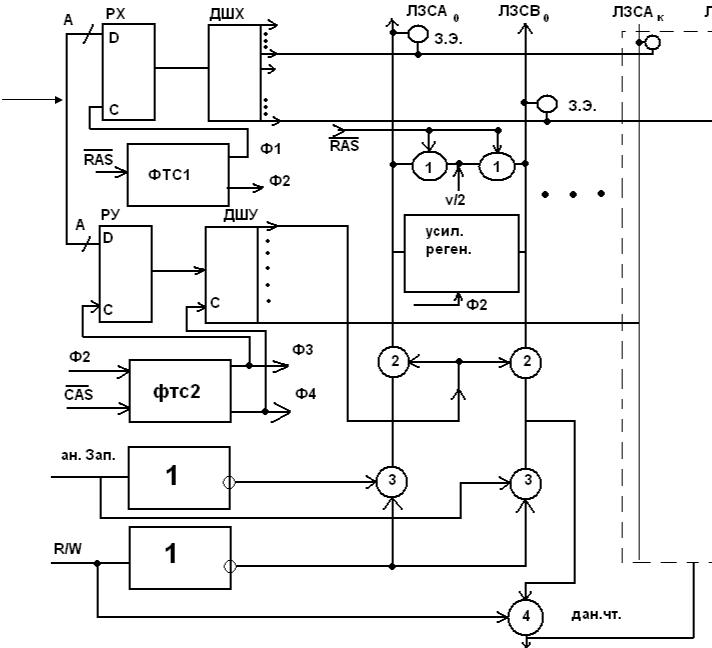

Современная архитектура памяти с произвольным доступом имеет матричную организацию массива запоминающих элементов. Адрес для выбора соответствующего элемента, хранящего информацию, подаѐтся на модуль памяти за 2 такта (адрес строки, и адрес столбца) с целью экономии числа адресных имен, использую мультиплексирование.

1. Выбор (доступ к элементу памяти) начинается с подачи  , по которому во внутреннем контроллере памяти запускается формирователь ФТС1, формирующий

, по которому во внутреннем контроллере памяти запускается формирователь ФТС1, формирующий  и

и . По

. По  осуществляется приѐм адреса строки в буферный

осуществляется приѐм адреса строки в буферный

регистр и активация ДШХ, на выходе которого активизируется одна из линий выборки в результате чего осуществляется подключение запоминающих элементов к линиям ЛЗСА или ЛЗСВ 2. Одновременно сигнал  блокирует ключи КЛ1

блокирует ключи КЛ1

1) Снимая  с ЛЗСА и ЛЗСВ, потенциал одной из которых будет

с ЛЗСА и ЛЗСВ, потенциал одной из которых будет

определяться значением потенциала ,которым обладает информационная емкость С , а другая (пассивная) сохранять значение

3. Формируется сигнал  по которому подается питание на усилительформирователь триггерного типа . С этого момента начинается процесс регенерации и потенциал активной линии ЛЗСА

по которому подается питание на усилительформирователь триггерного типа . С этого момента начинается процесс регенерации и потенциал активной линии ЛЗСА  V, а пассивной ЛЗСВ

V, а пассивной ЛЗСВ 0 (считывание 1 с ЛЗСа)

0 (считывание 1 с ЛЗСа)

4. К моменту  должен при высоком

должен при высоком  запускается ФТС2 и формируются

запускается ФТС2 и формируются  в результате действия которых осуществляется прием кода столбца его

в результате действия которых осуществляется прием кода столбца его

дешифрация в результате чего на одном из выходов дешифратора появится активный уровень ,открываются ключи 2 и считанная информация при условии, что открыт ключ 4 поступает на внешнюю шину.

5.Состояние триггерного усилителяформирователя сохраняется в течении длительности  , которая должна быть достаточной для приѐма информации из модуля следующим звеном передачи информации в процессор.

, которая должна быть достаточной для приѐма информации из модуля следующим звеном передачи информации в процессор.

6. Сигнал  выполнив свою функцию совместно с

выполнив свою функцию совместно с  становятся высокими,, подготавливая модуль памяти для следующего обращения.

становятся высокими,, подготавливая модуль памяти для следующего обращения.

Время между двумя  должно быть достаточным для того, чтобы восстановить на ЛЗСА, ЛЗСВ значение

должно быть достаточным для того, чтобы восстановить на ЛЗСА, ЛЗСВ значение  . Для того, чтобы можно было обратиться к

. Для того, чтобы можно было обратиться к  строке.

строке.

Дадим определения основным временным параметрам работы памяти. ТRСDвремя ,определяющее задержку подачи сигнала CAS относительно RAS.Эта задержка необходима для дешифрации адреса строки , активизации линии выборки и отключения линий ЛЗС от источника предзаряда.

TCLвремя появления данных на линиях записи считывания от начала активизации сигнала CAS. Время отводимое для приема адреса столбца на дешифрацию и переключение ключа КЛ4,разрешающего выдачу данных с шин ЛЗС

TRAS-полное время цикла записи считывания данных из памяти. TPRвремя предзаряда шин ЛЗС, по другому, время необходимое для

восстановления значения напряжения на линиях ЛЗС до величины V/2 в нашем случае , определяется временем срабатывания ключей КЛ1 и постоянной заряда линий ЛЗС

TRAS + TRPминимальное время, через которое возможно следующее обращение к памяти.

.

ЛЕКЦИЯ N4

Тема лекции:

1.Организация памяти повышенного быстродействия. Архитектура SDRAMитог поиска архитектурных решений в предшествующих видах памятей FPM и EDO.

2.Модульное построение памяти. Методика проектирования памяти большого объема на стандартной элементной базе. Определение конфигурации памяти при инициализации системы .

1. Одним из первых методов повышения быстродействия памяти была технология расслоения данных в физической структуре памяти и применения метода чередования адресов обращения за данными в такой памяти. Поэтому прежде чем рассматривать другие методы, а в частности те ,что используются в современных архитектурах, отдавая дань первым разработкам, остановимся подробнее на этом методе. Этот метод основан на модульном построении памяти ,технологию которого рассмотрим позже, и является одним из частных случаев построения памяти с физической организацией памяти в банки. Физическим банком принято считать модуль или группу модулей памяти, которые устанавливаются одновременно для обеспечения ширины выборки данных из памяти на системную шину .

Такая организация позволяет управлять размером области информационного пространства системной памяти , добавляя или удаляя модули из памяти.

При построении памяти с использованием банков из разрядной сетки адреса выделяют разряды для адресации номера банка, к которому производится обращение . В зависимости от весов этих разрядов ( местоположения в адресной сетке) формируются различные конфигурации банков.

Так ,например, выбрав для адреса банков младший разряд адреса обращения к памяти мы размещаем четные элементы в одном банке а нечетные в другом а используя технологию чередования адресов обращения к памяти повышаем ее производительность.