ORGANIZATsIYa_EVM

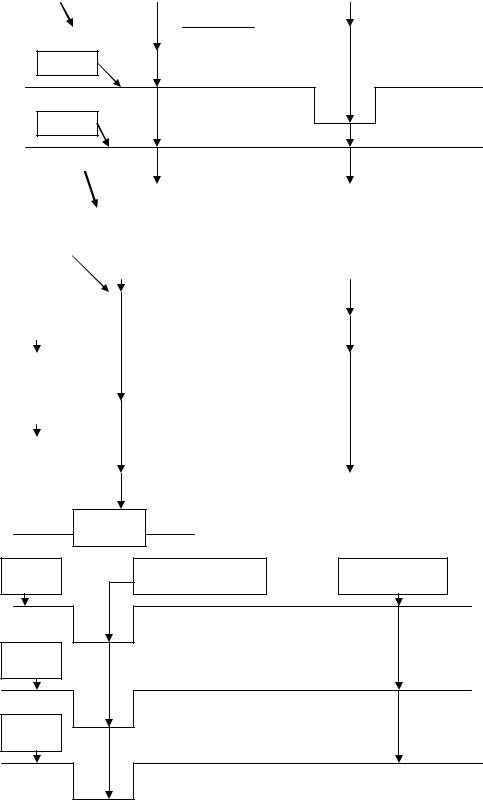

.pdfБлок-схема памяти SDRAM

1.Память SDRAM имеет модульную структуру. В качестве исходного

модуля используются микросхемы с матричной организацией хранения

элементов(бит) информации со структурой 2DM.

Как обсуждалось раньше данная структура позволила активизировать

одноименные строки в каждой микросхеме, которые в совокупности

составляют страницу, количество слов в которой определено количеством

колонок в каждой из них другим словом.

Nслов=2n

Где n-количество разрядов адреса предназначенных для адресации

колонок.

2.Память SDRAM использует банковскую организацию исходных микросхем. Для выделения разрядов под адреса банков используют разряды адреса памяти с тем расчетом чтобы обеспечить определенный размер страницы. Два этих обстоятельства позволяют увеличить производительность деятельности за счет открытия нескольких банков памяти и одноименных или разноименных в них страницах. Как было указано ранее, считывание информации из разных страниц в одном банке требуют выполнения команды «Закрытие страницы и предзаряда в матрицах памяти». Для ускорения этого процесса с целью освобождения внешнего контролера от этих функций используют автоматический режим предзаряда, который устанавливают при выполнении команды “ установка регистра режима” или при передаче адреса первой колонки пакета по шине A10 т.к. этот разряд д ля адресации колонки не используют из-за ассиметричной структуры матрицы

В заключение рассмотрим виды команд, используемых для работы с памятьюSDRAM, внешним контроллером

|

|

|

Команда |

|

Команда |

|

|||

ras |

|||||||||

|

|

“активизация” |

|

“чтение” |

|

||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cas +

We +

|

ША |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

row |

|

|

col |

|

|

|

|||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Ras + |

|

|

запись |

|

|

|

предзаряд |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Cas + |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

we+ |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

col |

|

Ras + |

Уст рег режима |

nop |

Cas +

We+

ЛЕЦИЯ N5

ИНИЦИАЛИЗАЦИЯ И ОПРЕДЕЛЕНИЕ ТИПА И РАЗМЕРА ПАМЯТИ.

Перед началом функционирования вычислительной системы производится определение ее конфигурации то есть определение наличия аппаратных средств ,входящих в состав.

Так ,например, в состав аппаратных средств могут входить узлы(тезы) в которых фиксируется текущая конфигурация системы: объем памяти, типы и наличие каналов ввода/вывода, идентификатор, тип и номер процессора и другая информация ,необходимая для работы операционной системы; вся эта информация считывается при включении питания или при необходимости во время работы микропрограммными или программными средствами в зависимости от архитектуры системы.

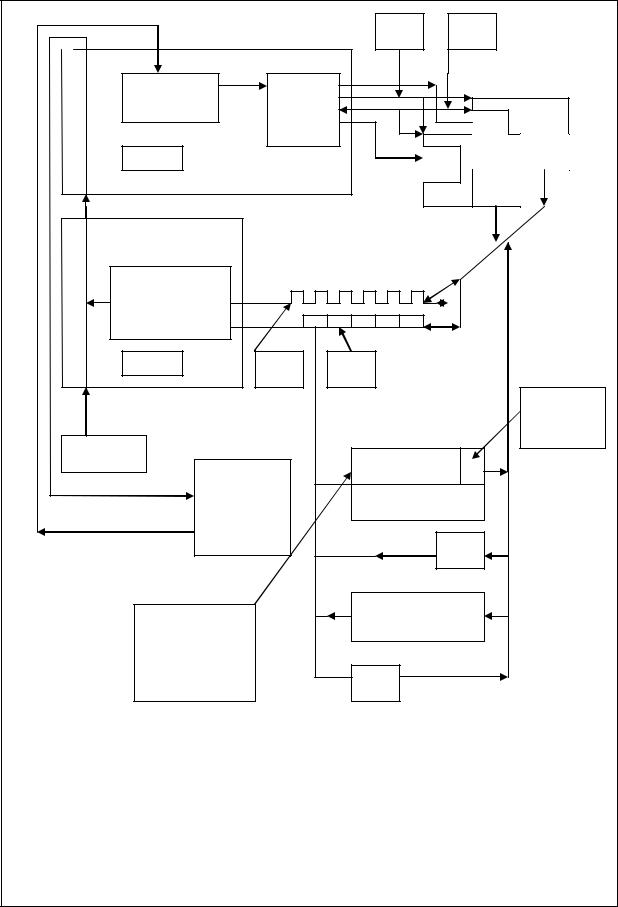

При определении объема памяти используется во многих системах метод параллельной идентификации. Суть этого метода заключается в том ,что оперативная память (адресное пространство) разбивается на блоки(при модульном построении и на соответствующие физические ) коды которых представлены старшими разрядами шины адреса и количество которых определяется размерами блоков. При наличии данного блока памяти путем перемычек код адреса блока жестко фиксируется ,кроме того используется дополнительный сигнал “блок включен”. Текущий адрес обращения к памяти(старшие разряды, определяющие обращение к блоку) одновременно подаются на схемы сравнения ,на которые подаются кодированные значения номеров блоков с перемычек; при активном сигнале “блок включен”формируется активный сигнал обращения к блоку.

Если блок выключен, сигнал обращения остается пассивным. Такой метод с использованием перемычек применим , если конфигурация памяти подвергается изменению в редких случаях(ограничение размера памяти в случае неисправности или ее увеличения)

Данный метод можно использовать несколько в в другом варианте. Так в модулях SIMM-30 фирмы IBM в свое время были использованы два дополнительных вывода и по заземленным (на модуле) сигналам системная плата могла распознавать наличие и

объем устанавливаемой памяти, считывая эти коды с модулей. Этот метод не выдержал конкуренции, так как для более детальной информации об архитектуре модуля нужно было увеличить число выводов и INTEL решила эту проблему подругому, используя стандартный интерфейс i2c и энергонезависимую память, устанавливаемую на каждый модуль. В эту память при изготовлении заносится вся необходимая информация, которая считывается BIOS Ом во время инициализации. На основании ее BIOS устанавливает в конфигурационных регистрах внешнего контроллера памяти всю необходимую информацию для функционирования интерфейса.

Один из таких регистров , а точнее группа регистров, фиксируют старшие разряды адреса памяти, доступной на соответствующем физическом модуле.

Собственно говоря, используется часть выше упомянутой технологии, только заполнение содержимого номеров блоков происходит не за счет установленных перемычек а программно, используя выше упомянутый канал связи

Модуль памяти (микросхема SPD) >i2c>ICH>MCH(конфигурационный регистр внешнего контроллера памяти)

|

|

ша |

шд |

|

Конфигур. |

Управл |

|

|

|

регистры |

. |

|

|

|

|

интерф |

|

cs |

|

MCH |

|

cs |

spd |

|

|

|

|||

|

|

|

spd |

|

Контроллер |

|

|

|

|

smbus |

|

|

|

|

ICH |

Scl |

sda |

|

|

|

|

|

Команда |

|

|

|

|

чтения |

|

BIOS |

|

1010ххх |

1 |

|

процессор |

||||

|

|

|||

|

|

а дрес устр-а |

|

|

|

|

ack |

||

Признак мксх |

|

Данные(байт) |

|

|

|

|

|

||

Памяти типа |

|

|

|

|

EEPROM |

|

|

|

|

|

|

aсk |

|

|

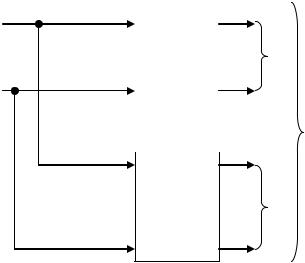

2. МОДУЛЬНОЕ ПОСТРОЕНИЕ ПАМЯТИ

Так как микросхемы памяти по глубине своего адресного пространства,

которое определяется числом входов подаваемых на адресные входы микросхем не обеспечивает в большинстве случаев объем системной памяти, то при расчете в первую очередь проводят расчет субмодуля - узла из количества микросхем, обеспечивающих ширину выборки.

А0

: |

|

|

: |

|

|

Аk 1 |

|

m |

|

|

L/m – количество микросхем, |

|

|

|

А0 |

|

емкость субмодуля 2k xL |

|

||

: |

|

|

: |

|

m |

Аk 1

Ввиду того, что из памяти считывается L разрядов одновременно, где количество считываемых байт равно L/8, а в памяти адресуется каждый байт,

то для адресации одновременно считываемых байт из памяти мы обязаны откинуть справа в адресной сетке «Р» разрядов.

P log 2 l / 8 . Или 2 p - количество одновременно считываемых байт.

Оставшиеся разряды будут использованы следующим образом:

2t - число субмодулей

2k - емкость микросхем

2 p - шина выборки

2k + 2 p - емкость субмодуля

2t |

2k |

2 p |

t разрядов |

k |

p |

|

|

А[0†k-1] |

Субмодуль |

|

|

|

|

|

|

|

e |

|

|

|

|

|

|

|

|

|

|

|

|

|

ДШ |

|

|

|

|

Старшие |

|

|

(2^k) х е |

|

|

|

|

|

|

|

|

t разрядов |

|

: |

: |

|

|

|

|

: |

: |

|

|

|

|

|

|

|

|

|

|

|

Субмодуль |

||

|

|

|

|

|

|

e

(2^k) х е

РЕГЕНЕРАЦИЯ ПАМЯТИ Динамическая память требует восстановления информации после

обращения в неѐ за данными и в процессе хранения ввиду саморазряда конденсаторов, которые используют в качестве запоминающего элемента.

Как было рассмотрено при анализе DRAM и SDRAM, для регенерации достаточно активизировать только строки, при этом происходит автоматическое восстановление информации во всей строке. Т.е. через определѐнное время каждый элемент памяти требует к нему обращения с целью восстановления хранимой в нѐм информации. Различные системы реализуют этот процесс по-разному.

Так в системах с шинной организацией, где на шине данных и адреса кроме данных находятся другие агенты шины, контролер шины вынужден через определенные промежутки времени организовывать запрос к процессору на владение шиной.

Так в свое время в режиме регенерации был задействован один из каналов

DMA (прямого доступа памяти), в котором хранилась информация адреса, на котором останавливался предыдущий цикл.

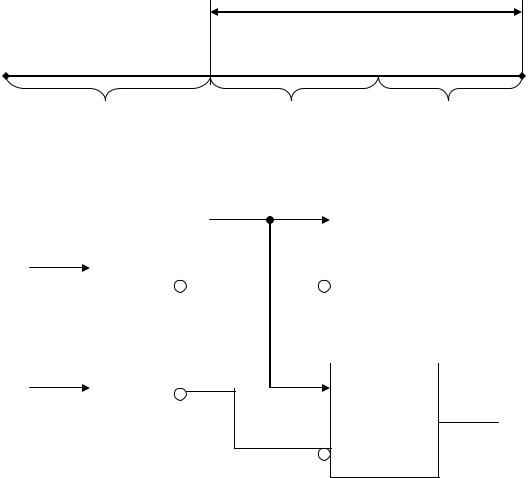

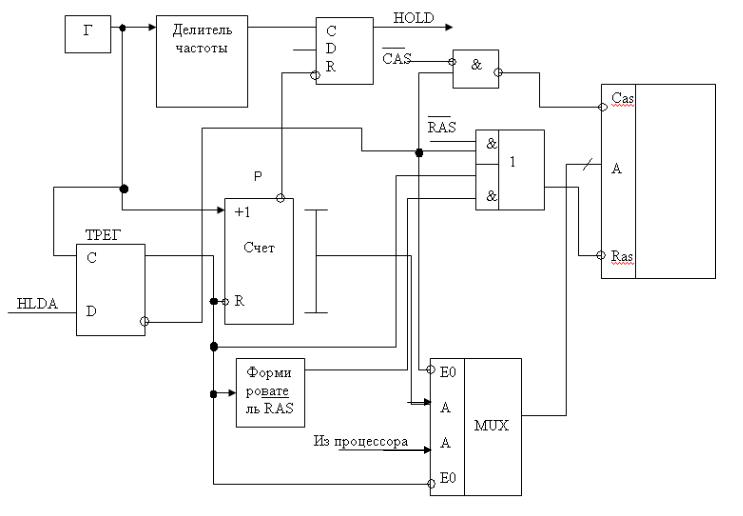

Блок-схема

Генератор вырабатывает импульсы и через делитель частоты организует импульсы запросов на регенерацию процессор. В случае подтверждения устанавливает ТРЕГ=1, разрешая работу счетчика, формирующего адреса регенерации (строк) и сопровождающиеся сигналом RAS. На время регенерации блокируются сигналы RAS и CAS от процессора. Цикл регенерации определяет время работы счетчика и заканчивается по сигналу переполнения. Для подачи адреса строки на модуль используется мультиплексор, управляющий триггером регенерации.

В архитектуре современных компьютеров с шинной организацией, в

которых интегрированная память, контроллер выделен. Схема управления регенерацией организована как во внешнем контроллере, так и частично во внутреннем контроллере (микросхема памяти). Внешний контроллер выдает

только команду регенерации CBR, которая формируется через определенное время, обозначенное циклом регенерации.

Поскольку обращение к памяти к различным ее ячейкам происходит в случайном порядке, то для динамической памяти для сохранности информации необходимы циклы регенерации.

Memory Refresh.

Циклы регенерации могут быть организованы различными способами.

Классическим способом является цикл без импульса CAS, сокращенно ROR (RAS only refresh)

Вторым распространенным способом является CBR (CAS before RAS).

Данный способ в частности используется в SDRAM, т.к. последовательный

ROR в этой памяти воспринимается как команда «АКТ» - активизация строки.

Кроме организации циклов регенерации со стороны внешнего контроллера используется режим само регенерации. Адрес регенерируемой строки берется из внешнего контролера для цикла ROR и из внутреннего счетчика регенерации для цикла CBR. Т.е. для SDRAM адрес регенерируемой строки хранится в самой микросхеме памяти. Активизация циклов CBR из внешнего контролера происходит через определенные промежутки времени.

Само регенерация.

Режим само регенерации организуется в микросхеме при переводе сигнала

CKE(clock enable) в низкий уровень со стороны внешнего контролера.

В режиме само регенерации микросхемы периодически выполняют циклы регенерации по внутреннему таймеру и не реагируют на внешние сигналы,

поэтому внешняя синхронизация может быть остановлена. Причинами остановки синхронизации могут быть следующие обстоятельства:

1) выполнение инструкции HULT в процессоре. В результате процессор переходит в состояние S1

S1 – останавливает таймеры системной платы , но сохраняются данные в системной памяти.