ORGANIZATsIYa_EVM

.pdf

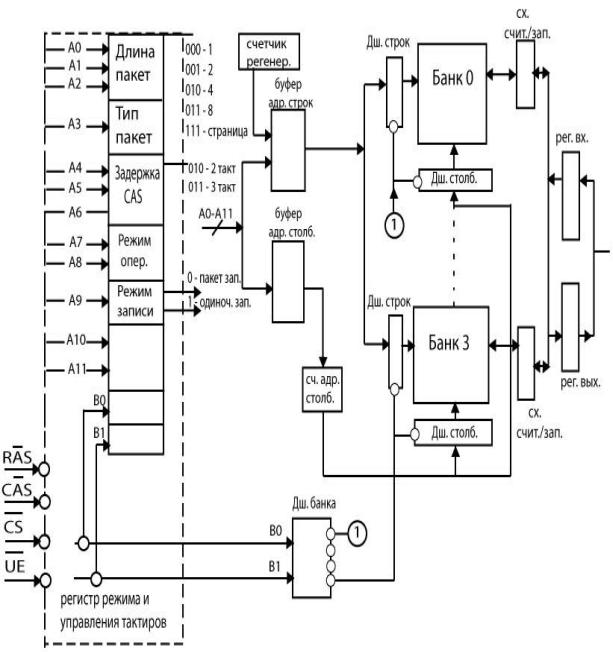

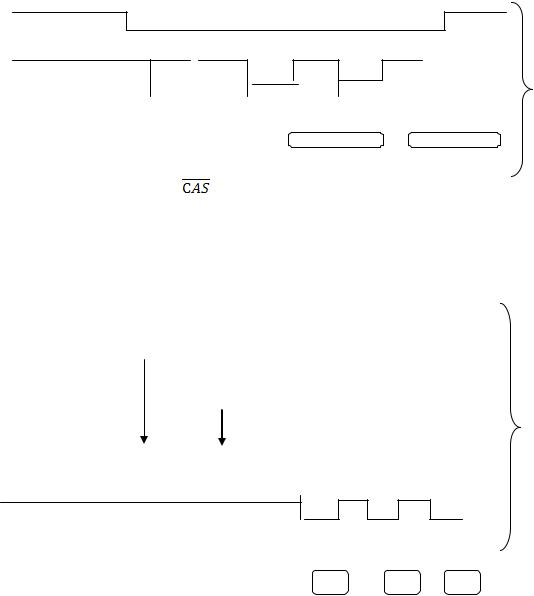

И так - расслоение оперативной памяти.- это метод многомодульного построения с веерной адресацией (чередованием) при которой смежные адреса информационных единиц, соответствующих ширине выборки (слова, двойные слова, и т.д.) принадлежат (размещаются) разным модулям.

Следовательно, размещая четные слова в одном, а нечетные в другом модуле при записи и организуя чтение их одновременно, при выборке получим в случае последовательного обращения по адресам увеличение производительности работы памяти. При этом будет необходим коммутатор

(мультиплексор) который будет выдавать по системную шину требуемое слово.

Рег адр чтен

|

|

|

|

|

|

D |

MUX |

|

|

|

|

|

|

Модуль |

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

чет |

|

|

|

|

|

1 |

|

|

|

|

||

|

|

А |

|

адресов |

|

|

|

|

|

|

|

D |

|

|

|

D |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рег адр зап |

Модуль |

D |

||

|

|

|

нечет |

|

|

|

|

адресов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема

выбора

модуля

Чтение/запись

Средства повышения быстродействия памяти

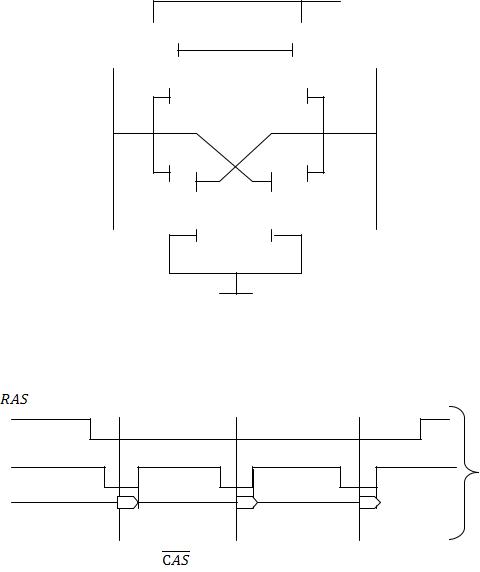

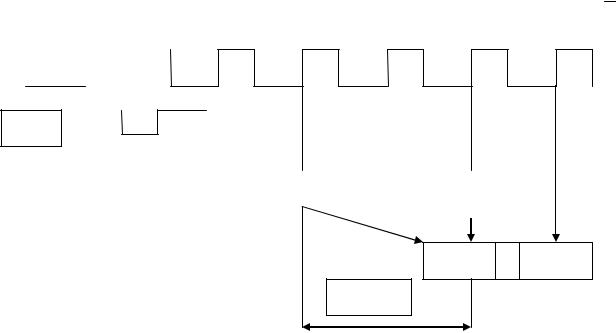

Как следует из анализа работы схемы, и временной диаграммы работы

памяти строка находится в активном состоянии на протяжении всего времени длительности сигнала  , а величины потенциалов

, а величины потенциалов  определяются значениями выходов триггера усилителя - регенератора пока на него подаѐтся

определяются значениями выходов триггера усилителя - регенератора пока на него подаѐтся

питание во время длительности Ф2.

V

ЛЗСА |

|

|

|

|

ЛЗСВ |

|

|

|

|

||

|

|

Ф2

Ф2

И так если предположить, что оставляя состояние  длительное время, строка будет активной и Ф2 зафиксировать на триггере, а подавая серию

длительное время, строка будет активной и Ф2 зафиксировать на триггере, а подавая серию  , и

, и

адреса столбцов в модуль памяти, получим увеличение быстродействия. Именно в таком режиме работает FPM.

|

FPM |

CAS |

|

счит.данных |

|

Частота следования |

, определяет время необходимое для передачи данных |

из памяти в процессор.

Так вот если ввести буферный регистр, который будет сохранять данные, то частоту следов.  можно увеличить.

можно увеличить.

RAS

CAS

шА

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

row |

|

|

|

col1 |

|

|

col2 |

|

|

|

|||

ШД |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

date1 |

|

|

date2 |

||

|

|

|

|

|

|

|

|

|||||||

В памяти ЕДО серия |

поступает из контроллера памяти в модуль. |

|||||||||||||

Дальнейшее увеличение быстродействия было реализовано BEDOBest External Data Out путѐм введения в модуль счѐтчика  число импульсов которого определяется длинной пакета, а адрес колонки передается в память

число импульсов которого определяется длинной пакета, а адрес колонки передается в память

только при первом обращении.

RAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ВЕDО |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

. |

row |

|

|

col1 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|||||||||||||||

ША |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

внутрен счетчик cas

шина данных

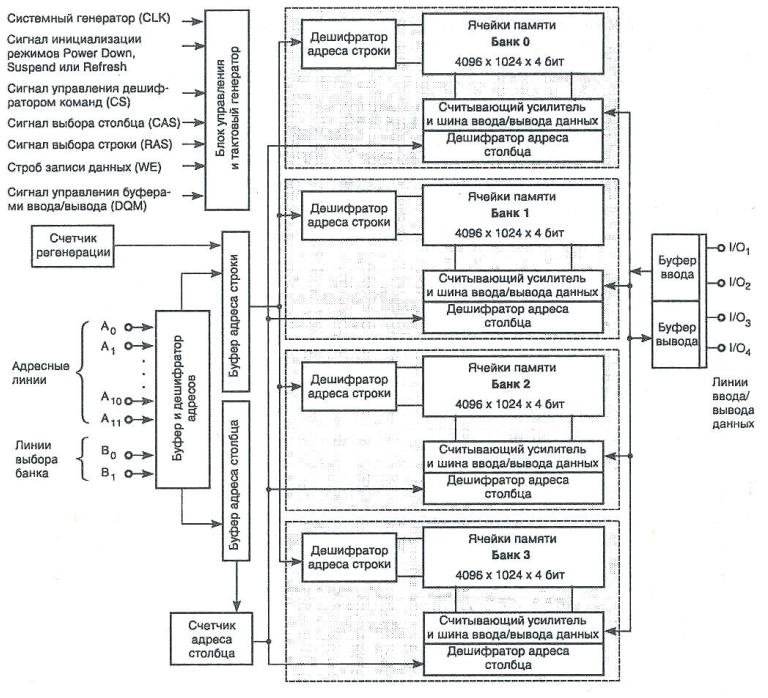

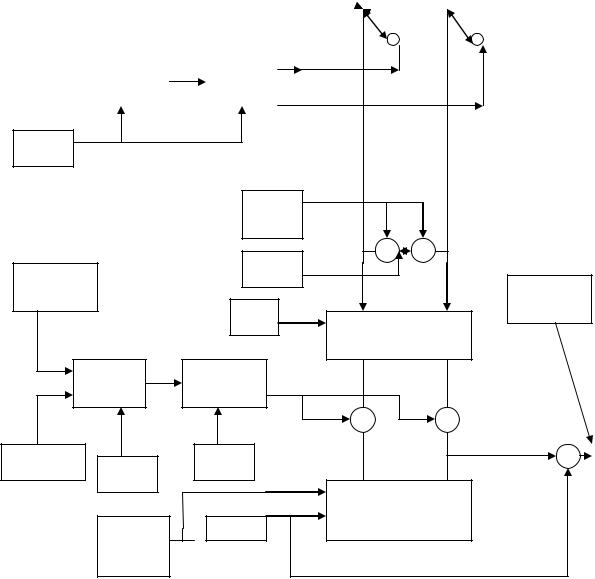

Архитектура памяти SDRAM.

Хотя SDRAM содержит внутри память DRAM, работающую как EDO, принцип управления модулем SDRAM совершенно другой, а улучшение производительности достигнуто путем “ скрытой” внутренней работы DRAM специальными методами по другому внедрением аппаратных средств, а именно:

1.Синхронизация всех операций в памяти тактовой частотой системной шины .

2.Разделение микросхемы SDRAM на внутренние банки (логические)

. Такое решение позволило реализовать режим чередования страниц, давший возможность исключить задержки, связанные с регенерацией, и организовать непрерывность потока данных. 3.Конвейерная обработка данных позволила производить обращение по новому адресу столбца в каждом тактовом цикле, кроме того подобно EDO микросхема SDRAM имеет внутренний счетчик потока, определяющий количество слов в потоке, и устанавливаемый из регистра режима.

4.Регистр режима предназначен не только для хранения размера потока но и информации о типе потока(последовательное считывание или с чередованием) то есть SDRAM является устройством с программируемыми параметрами, которые и заносятся в выше упомянутый регистр.

Запись в него осуществляется в специальном цикле из внешнего контроллера памяти, данные передаются по адресной шине. После такта записи в регистр режима следует обязательно пустой такт NOP. По окончании двух тактов инициализации начинается цикл обращения к памяти с команды “активизация”, во время

выполнения которой из внешнего контроллера в SDRAM передается адрес внутреннего банка по шинам адреса и адрес строки в банке. Указав на архитектурные особенности SDRAM,остановимся на них подробнее. Ну , во-первых, в архитектуре SDRAM вводится понятие логического банка. Вначале мы упоминали о модульном построении памяти , так вот распространяя выше упомянутую технологию на внутреннюю архитектуру самой микросхемы памяти мы приходим к понятию логический банк.

По сути физическая организация микросхемы, в которой хранятся данные (матрица) в случае организации логических банков с технологической точки зрения можно представить как набор независимых друг от друга матриц ,на которые разрезали одну большую матрицу микросхемы ,сохранив подачу одних и тех разрядов адреса строк и колонок на их дешифраторы, дополнительно подавая значения номера банка для активизации суббматрицы ,хранящей информацию того или иного банка.

Возникает вопрос. Так почему же эти внутренние банки микросхемы назвали логическими.

Ответить можно на него ссылаясь, например, на аналогичное понятие как логический диск. Логический диск-это часть дискового пространства(цилиндры или несколько дорожек) физического диска видимых вышестоящему уровню операционной системы как независимый управляемый объект, так же и логический банк, находящийся внутри микросхемы для программы видится как отдельный объект со своей памятью, к которой можно производить обращение.

Такое разрезание сделало независимыми строки разных банков, что позволило открывать последовательностью команд “активизация” их в банках в каждом цикле работы памяти и производить независимые обращения .

Если внешний контроллер “знает,” какие данные следует передать в банк, и в каком банке они находятся в случае их размещения в одном и том же физическом банке, то он может организовать обмен данными между логическими банками с задержкой в один цикл.

Буфер |

|

Дешфр |

строки |

|

строки |

|

|

|

С0

ras

Нач.адр. колонок

Буфер

колонк

Счетчик

С2

Дан

зап

v/2

С1

Дшф

колон

С3

w/r

Дан чт

Тригерный

усилитель

Канал записи (ключ 3)

|

|

|

C0 |

c1 |

c2 |

c3 |

c4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ras

row |

|

Col 0 |

|

col 1 |

|

col 2 |

|

|

|

|

|

|

|

Date0 date1

Caslatenc

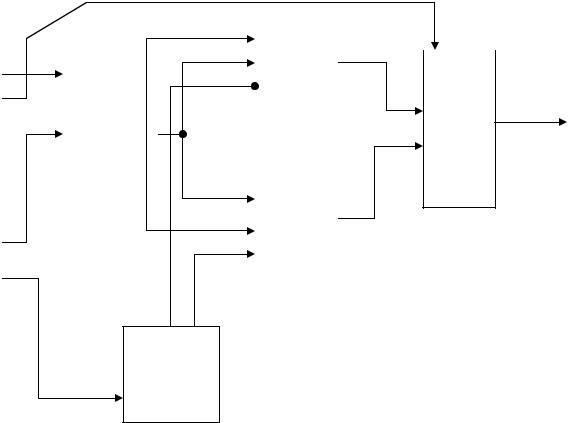

Реализация конвейера при считывании данных из памяти иллюстрируется на вышеприведенной схеме и временной диаграмме. Суть заключается в том что прием адреса столбца в буферный регистр и активизация дешифратора осуществляются двумя сериями синхронизации, смещенными во времени на такт поэтому регистр адреса столбца, передав информацию на входы дешифратора в течение текущего такта, становится свободным для приема следующего адреса колонки к началу фронта следующего синхроимпульса; а в это же время начинается дешифрация адреса предыдущей колонки таким образом данные из памяти будут выдаваться в каждом следующим такте системной шины.

Как видно из схемы для организации пакетного режима из внешнего контроллера необходимо передать адрес первой колонки(начало пакета) и значение загружаемое в счетчик(длину пакета) . Из вышесказанного следует что для организации пакетного режима требуется подготовительная операция ,которая и осуществляется в специальной команде “установка регистра режима”из внешнего контроллера.

Внешний контроллер в свою очередь для реализации протокола связи с модулем памяти имеет свой регистр режима, управляемый как внутренней аппаратной логикой, так и выше стоящим уровнем

(программой) через процессор из которого и поступает тот или иной приказ на установку режима работы.

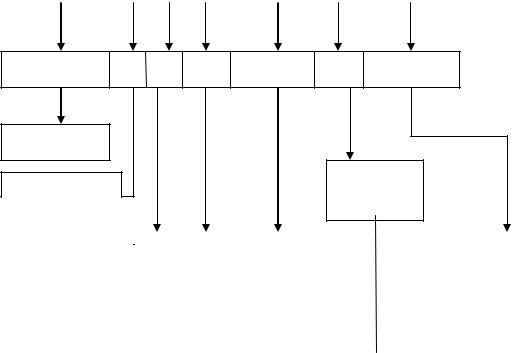

Каким образом осуществляется связь процессора с внешним контроллером памяти мы разберем в дальнейшем, а сейчас отметим то ,что регистр режима внешнего контроллера реализует следующие режимы по коду получаемому из программы или от внутренней логики

сброс(cаморегенерация)-000

nop(нет операции) |

-001 |

все банки закрыть |

-010 |

уст регистра режима |

-011 |

регенерация |

- 110 |

нормальная операция |

- 111 |

A13 A12 A11 |

A10 |

A9 |

A8 A7 |

A6 A5 A4 |

A3 |

A2 A1 A0 |

|

|

|

|

|

|

|

BA1 BA0 |

AP |

WB |

mode |

Cas latence best |

lenght |

N банка |

|

|

|

|

|

1- автопредзар |

|

|

|

0-последов |

|

|

|

|

1-чередов |

||

|

|

|

|

||

|

10-пакет.чт/одиноч.запись |

|

|

000-резерв |

|

|

000-1 111-страница |

00-пакет.чт/пакет.запись |

|

|

001-2такта |

|

|

001-2 |

|

|

|

|

|

010-3такта |

|

|

010-4 |

|

|

|

|

011-111 |

|

|

011-8 |

|

|

|

|

||||

|

|

|

|

резерв |

|

|

100-110 резерв |

|

|

|

|

|

|

|

Поле устанавливает |

|

|

|

|

|

|||

|

|

|

|

|

|

|

длину пакетного |

|

0-послед считыв. 1, 2,3,4.5,6,7,8 |

|

|

|

|||

|

|

|

|

цикла в соответствии |

|||

|

1-чередов.при работе счетчика используется |

|

|

||||

|

|

|

с которым работает |

||||

|

иверсное значение первого разряда при этом |

|

|

||||

|

|

|

внутренний счетчик |

||||

|

порядок считывания будет 2,3,0,1,6,7,4,5 |

|

|

||||

|

|

|

cas. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|