ORGANIZATsIYa_EVM

.pdf

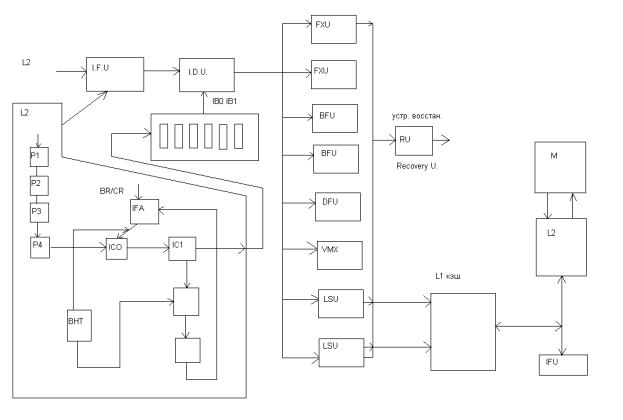

Архитектура микропроцессора Z990

Прежде чем рассматривать архитектуру микропроцессора Z990, необходимо отметить, что данная архитектура явилась результатом эволюции развития серверов предшествующих поколений, родоначальником которых была серия манфреймов IBM360. Особенностью этой серии была CISC архитектура ,которая определяла структуру и форматы команд, реализуемых в процессорах этой серии . Кроме того эти процессора достаточно развитую аппаратную систему диагностики и восстановления работоспособности процессоров ,поддерживаемую на программном уровне специальными системными командами. Хотя эти процессора не были суперскалярными и выполняли только одну инструкцию за цикл, но имели достаточно высокие показатели и характеристики при выполнении сложных CISC команд за счет наличия дополнительных аппаратных средств(акселераторы, блоки логических операций) и мощную систему памяти ,включающую буферные памяти команд и аппаратные средства поддержки преобразования логических адресов в физические.

Внедрение принципов RISC архитектуры при проектировании процессора сопровождалось разработкой и появлением новых языков программирования C, C++, Java, которые использовались для написания программных приложений для пользователей. Для того чтобы сохранить возможность выполнения уже ранее разработанных приложений и новых разработчики архитектуры процессора решили совместить как технологию суперскалярности, так и возможность выполнения сложных команд CISC архитектуры.

При разработке архитектуры микропроцессора были учтены и использованы достижения и наработки в предшествующих моделях процессоров. Это в первую очередь использование милликодов и аппаратные средства восстановления работоспособности системы при возникновении сбоев. Кроме того в микропроцессореZ990 подобно его предшественникам используется дублирование функционирования основных узлов процессора и содержится несколько механизмов для трансляции его состояния в резервный процессор в случае фатальной ошибки.

В микропроцессоре рассматриваемой архитектуры не используется технология безупорядочного выполнения команд, что является отличительной особенностью от других RISC процессоров. За счет этого была сокращена аппаратная часть микропроцессора поддержки этого режима и ее место заняли схемы дублирования основных узлов и восстановления при возникновении ошибок.

Одним из оригинальных решений при проектировании было решение сохранить использование милликода, который использовался еще в предшествующих моделях.

Для того, чтобы понять, что из себя представляет милликод и как он используется в процессоре, напомним, что существуют два основных метода

реализации команд в процессоре. Это микропограммное управление ижесткая логика.

Большинство команд в микропроцессореZ990 реализуется аппаратными средствами, т. е. использует жесткую логику и только сложные команды используют милликод.

Если рассматривать архитектуру микропроцессоров ,например, линейку микропроцессоров PENTIUM фирмы INTEL ,то можно отметить, что при реализации сложных команд ,когда дешифратор не справляется с декодированием инструкции в микроинструкции там используется, так называемый, микрокод ,хранящийся в постоянной памяти микропроцессора , который можно интерпретировать как элемент микропрограммного управления.

С точки зрения методологии подхода к реализации сложных команд нет разницы ,,но отличие заключается в том, что INTEL использовала микроинструкции ,имеющие свою специфичную структуру и формат, а IBM стандартные команды с вертикальным кодированием, таким образом милликод также как основной набор команд выполняется на тех же аппаратных средствах, это во первых. А во-вторых, функциональные возможности милликода намного шире ,чем системные команды, то есть при входе в режим выполнения милликода его рутинам доступны аппаратные средства, которые не доступны даже системным командам.

Размещается милликод ,точнее его рутины в системной памяти в определенной области ,в которую запрещен доступ системным командам и загружается в эту область во время инициализации системы по включению питания то есть эта область по сути выполняет функцию памяти микропрограмм.

И так, отказавшись от технологии микропрограммного управления, IBM сохранила ее метод управления вычислительным процессом за счет 1 Использования особого режима во время выполнения милликода.

2 Расширения функциональных возможностей, что позволило реализовать не только интерпретацию сложных команд, но и выполнять сервисные функции в процессоре, связанные с диагностическими операциями и реализацией механизмов прерывания.

Применение милликода в процессоре позволило разработчикам серверов перенести часть функций при реализации виртуального режима в них с системного уровня на аппаратный и именно этот факт стал при реализации технологии логических партиций LPAR в серверах фирмы IBM, то есть многооперационных систем на одной аппаратной платформе.

Выборка инструкций и блок предсказания переходов.

Доступ к кэш памяти инструкций по времени занимает 3 цикла конвейера в течении которых формируется запрос в кэш инструкций со стороны устройства выборки инструкций и передача выбранных инструкций в буферные регистры. Обычно эти циклы скрыты и не влияют на производительность процессора так как выборка инструкций из кэш производится с опережением, и была еще использована в свое время в отечественных ЭВМ серии ЕС начиная с ряда2.

В тех случаях когда текст инструкции необходимо декодировать немедленно, то она ,минуя буфер, передается на декодер(случай перевыборки, связанный с командой перехода,.когда целевая инструкция отсутствует в буфере команд)

Устройство выборки имеет 16 буферных регистров, каждый с разрядностью в 4 слова.

Логика предсказания переходов содержит буфер целевых адресов, строки которых содержат, бит предсказания, целевой адрес и адрес самой команды перехода. В случае отсутствия информации в буфере для данной команды перехода принимается решениенет перехода на целевой адрес.

Помимо этого буфер переходов целевого адреса содержит “историю” переходов, указывая, что на данный момент наиболее вероятен “сильный”,”слабый”или отсутствие перехода в зависимости от величины счетчика переходов.

Декодирование и формирование групп.

Декодеры инструкций могут декодировать любой тип инструкций. Большинство инструкций декодируется в одном цикле. Однако, наиболее сложные требуют более одного цикла для декодирования, к таким, например, относятся двухадресные инструкции, указывающие на расположение операндов в памяти.

Большинство других инструкций декодируются вместе, объединяясь в группу с одним исключением: инструкция перехода должна быть старшей в группе.До трех инструкций может входить в группу.

Совместно с командой перехода, которая является старшей в группе, могут находиться простые, выполняемые за один такт, к которым относятся логические и арифметические операции.

Идея размещения команды перехода старшей в группе связана с тем, что на первый взгляд является парадоксальной, так как эти команды предназначены для анализа признаков результатов от предыдущих команд. Однако выбранная схема при отсутствии безупорядочного выполнения, то есть в

порядке следования программному коду дает возможность получать результат перехода в одном цикле с проверяемой командой так как она выполняется в предыдущей группе программного кода.

Во время формирования групп могут иметь место факторы ,которые ограничивают их эффективное выполнение в процессоре и препятствуют включению инструкций в группу. Так ,например ,одним из условий является , что генерация адреса обращения к памяти должна быть завершена до того или в том цикле ,в котором соответствующая инструкция ,использующая этот адрес, включается в группу для исполнения. Кроме того ,если инструкция имеет зависимость при формировании адреса от инструкции уже распределенной в группу,(старшая инструкция производит операцию над базовым или индексным регистрами, являющихся составной частью адреса операнда) то она не включается в группу.

Такие зависимости как RAWв группе между инструкциями запрещены ,с одним исключением .Если такая зависимость существует между инструкциями типа LOUD,выполняющей загрузку данных в регистр из памяти или из другого регистра регистрового файла, а другая использует загружаемый регистр как источник операнда в арифметической или логической операции, то такая комбинация разрешена в группе. Путем простого изменения маршрута на вход исполнительного конвейера продвижение операнда может быть реализовано с минимальными потерями.

Конвейеры операционных устройств

После формирования групп инструкции поступают в исполнительные устройства.

B-конвейер предназначен для определения в действительности будет переход в программе или нет.

Х конвейер выполняет простые инструкции и инструкции милликода .

Yконвейер выполняет простые инструкции.

Zконвейер содержит специальные аппаратные средства для выполнения сложных инструкций, включая операции умножения с фиксированной точкой и десятичную арифметику.

В других случаях при необходимости формируется виртуальный конвейер для обработки 16 байтного потока данных(пересылка символов и операции память-память).

FPU конвейер выполняет операции с плавающей точкой.

Лекция 16

Тема лекции: Мультипрограммный режим работы ЭВМ.

1. Общие принципы организации мультипрограммного режима.

2.Программно аппаратные средства поддержки мультипрограммного режима.

В основу мультипрограммного режима работы ЭВМ положен принцип одновременного выполнения программ в машине. Определение “одновременный” является чисто условное, так как данный режим был внедрен в архитектуру процессора фон неймановской модели, классифицируемой как SISDодна инструкция, одни данные. То есть процессор в каждый момент времени в данной архитектуре выполняет одну команду и говорить об одновременном выполнении не только программ ,но команд не имеет смысла. Да, впоследствии, с внедрением конвейерной обработки команд в процессоре стало возможным их одновременное выполнение, причем количество одновременно выполняемых команд стало определяться глубиной конвейера и их количества в процессоре. Но это была технология параллельной обработки команд, принадлежащих одной программе, поэтому понятие “одновременный” в мультипрограммном режиме подразумевает только одновременное нахождение программ в системной памяти процессора, готовых в любое время продолжить выполнение при представлении им процессорного времени.

Идеи мультипрограммного режима работы ЭВМ были выдвинуты в результате анализа занятности ресурсов системы в процессе выполнения программ. Выяснилось, что процессор вынужден простаивать, то есть останавливать выполнение программы из за неготовности ее к работе, в частности отсутствия данных в памяти и ожидания окончания операций ввода вывода, когда эти данные поступят в память.

Для того, чтобы увеличить пропускную способность выполнения задач и была разработана концепция организации мультипрограммной обработки в системе, суть которой сводилась к

тому, что при возникновении простоя при выполнении программы представлять ресурсы системы другой.

А для того ,чтобы реализовать это необходимо было ввести в

архитектуру комплекс аппаратно программных средств и это в первую очередь управляющей программы, выполняющей функции диспетчера и контроллера за выполнением программ в процессоре.

Аппаратные средства поддержки многопрограммного режима в ЭВМ

1.Наличие виртуальной памяти для хранения программного кода и данных, представляемой каждому пользователю потребовало специальных аппаратных средств по преобразованию логических адресов виртуальной памяти в физические и разбиение физической памяти на страницыобласти непрерывного адресного пространства . Смысл такого разбиения физической памяти заключается в том ,что и виртуальная память разбивается на такие же по размеру страницы в результате чего операционная система, размещая программы и данные пользователей во внешней памяти системы(диски, ленты), во время выполнения их в процессоре, используя механизм преобразования логических адресов в физические, осуществляет перемещение содержимого виртуальных страниц из внешней памяти в системную. Таким образом, используя концепцию организации виртуальной памяти в системе, пользователям была предоставлена возможность размещения своих программ и данных вне зависимости от размеров реальной физической памяти в системе.

2.Система прерываний и средства переключения задач.

Механизм прерываний существовал и в однопрограммном режиме. Особенностью системы прерывания в мультипрограммном режиме является то , что реакцию на большую часть причин прерываний и их обработку осуществляет не программа пользователя , а управляющая программасупервизор, при этом если прерывание возникло при возникновении ошибки в программе или другой причине не связанной с нарушением работы системы , блокируется только выполнение этой программы с формированием сообщения пользователю о причине останова. Если пользователь в своей программе желает сформировать запрос на прерывание, то в зависимости от среды вычислительной системы ему представляется возможность использования в программе

специальных командкоманд программных прерываний( архитектура intel) или команды обращения к супервизору “вызов супервизора” (в архитектуре ibm). Так, например, при обработке программных прерываний пользователю может быть предоставлена возможность блокировки тех или иных причин прерываний путем их маскирования как это делалось в архитектуре отечественных ЭВМ серии ЕС и в настоящее время в z архитектуре. Что касается механизма переключения задач, то в основу заложен принцип прерывания выполнения программы с той лишь разницей ,что при переключении задач процессор сохраняет при переключении больший объем информации состоянии программы и процессора.

3 Механизм защиты памяти.

Механизм защиты памяти в мультипрограммном режиме необходим, для того чтобы исключить вмешательство как случайное, так и преднамеренное одной программы в другую. Существуют различные аппаратные решения реализации механизмов защиты, наиболее применяемые из них – это Защита с использованием метода верхней и нижней границы области разрешенной памяти, наличие памяти ключей защиты, применение уровней привилегий.

4.Привилегированные команды, которые могут выполняться только на определенных уровнях или при двух уровневой организации в состоянии системы “супервизор”.

5. Средства отсчета времени, которые предназначены для управления выполнением задач в процессоре. Эти средства позволяют контролировать и выделять кванты времени на выполнение задач на аппаратных ресурсах, Супервизор обрабатывает прерывания от таймера, контролирует затраченное время работы процессора по выполнению той или иной программы и по истечении временного кванта размещает на аппаратных ресурсах другую задачу.

Уровни привилегий.

Идея использования уровней привилегий для защиты областей памяти в мультипрограммном режиме была еще реализована в архитектурах ЭВМ второго поколения. Концепция эта используется

всовременных микропроцессорах, примером тому может быть архитектура микропроцессоров фирмы INTEL, и была реализована

ваппаратных средствах механизма сегментации, который помимо использования уровней привилегий для защиты памяти имеет дополнительные возможности и средства ,которые мы и рассмотрим .

Механизм сегментации является основным программноаппаратным средством защиты информации в системной памяти микропроцессоров фирмы INTEL.

При использовании сегментации памяти каждая программа имеет свой собственный набор сегментов, размещаемых в линейном адресном пространстве .Процессор устанавливает границы между этими сегментами, таким образом исключая возможность вмешательства одной программы в другую. Механизм сегментации позволяет классифицировать сегменты по типу и набору разрешенных операций производимых в границах сегмента, то есть расширяет набор средств защиты памяти.

Все сегменты внутри системы содержатся в линейном адресном пространстве. Для локализации байта в конкретном сегменте должен быть сформирован логический адрес, состоящий из селектора сегмента и смещения. Селектор сегмента является уникальным идентификатором, определяющим смещение в дескрипторной таблице, указывающим на местонахождения в ней дескриптора сегмента. Каждый дескриптор определяет размер сегмента ,тип сегмента, права доступа, уровень привилегий, местонахождение первого байта в сегменте (называемым базовым адресом сегмента)

Смещение сегмента складывается со значением базового адреса для определения положения байта внутри сегмента, эта сумма называется линейным адресом.

Процессор транслирует каждый логический адрес в линейный. Трансляция логического адреса в линейный адрес производится в три этапа.