ORGANIZATsIYa_EVM

.pdf

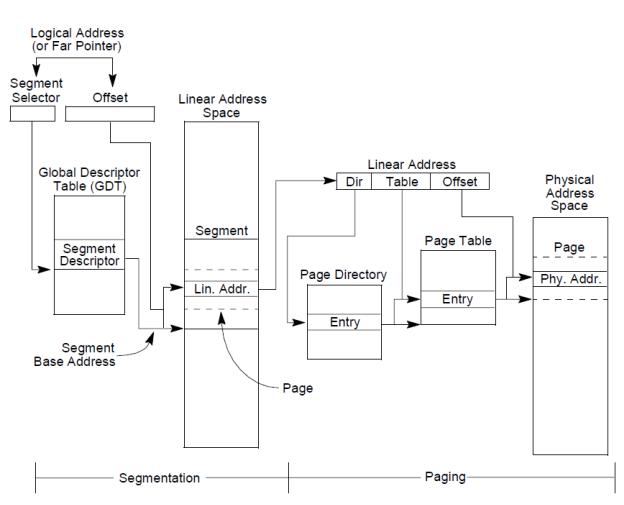

1.Использует смещение в селекторе сегмента для локализации дескриптора сегмента в глобальной или локальной (задачи) дескрипторной таблице и читает содержимое дескриптора в свои регистры.

2.Осуществляет контроль дескриптора сегмента с целью проверки прав доступа к сегменту и проверяет значение смещения с пределом, указывающим размер сегмента.

3.Производит сложение адреса из дескриптора со смещением ,если не обнаружено нарушение защиты, то есть формирует логический адрес.

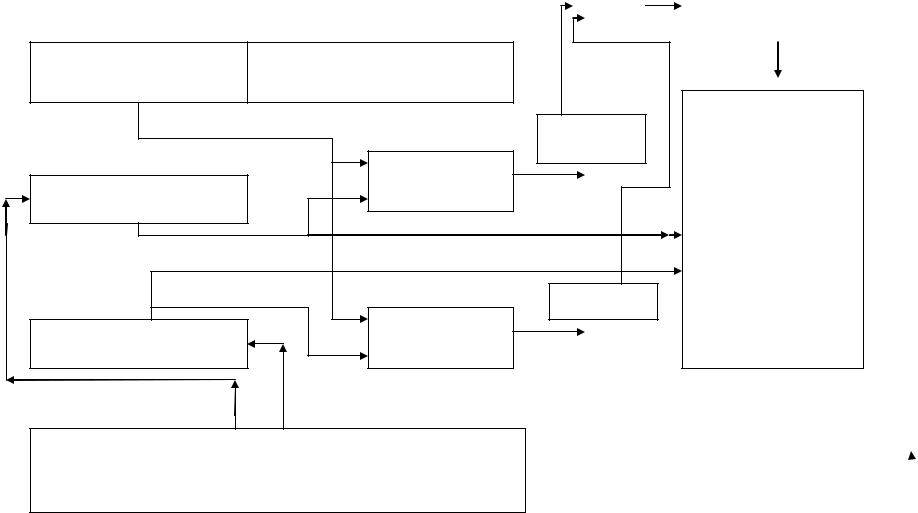

На данной схеме изображены два независимых этапа преобразования логического адреса в физический адрес: сегментация и страничное преобразование. Как видно из схемы сегментация адресов в процессоре не связана с режимом виртуализации системной памяти и полностью возложена на этап страничного преобразования ,то есть механизм сегментации

задействован всегда и в том случае, когда страничное преобразование не используется линейный адрес становится физическим автоматически.

Следует отметить, что в некоторых архитектурах сегментация памяти используется как начальный или промежуточный этап преобразования логического адреса в физический. Примером тому архитектура процессоров фирмы IBM.

|

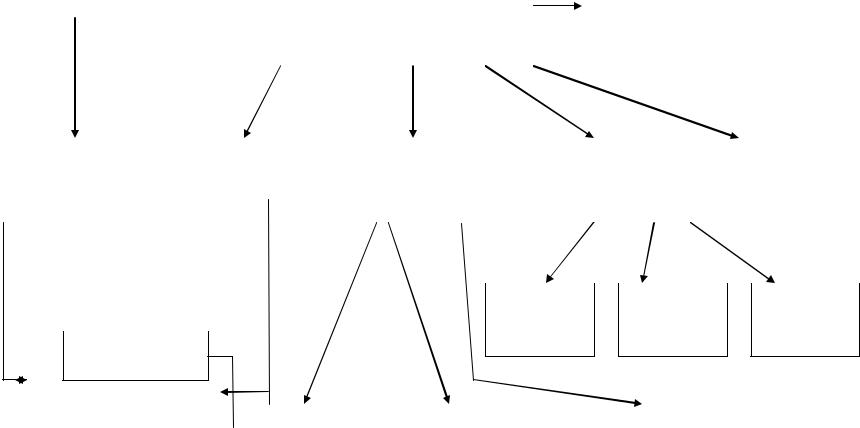

Аппаратные средства |

|

Средства отсчета |

|

поддержки мультипрограммного |

|

времени |

|

|

||

|

режима |

|

|

|

|

|

|

|

|

|

|

Наличие |

|

Механизм |

|

Система прерываний |

|

|

Средства |

|

|

|

|

|

|||||

виртуальной |

|

динамического |

|

И средства |

|

|

защиты памяти |

|

привилегирован |

|

|||||||

памяти |

|

преобразования |

|

переключения задач |

|

|

|

|

|

|

ные команды |

|

|||||

|

|

|

адресов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

базирование |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Метод |

|

|

Память |

|

|

|

Уровни |

|

||

|

|

|

|

|

|

|

Граничных |

|

ключей |

|

|

|

привилегий |

|

|||

|

|

|

|

|

|

|

регистров |

|

|

защиты |

|

|

|

|

|

||

|

сегментирование |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Страничное |

|

|

Переключение |

|

Через PSW |

|

Через команды |

|

преобразование |

|

|

уровней |

|

|

|

CALL B JMP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

.

|

|

|

|

Схема |

Схема |

Регистр |

|

|

Сбой процессора |

|

|||||

|

|

|

приоритета |

преобразо |

номера |

||

|

процессора |

|

|

||||

|

|

|

|

вания |

|

|

|

|

|

|

|

|

уровня |

|

|

|

|

|

|

|

позиц кода |

|

|

|

Сбой внеш устройст |

|

|

|

|

||

|

|

|

в |

|

|

||

|

устройств |

|

|

двоичный |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Сбой канала в/вывода |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Запрос активной консоли

Конец работы внеш устройст

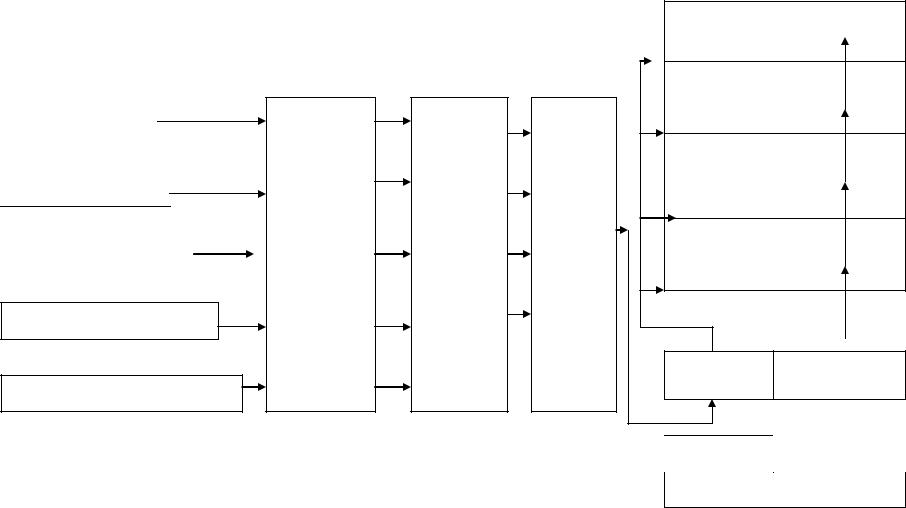

Управляющая область памяти |

|

Нулевого уровня |

|

Управляющая область памяти |

|

Первого уровня |

|

……………………………….. |

|

Управляющая область памяти |

|

N- ного уровня, |

|

Номер уровня номер яч. уров. |

|

Форм аппар |

Из форм команд |

парат |

|

Адрес обращения к памяти |

|

Номер блока |

размер блока |

|

|

|

|

|

системная |

||

|

|

|

|

|

|

|

|

|

память |

Память |

|

|

Комбинационная |

|

|

Схема проверки |

|

|

|

Ключей |

|

|

схема |

|

|

|

|

||

|

|

|

|

ключей на нуль |

|

|

|||

защиты |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

нет |

Кл прог v кл |

|

|

|

|

|

|

|

|

защ=0 |

да |

|

|

|

|

|

|

|

|

|

|

|

|

|

Разряды ключа |

|

|

|

|

|

|

|

Схема сравнения |

|

|

|

|

|

|

|

|

|

ключей |

|

|

|

|

|

Значение бита |

|

|

|

||

|

Разряд |

|

разрешения |

|

|

|

|||

|

|

защиты |

|

|

|

|

|||

|

Разрешения |

|

|

|

|

||||

|

игнорировать |

|

|

|

|||||

|

защиты |

Считывание |

|

равны |

|

||||

|

разрешить чтение |

да |

нет |

||||||

|

|

|

разрешено |

|

|||||

|

|

|

и запись |

|

|

|

|

||

|

|

|

|

|

|

|

|

||

Разряды ключа |

маски |

|

адрес команды |

|

|

|

|

Значен |

|

|

|

Вид |

|

0 |

ие бита |

1 |

|||

|

|

|

|

|

|

||||

|

|

|

|

|

зп |

Разреш |

|||

|

|

|

|

чт |

операц |

|

|

||

|

|

|

|

|

|

ение |

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Слово состояния программы |

Блок |

|

Запрет |

защиты |

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

прерывания |

записи |

|

|

||

|

|

|

|

|

|

|

считывани |

|

|

ИЛИ |

|

Обращение разрешено |

|

|

|

|

|

|

разряды адреса блока [X] |

разряды адреса ячейки в блоке |

X< ИЛИ = A

Схема сравнения

Регистр верхней границы области памяти [рег]=А

X> ИЛИ=И |

Оперативная память |

|

Схема сравнения

Регистр нижней границы

области памяти [рег] =B

Управляющая область памяти уровня хранит значения верхней и нижней границы разрешенной области памяти программы

Лекция N17

Тема лекции: Организация мультипрограммного режима работы ЭВМ.

1.Понятие задачи, структура задачи, структурные данные для управления задачи.

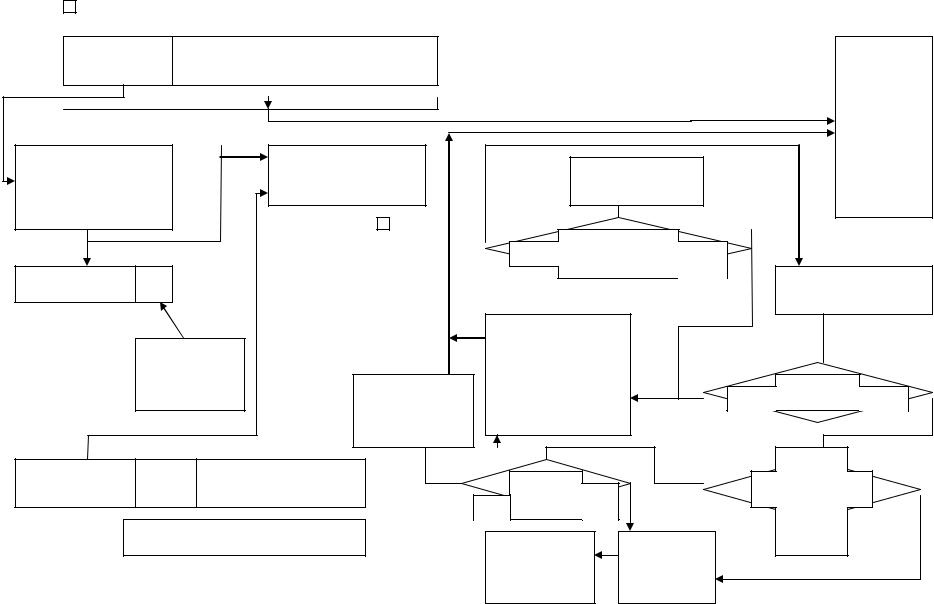

2.Механизм, обеспечивающий переключение выполнения задач в мультипрограммной среде вычислительной системы. Для организации мультипрограммного режима работы вычислительной системы ее архитектура содержит аппаратно программные средства ,как уже упоминалось выше.

Для того чтобы рассмотреть подробно организацию выполнения задачи, переход от одной задачи к другой в качестве примера рассмотрим, как это реализуется в механизме переключения задач в процессорах INTEL. Архитектура процессоров INTEL в составе имеет блок сегментации, который в свою очередь не только организует механизм защиты доступа ко всем структурным данным, расположенным в виртуальной памяти, но и реализует доступ к ним в соответствующих сегментах. Поэтому, переключение задач , cвязанное с доступом к памяти также использует блок сегментации , используя при этом соответствующие структуры системных данных и дескрипторы, определяющие их специфику и расположение в виртуальной памяти.

И так прежде чем рассматривать работу этого механизма, сформулируем определение задачи , ее структуру и структуры системных данных для ее управления.

Задача – это единица работы которую процессор может активизировать ,выполнять и задержать выполнение. Эта структура может быть использована для выполнения программы, задания или процесса, сервисной утилиты

операционной системы ,обработки прерывания или исключения.

При работе процессора в защищенном режиме все действия процессора трактуются как действия внутри задачи то есть в самом простом варианте функционирование системы представляется как выполнение, по крайней мере одной задачи. В случае выполнения нескольких задач включается программно аппаратный комплекс для их переключения.

Структура задачи.

Задача состоит из двух частей: - область выполнения сегмент состояния задачи

Область выполнения включает сегмент кода, сегмент стека один или более сегменты данных.

Сегмент состояния задачи используется для ее выполнения и является местом записи ее текущего состояния при переключении в мульти программном режиме.

Состояние задачи определяется:

областью текущего выполнения, которая представлена сегментными селекторами в сегментных регистрах состоянием регистров общего назначения состоянием регистра флагов

состоянием управляющего регистра, в котором хранится физический адрес каталога страниц содержимым регистра задачи

содержимым регистра локальной дескрипторной таблицы, в котором находится селектор, указывающий на строку в глобальной дескрипторной таблице . В этой строке размещается базовый адрес локальной дескрипторной таблицы , оформленной как системный сегмент.

Базовым адресом карты ввода вывода Звеном к предыдущей задаче

Стеком указателей к уровням привилегий 0,1, 2 Структуры данных для управления задачи представлены

Сегментом состояния задачи Дескриптором шлюза задачи Дескриптором сегмента состояния задачи Регистром задачи

Флагом вложенной задачи в регистре флагов

Сегмент состояния задачи Информация состояния процессора необходимая для

восстановления задачи при переключении хранится в сегменте состояния задачи, в который эта информация была записана ранее в момент прерывания.

Помимо выше указанной информации о состоянии задачи в сегмент состояния задачи записывается адрес текущей инструкции и содержимое регистра флагов.

Рассматривая в свое время многоуровневую организацию памяти в вычислительной системе , мы отметили об использовании виртуальной памяти как об одном из средств поддержки организации мультипрограммного режима в системе. Мы уже говорили ранее, что при использовании технологии виртуализации системной памяти используется механизм преобразования логических адресов в физические. Следует помнить, что в архитектуре процессоров фирмы INTEL блок сегментации не является частью механизма преобразования логических адресов памяти в физические. Он является частью аппаратных средств системы для организации сегментированной виртуальной памяти, в которой она представлена системе набором сегментов - непрерывных областей памяти различного размера, доступ к которым осуществляется через дескрипторы, организованные в таблицы.

Доступ же к ним осуществляется через селекторы, которые находятся в соответствующих регистрах сегментов кода, данных и стека.

Мы еще будем разбирать , когда и каким образом селекторы загружаются в соответствующие регистры сегментов, а сейчас разберем форматы и типы дескрипторов.

Код тип дескрипторов

11.10.98

0 0 0 0 – резерв.

00 0 1 – 16 бит. TSS (доступен)

00 1 0 – LDT

00 1 1 – 16 бит. TSS (занят)

01 0 0 – 16 бит. Шлюз вызова

01 0 1 – шлюз задачи

01 1 0 – 16 бит. Шлюз прерыв.

01 1 1 – 16 бит. Шлюз пов.

10 0 0 – резерв.

1 0 0 1 – 32 бит. TSS (доступен) 1 0 1 0 – резерв.

1 0 1 1 - 32 бит. TSS (занят)

1 1 0 1 – резерв.

1 1 1 0 - 32 бит. Шлюз. прерыв. 1 1 1 1 - 32 бит. Шлюз пов.

Типы системных дескрипторов.

Когда S ( тип дескриптора ) установлен в дескриптор является системным. Процессор распознает следующие типы дескрипторов.

1.дескриптор LDT

2.дескриптор TSS

3.дескриптор шлюза вызова

4.дескриптор шлюза ловушка

5.дескриптор шлюза задачи

6.дескриптор шлюза прерывания

Эти дескрипторы разделяются на 2 категории:

1.Системные дескрипторы, указывающие на вход к системным сегментам ( LDT и TSS )

2.Дескрипторы шлюзов, которые содержат сами указатели к точкам входа в процедурах в сегментах кода и селектора их дескриптора.

Дескрипторные сегментные таблицы – область сегментных дескрипторов. Дескрипторная таблица может быть различных размеров и может содержать до 8192 (2^13) 8 байтные дескрипторов.

Различают 2 вида таблицы LDT и GDT. Каждая система должна иметь одну GDT, которая может быть использована для всех программ и задач в системе, в то время как одна или больше LDT может быть определено. Например LDT может быть назначена для каждой отдельной задачи или несколько задач могут иметь ту же самую LDT . GDT не является сама сегментом, т.е. она является структурой данных в линейном адресном пространстве. Базовый линейный адрес и предел GDT должен быть выровнен по 8 байтной границе. Величина предела для GDT выражается в байтах также как и для сегментов. Limit + база адрес определяет послед байт достоверный в таблице.