- •Глава I

- •06Ласти применения эвм

- •1.6,1. СуперЭвм

- •Глава 2

- •8 Разрядов

- •11110001 11111001 11110001 11110111 А число — 6.285 запишется в память в виде слова из 6 байт:

- •Глава 3

- •Глава 4

- •Лечит узап j

- •Сверхоперативная или местная память

- •4.2. Адресная, ассоциативная и стековая организации памяти

- •Буфер входа-выхода

- •Усилители считывания-записи

- •Глава 5

- •Проклей

- •Идентификатор адреса (s байт)

- •Сектор на дискете

- •Глава 6

- •Управляющий блок автомат)

- •Глава 7

- •В цпршВляющай блок у б

- •Сумматор частичных произведений Регистр множимого

- •О vМножимое перед началом Выполнения умножения

- •Слой элементов и

- •Глава 9

- •Двойное слада па адреса о 32 бит

- •Слобо по адресу z в бит

- •Заслать в стек ад РеЗ

- •Загрузить аз стана в Pa V

- •Номер регист

- •Непосредственный операнд 1а

- •15Ю кГго 51

- •Оповещающий сив нал „Состояние

- •Блок ревастрод

- •Ветвление в макропроерамме по уело дую Акк*0

- •Макрокоманды управления последовательностью выборка микрокоманд

- •Окно процедуры

- •Регистры параметров (а) Регистры глобальных переменных |

- •1 Нуль м Знак-

- •Запоминание состояния процессора (программы)

- •Общий сигнал прерывания

- •Код приоритетного запроса

- •Маска ввоОагвывода

- •Прерывающая

- •01 23*56789 Время

- •I участка I

- •Запись льта мп

- •I Прием операндов на регистры 1

- •Умножение чисел с фиксированной точкой

- •Сложонив чисел с плавающей точкой

- •Глава 10

- •Вызов команды и модификация счетчика команд

- •Процедура тандемных пересылок

- •Однобайтная

- •16 Разрядов

- •Передача д стек а восстановление содержимого регистров

- •Команды досстаяовяения из стеки содержимого регистров

- •Блок сегментных регистров

- •Первый байт команды Второй ffaSm команды (постбайт адресации)

- •Сегментные селекторы

- •Регистры задачи и регистры дескрипторнои таблицы

- •Блок управления и контроля оп

- •Справочник страниц

- •Физическая память

- •16 Мбайт

- •Расширенная память

- •1 Мбайт

- •С каналом ес эвм

- •Связь с другой эвм

- •I Манипулятор % I Графа- I I типа „Мышь” I I построитель I

- •Глава 11

- •Интерфейс основной намята

- •Общее оборудование мультиплексного канала

- •Глава 12

- •Определения четности переносод

- •Глава 13

- •Ill:Выполнснис программы а Выполнение про ерам мы в

- •Пакеты заданий и Входные наборы данных

- •Выходные очереди разных классов в зу на дисках

- •I требует ‘'ода

- •Пользователь обдумывает | ответ системе I (новый запрос)

- •Блок управления памятью

- •Схемы совпадения

- •Шифратор номера отделения

- •Входной коммутатор

- •Коммутации

- •Сегментная таблица п-й программы

- •Векторные, средства

- •К периферийным устройством

- •К периферийным устройствам

- •Глава 15

- •Устройства Ввода- вывода

- •Процессор 2

- •Процессор 3

- •8 Векторных регистров (по 6* слова в каждом)

- •Готовности операндов

- •Глава 16

- •Комплекс абонентского пункта

- •16.2.. Классификация вычислительных сетей

- •1 Элемент

- •Время распрост- ранена*

- •Задержка сета лри коммутации пакетов[

- •Абонентская система

- •Данные пользователя

- •Сеансовый

- •Транспортный

- •Сетевой

- •Интерфейс высоког о уровня

- •Аппаратура передачи данных

- •Установление связи

- •Данные пользователя 00Длина поля и слови я обслуживания

- •Идентификатор протокола

- •7» Бшдта) Данные пользователя б вызове

- •Поток бит

- •Новый пакет (кадр)

- •Станция 1 ведет передачу

- •Передатчик Коаксиальный кйбель

- •Глава 15. Принципы организации многопроцессорных и многомашинных вычислительных систем (комплексов) и суперЭвм 489

- •1S в 7 о Слада па адресу ь

Процессор

Процессор

Процессор

Векторные

сродства

Процессор

Блок

управления системой

Блок

управления системой

Векторные, средства

|

Канальная |

|

Канальная | |

|

система |

|

система | |

|

ввода-вывода |

|

ввода-вывода | |

|

|

:l -1 |

tt-t | |

|

' v |

|

* ' | |

К периферийным устройством

К периферийным устройствам

Рис. 14.11. Структура ЭВМ общего назначения IBM 3090

Рис.

14.12. Структура процессора ЭВМ IBM

309,0

блок (блок /) и исполнительный (блок Е).Эти блоки связаны друг с другом и со скрытой (недоступной программисту) кэш-памятью. Блоки / иЕвыполнены с использованием конвейерной обработки и перекрытия, так что в рассматриваемом процессоре реализован конвейер команд (одновременная обработка четырех команд) и арифметический конвейер. В блокеЕприменено микропрограммное управляющее устройство (длина микрокоманды свыше 100 разрядов) с управляющей памятью, допускающее считывание и с меньшей скоростью запись.

В блоке / используется буфер для предварительной выборки команд, хранения очереди четырех декодированных команд вместе с их операндами и согласования скоростей работы блоков / и Е.

Средства векторной обработки каждого центрального процессора включают в себя конвейерное арифметическое устройство и набор из 16 векторных регистров по 128 32-битных элементов в каждом. Эти средства реализуют 171 векторную команду. Они являются дополнением / к набору команд системы IBM 370. При заполненности конвейера время обработки пары операндов (элементов двух векторов) близко к одному машинному такту, причем, чтобы снизить время операции умножения до одного такта, применен подконвейер из трех множительных устройств, поочередно загружаемых парами перемножаемых элементов векторов.

Кэш-память в IBM 3090 представляет собой быстродействующую память-буфер емкостью 64 Кбайт с временем обращения 2 машинных такта. В системеIBM 3090 а целях повышения быстродействия отказались от одновременной записи информации в кэш- и основную память (так называемой кэш типаstore-through). Новая информация записывается только в кэш (кэш типаstore in cache}, при этом исключается цикл более медленной центральной памяти, но возникает проблема выравнивания (актуализации) содержания центральной памяти. «Строка» (единица информации размером в четыре двойных слова, которыми обмениваются кэш-память и центральная память) передается из кэш-памяти в центральную память только в том случае, если ее запрашивает другой процессор или надо освободить место в кэш-памяти. С привлечением второго БУС возможен прямой обмен информацией между кэш-памятями процессоров, принадлежащих разным ЭВМ модели 3090/200, объединенным в систему 3090/400.

Канальная система.Каждая из машин, входящих в составIBM 3090/400, имеет собственную канальную систему. Необходимость приведения в соответствие пропускной способности системы ввода-вывода со значительно увеличившимися скоростью работы процессорной части и пропускной способностью центральной памяти (в условиях сравнительно медленного увеличения скорости передачи данных у внешних ЗУ и других ПУ) потребовала увеличения числа каналов ввода-вывода. Так, в каждой из двух канальных системIBM 3090/400 число каналов может достигать 48.

При увеличении числа каналов значительно возрастает объем операций по управлению вводом-выводом, в результате чего особую остроту приобретает проблема более полного освобождения процессора от процедур, связанных с вводом-выводом. Тот уровень освобождения процессора от этих процедур, который достигнут в выпускаемых в настоящее время машинах общего назначения (см. гл. 11), оказывается в данном случае недостаточным. Там процессор освобождается главным образом от управления реализацией канальных программ, что, конечно, весьма существенно. Однако во многих случаях часть аппаратуры процессора, например управляющая память, используется процессором и каналами на основе разделения времени, что снижает производительность процессора. Кроме того, инициализация любой операции ввода-вывода сопровождается переходом ЭВМ в режим супервизора (по команде «Вызов супервизора») и выполнением процессором программы «супервизор ввода-вывода».

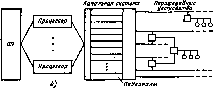

В новой системе ввода-вывода IBM 3090 достигается существенное освобождение процессора от процедур, связанных с операциями ввода- вывода. На рис. 14.13, заимствованном изffO], сопоставляются (применительно к двухпроцессорным комплексам) структуры существенно различающихся существующей(а)и новой(б)систем ввода-вывода.

В новой, «канальной системе» процедуры, связанные с выполнением канальных программ и управлением интерфейсом ввода-вывода, выполняют каналы, представляющие собой микропрограммируемые процессоры с управляющей памятью, допускающей запись микропрограмм для задания нужно комбинации байт- и блок-мультиплексных каналов и их режимов работы. Вся Канальная система управляется микропрограмми- руемым процессором ввода-вывода («директором каналов») с сокращенным набором команд [с RISC-архитектурой (см. гл. 9)], которые при лнициализации процессором операции ввода-вывода выполняют своими микропрограммными средствами функции «супервизора ввода-вывода», организуют очереди запросов ввода-вывода, управляют выбором маршрутов передачи информации в системе ввода-вывода (в условиях многовариантности этих маршрутов), формируют запросы прерывания, осуществляют динамическое повторение операции ввода-вывода при ошиб

ках. В канальной системе используется логическая адресация периферийных устройств, не зависящая от маршрута передачи данных. Сами маршруты могут меняться на разных этапах выполнения одной и той же цепочки операций.

Рис.

14.13. Сопоставление структур систем

ввода-вывода: а

— существующая система ввода-вывода

машин общего назначения; б

— «канальная

система» в IBM

3090

Контрольные вопросы

Для чего предназначена кэш-память? Каким образом автоматически устанавливается наличие запрашиваемой процессором информации в кэш-памяти?

Какие существуют режимы защиты и в чем их различие? Почему время обращения к памяти ключей защиты должно быть существенно меньше времени обращения к ОП?

Поясните, как в схеме на рис. 14.6 реализуется конвейерная обработка запросов на доступ к ОП?

Каким образом сегментно-страничная виртуальная память способствует более эффективному использованию ОП и облегчает труд программистов?

Почему в устройстве быстрого преобразования адресов оказалось необходимым использование ассоциативной памяти?

В чем различие физически реализуемых и нереализуемых алгоритмов замещения страниц? Как можно использовать физически нереализуемые алгоритмы замещения страниц?