- •Глава I

- •06Ласти применения эвм

- •1.6,1. СуперЭвм

- •Глава 2

- •8 Разрядов

- •11110001 11111001 11110001 11110111 А число — 6.285 запишется в память в виде слова из 6 байт:

- •Глава 3

- •Глава 4

- •Лечит узап j

- •Сверхоперативная или местная память

- •4.2. Адресная, ассоциативная и стековая организации памяти

- •Буфер входа-выхода

- •Усилители считывания-записи

- •Глава 5

- •Проклей

- •Идентификатор адреса (s байт)

- •Сектор на дискете

- •Глава 6

- •Управляющий блок автомат)

- •Глава 7

- •В цпршВляющай блок у б

- •Сумматор частичных произведений Регистр множимого

- •О vМножимое перед началом Выполнения умножения

- •Слой элементов и

- •Глава 9

- •Двойное слада па адреса о 32 бит

- •Слобо по адресу z в бит

- •Заслать в стек ад РеЗ

- •Загрузить аз стана в Pa V

- •Номер регист

- •Непосредственный операнд 1а

- •15Ю кГго 51

- •Оповещающий сив нал „Состояние

- •Блок ревастрод

- •Ветвление в макропроерамме по уело дую Акк*0

- •Макрокоманды управления последовательностью выборка микрокоманд

- •Окно процедуры

- •Регистры параметров (а) Регистры глобальных переменных |

- •1 Нуль м Знак-

- •Запоминание состояния процессора (программы)

- •Общий сигнал прерывания

- •Код приоритетного запроса

- •Маска ввоОагвывода

- •Прерывающая

- •01 23*56789 Время

- •I участка I

- •Запись льта мп

- •I Прием операндов на регистры 1

- •Умножение чисел с фиксированной точкой

- •Сложонив чисел с плавающей точкой

- •Глава 10

- •Вызов команды и модификация счетчика команд

- •Процедура тандемных пересылок

- •Однобайтная

- •16 Разрядов

- •Передача д стек а восстановление содержимого регистров

- •Команды досстаяовяения из стеки содержимого регистров

- •Блок сегментных регистров

- •Первый байт команды Второй ffaSm команды (постбайт адресации)

- •Сегментные селекторы

- •Регистры задачи и регистры дескрипторнои таблицы

- •Блок управления и контроля оп

- •Справочник страниц

- •Физическая память

- •16 Мбайт

- •Расширенная память

- •1 Мбайт

- •С каналом ес эвм

- •Связь с другой эвм

- •I Манипулятор % I Графа- I I типа „Мышь” I I построитель I

- •Глава 11

- •Интерфейс основной намята

- •Общее оборудование мультиплексного канала

- •Глава 12

- •Определения четности переносод

- •Глава 13

- •Ill:Выполнснис программы а Выполнение про ерам мы в

- •Пакеты заданий и Входные наборы данных

- •Выходные очереди разных классов в зу на дисках

- •I требует ‘'ода

- •Пользователь обдумывает | ответ системе I (новый запрос)

- •Блок управления памятью

- •Схемы совпадения

- •Шифратор номера отделения

- •Входной коммутатор

- •Коммутации

- •Сегментная таблица п-й программы

- •Векторные, средства

- •К периферийным устройством

- •К периферийным устройствам

- •Глава 15

- •Устройства Ввода- вывода

- •Процессор 2

- •Процессор 3

- •8 Векторных регистров (по 6* слова в каждом)

- •Готовности операндов

- •Глава 16

- •Комплекс абонентского пункта

- •16.2.. Классификация вычислительных сетей

- •1 Элемент

- •Время распрост- ранена*

- •Задержка сета лри коммутации пакетов[

- •Абонентская система

- •Данные пользователя

- •Сеансовый

- •Транспортный

- •Сетевой

- •Интерфейс высоког о уровня

- •Аппаратура передачи данных

- •Установление связи

- •Данные пользователя 00Длина поля и слови я обслуживания

- •Идентификатор протокола

- •7» Бшдта) Данные пользователя б вызове

- •Поток бит

- •Новый пакет (кадр)

- •Станция 1 ведет передачу

- •Передатчик Коаксиальный кйбель

- •Глава 15. Принципы организации многопроцессорных и многомашинных вычислительных систем (комплексов) и суперЭвм 489

- •1S в 7 о Слада па адресу ь

Глава 10

ОРГАНИЗАЦИЯ МИКРОПРОЦЕССОРОВ И ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ

Общие сведения о микропроцессорах

Развитие интегральной технологии и схемотехники цифровых электронных схем привело к появлению интегральных микросхем с большой и сверхбольшой степенями интеграции (БИС

306

и СБИС), содержащих на одном кристалле (в одном корпусе) несколько десятков тысяч, а в последних разработках сотни тысяч элементарных транзисторов. На основе таких схем в последние годы удалось создать микропроцессоры — функционально законченные, управляемые хранимой в памяти программой (большей частью малоразрядные) устройства обработки цифровой информации, выполненные в виде одной или нескольких БИС или СБИС.

Микропроцессоры (МП) отличаются крайне малыми габаритными размерами, малой потребляемой мощностью, довольно большим быстродействием, высокой надежностью и дешевизной. Очень важной особенностью микропроцессоров является их универсальность, т. е. возможность самого разнообразного применения благодаря их программируемости на выполнение конкретных функций.

Малые габаритные размеры, универсальность, способность реализовать сложные функции обработки данных и управления служат основой для построения различных микроЭВМ, персональных компьютеров, микропроцессорных устройств и систем управления, встраиваемых в различные аппараты, машины, орудия, приборы и системы.

Микропроцессорные средства производятся в виде микропроцессорных комплектов интегральных микросхем, имеющих единое конструктивно-технологическое исполнение и предназначенных для совместного применения. Микропроцессорный комплект помимо самого микропроцессора содержит микросхемы, поддерживающие функционирование микропроцессора и расширяющие его логические возможности. *

Развитие микропроцессоров ознаменовалось соревнованием биполярной и МОП-технологий микроэлектроники.

МОП-структуры электронных схем позволяют размещать на одном кристалле большое число элементарных схем благодаря их небольшим размерам и небольшой мощности рассеяния. Однако первые МОП-микропроцессоры имели сравнительно низкое быстродействие (сложение двух слов в регистрах занимало около 20 мкс).

Биполярные БИС, например TTJl-схемы, обладали намного большим быстродействием, но значительно меньшей плотностью компонентов на кристалле. Поэтому довольно трудно было построить биполярный микропроцессор на одном кристалле.

Для преодоления ограничений, связанных со сравнительно небольшой плотностью компонентов у биполярных схем, был предложен секционный метод конструирования микропроцессоров.

По этому методу микропроцессор составляется из нескольких одинаковых 2-, 4- или 8-разрядных процессорных секций, размещенных на отдельных кристаллах и объединенных общим микропрограммным управлением. Использование секционного метода в сочетании с прогрессивной технологией маломощных TTJl-схем с диодами Шотки (ТТЛШ) позволило создать микропроцессорные комплекты серий К589, КР1802, КР1804, содержащие соответственно 2-, 4-, 8-разрядные процессорные кристаллы (секции) с быстродействием (временем цикла) 100— 150 не. В состаё этих комплексов помимо БИС процессорной секции входят пять—семь дополнительных БИС (блоки микропрограммного управления, синхронизации, связи с периферийными устройствами, прерываний). К рассматриваемому типу микропроцессорных средств относится реализованная на ЭСЛ-технологии серия быстродействующих микропроцессорных БИС К1800, содержащая 4-разрядные секции АЛУ, микропрограммного управления, синхронизатора, управления оперативной памятью.

На основе секционных микропроцессорных БИС можно строить микропроцессоры с изменяемой разрядностью слова и микропрограммным управлением. Эти микропроцессоры не имеют фиксированного набора команд, а имеют только набор микрокоманд, что позволяет (хотя это связано с определенными трудностями для широкого пользователя) реализовать микропрограммным путем оптимальный для данной задачи набор команд и отдельных процедур.

Секционные ТТЛШ и ЭСЛ-микропроцессорные серии БИС используются при построении устройств вычислительной техники и автоматики, которым предъявляются повышенные требования в отношении быстродействия.

Параллельно с этим направлением быстро совершенствовалась МОП-технология и были достигнуты крупные успехи в повышении степени интеграции и быстродействия. На этой основе по мере совершенствования МОП-технологии были созданы 8-, а затем 16-разрядные с жесткой логикой и фиксированной системой команд, а р последнее время — 32-разрядные однокристальные микропроцессоры.

В настоящее время в микропроцессорной технике основное место занимают однокристальные микропроцессоры, выполненные на различных вариантах МОП-технологии. Они служат основой современных микроЭВМ и персональных компьютеров, широко используются в различных микропроцессорных устройствах и системах автоматизации управления и обработки данных.

Организация однокристальных 8-разрядных микропроцессоров

Восьмиразрядный микропроцессор с фиксированной системой команд К580ВМ80А, в дальнейшем для краткости обозначаемый МП К580, выполнен в виде изготовленной по л-МОП-тех- нологии БИС, содержащей около 5 тыс. транзисторов на кристалле кремния размером около 30 мм2, заключенном в корпусе с 40 выводами. Работает с тактовой частотой 2 МГц (длительность такта 500 не), требует трех уровней напряжения питания: + 5, —5, +12 В. Микропроцессор К580 аналогичен МП 8080 фирмы Intel (США).

Длина машинного слова в МП К580 8, а адреса 16 разрядов. Микропроцессор может работать с оперативной и постоянной памятью, суммарная емкость которых не превышает 64 Кбайт. Ширина выборки из памяти 1 байт. Возможна адресация любого байта памяти. Скорость выполнения коротких операций (типа регистр — регистр) 500 тыс. операций/с.

Создание высокопроизводительного микропроцессора с эффективными системой команд и процедурами обмена информацией с внешним по отношению к микропроцессору оборудованием затруднялось из-за ограничений, которые вызывались коротким словом МП и малым число внешних выводов его корпуса. Последнее, в частности, обусловило узкую (малоразрядную) шину данных в МП и узкий интерфейс обмена данными с внешним оборудованием.

Для преодоления этих ограничений потребовались разработки ряда новых архитектурных решений. С частью из них читатель познакомился в гл. 9. Здесь остановимся главным образом на структурных аспектах и особенностях системы команд МП. Организация ввода-вывода в МП рассмотрена в гл. 11.

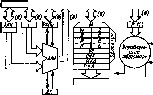

Читатель имел возможность ознакомиться с программистской моделью МП К580, приведенной в гл. 9Ь Более детальное представление об устройстве МП К580 дает его структура, приведенная на рис. 10.1.

Характерными особенностями организации МП К580 являются:

трехшинная структура с шинами данных, адреса и управления;

магистральная структура связей — наличие внутренней шины данных, которая связывает все узлы внутри МП. Ширила шины данных (8 разрядов) равна разрядности слов, с которыми Ьперирует МП;

регистровая память в виде блока программно-доступных

|

|

|

9, |

|

|

Синхрони |

с9>г |

|

! |

зация |

СИНХ ГОТ |

|

ЯППЛтт | ||

|

I |

/ ишии иость/ ожидание |

0ЖДУ |

|

|

|

ЗПДП |

|

§ |

| |

|

< § |

Управление ПДП |

ППДП |

|

|

|

ЗП |

|

| |

| |

|

1 |

ние прерыванием |

РП |

|

1 |

Управле |

ЧТ |

|

а |

ние шиной |

|

|

|

Запись |

ЗП |

|

|

|

BA

I'

* Сигналы

_1

L-

.

**/»-. ША^к^(7В)^паяний

о

Внутренняя

шина ванных (ВТ

Рис.

10.1. Структура однокристального

8-разрядного МП К580:

Узлы:

Акк

— аккумулятор; Т,

w,

г

— регистры временного хранения; РгПр

— регистр признаков; М

— мультиплексор; И/Д

— инкрементор/декрементор; РгА

—

регистр адреса; ДК

— десятичный корректор; РгК

— регистр команд; СчК

— счетчик команд; УС

—

указатель стека; БД

— буфер данных; БА

— буфер адреса; шины: ША

— шина адреса; ШД

— двунаправленная шина данных; сигналы:

ЗП

—

запись; ЧТ

— чтение; ЗП

— запрос прерывания; ЗПДП

и ППДП

— запрос и подтверждение прямого

доступа к памяти; ОЖД

— ожидание; ГОТ

— готовность; СИНХ

— синхронизация; <pi

и

<рз — тактовые сигналы; РП

— разрешение прерывания

наличие 16-разрядной шины адреса, позволяющей прямо адресовать внешнюю память емкостью 64 Кбайт;

разнообразие применяемых методов адресации — прямая, регистровая прямая, регистровая косвенная (в том числе подразумеваемая), непосредственная, индексная, стековая,— в совокупности позволяющих при коротком 8-разрядном слове реализовывать достаточно гибкую систему команд, использующую три формата команд: 1, 2, 3 байта;

наличие эффективных средств работы с подпрограммами и быстродействующей системой прерывания, использующих стековую память («перевернутый стек»), специальные команды вызова подпрограмм и возврата (в том числе условного) из подпрограмм и процедуры перехода к прерывающим и возврата к прерванным программам;

реализация двухбайтных (тандемных) передач и некоторых^ других двухбайтных операций, с тем чтобы при 8-разрядных шине данных, общих регистрах и ширине выборки из ОП упростить процедуры обработки 16-разрядных слов и работу с 16-разрядными адресами и тремя форматами команд. Последнее достигается тем, что первый байт команды, содержащий указание об ее формате, загружается всегда в регистр команды, а второй и третий, если они имеются,— в определенные регистры.

Помимо упоминавшихся шин данных и адреса имеется шина управления, содержащая линии, предназначенные для передачи управляющих сигналов, признаков состояния процессора и периферийного оборудования. Шина содержит следующие линии: синхронизирующих сигналов для сопровождения информации при передачах ее в обоих направлениях по мультиплексируемой шине данных;

сигналов, информирующих МП о состоянии (готовности) периферийных устройств;

сигналов запроса прерывания от периферийных устройств -и разрешения прерывания и др.

Блок регистров содержит программно-доступные (с регистровой прямой или подразумеваемой адресацией) регистры: 8-разрядные аккумулятор А, общие регистры В, С, D, £, 16-раз- рядные счетчик команд СчК> указатель стека УС, парный регистр косвенного адреса Н — L, а также 8-разрядный регистр признаков, отдельные разряды (флажки) которого, принимая значение 1, указывают: СУ — перенос, Р и М — соответственно знак + и — результата, АС—вспомогательный перенос, Z — нулевой результат. Кроме того, имеется регистр адреса РгА. Регистры используются для хранения операндов, промежуточных результатов и адресов.

Непосредственно в МП из оборудования стековой памяти содержатся только указатель стека и соответствующие цепи управления. Сам стек реализуется в виде зоны ячеек в общей ОП. Хотя такая организация стека по сравнению с внутренним (встроенным в кристалл МП) стеком связана с некоторым замедлением стековых процедур, однако операции со стеком выполняются намного* реже, чем с другими регистрами. При таком выполнении стека его емкость практически неограниченна, оказывается возможным большее число вложелий при работе с подпрограммами и прерываниями, что в общем обеспечивает высокую производительность МП.

Блок регистров содержит специальную схему «инкремен- тор»/«Декрементор» И/Д, позволяющую без привлечения АЛУ в процессе межрегистровых передач выполнять модификацию текущего адреса добавлением (вычитанием) 1.

Арифметическо-логическое устройство, выполненное в виде комбинационной схемы с собственным регистром временного хранения, производит арифметические и логические операции над 8-разрядными операндами. Один вход АЛУ связан с аккумулятором, а другой может быть соединен с любым общим регистром. ИмеетЬя включаемый специальной командой десятичный корректор, превращающий результат непосредственно предшествующей операции двоичного сложения (вычитания) над двоично-десятичными операндами в результате соответствующей операции десятичной арифметики (см. гл. 7).