- •Глава I

- •06Ласти применения эвм

- •1.6,1. СуперЭвм

- •Глава 2

- •8 Разрядов

- •11110001 11111001 11110001 11110111 А число — 6.285 запишется в память в виде слова из 6 байт:

- •Глава 3

- •Глава 4

- •Лечит узап j

- •Сверхоперативная или местная память

- •4.2. Адресная, ассоциативная и стековая организации памяти

- •Буфер входа-выхода

- •Усилители считывания-записи

- •Глава 5

- •Проклей

- •Идентификатор адреса (s байт)

- •Сектор на дискете

- •Глава 6

- •Управляющий блок автомат)

- •Глава 7

- •В цпршВляющай блок у б

- •Сумматор частичных произведений Регистр множимого

- •О vМножимое перед началом Выполнения умножения

- •Слой элементов и

- •Глава 9

- •Двойное слада па адреса о 32 бит

- •Слобо по адресу z в бит

- •Заслать в стек ад РеЗ

- •Загрузить аз стана в Pa V

- •Номер регист

- •Непосредственный операнд 1а

- •15Ю кГго 51

- •Оповещающий сив нал „Состояние

- •Блок ревастрод

- •Ветвление в макропроерамме по уело дую Акк*0

- •Макрокоманды управления последовательностью выборка микрокоманд

- •Окно процедуры

- •Регистры параметров (а) Регистры глобальных переменных |

- •1 Нуль м Знак-

- •Запоминание состояния процессора (программы)

- •Общий сигнал прерывания

- •Код приоритетного запроса

- •Маска ввоОагвывода

- •Прерывающая

- •01 23*56789 Время

- •I участка I

- •Запись льта мп

- •I Прием операндов на регистры 1

- •Умножение чисел с фиксированной точкой

- •Сложонив чисел с плавающей точкой

- •Глава 10

- •Вызов команды и модификация счетчика команд

- •Процедура тандемных пересылок

- •Однобайтная

- •16 Разрядов

- •Передача д стек а восстановление содержимого регистров

- •Команды досстаяовяения из стеки содержимого регистров

- •Блок сегментных регистров

- •Первый байт команды Второй ffaSm команды (постбайт адресации)

- •Сегментные селекторы

- •Регистры задачи и регистры дескрипторнои таблицы

- •Блок управления и контроля оп

- •Справочник страниц

- •Физическая память

- •16 Мбайт

- •Расширенная память

- •1 Мбайт

- •С каналом ес эвм

- •Связь с другой эвм

- •I Манипулятор % I Графа- I I типа „Мышь” I I построитель I

- •Глава 11

- •Интерфейс основной намята

- •Общее оборудование мультиплексного канала

- •Глава 12

- •Определения четности переносод

- •Глава 13

- •Ill:Выполнснис программы а Выполнение про ерам мы в

- •Пакеты заданий и Входные наборы данных

- •Выходные очереди разных классов в зу на дисках

- •I требует ‘'ода

- •Пользователь обдумывает | ответ системе I (новый запрос)

- •Блок управления памятью

- •Схемы совпадения

- •Шифратор номера отделения

- •Входной коммутатор

- •Коммутации

- •Сегментная таблица п-й программы

- •Векторные, средства

- •К периферийным устройством

- •К периферийным устройствам

- •Глава 15

- •Устройства Ввода- вывода

- •Процессор 2

- •Процессор 3

- •8 Векторных регистров (по 6* слова в каждом)

- •Готовности операндов

- •Глава 16

- •Комплекс абонентского пункта

- •16.2.. Классификация вычислительных сетей

- •1 Элемент

- •Время распрост- ранена*

- •Задержка сета лри коммутации пакетов[

- •Абонентская система

- •Данные пользователя

- •Сеансовый

- •Транспортный

- •Сетевой

- •Интерфейс высоког о уровня

- •Аппаратура передачи данных

- •Установление связи

- •Данные пользователя 00Длина поля и слови я обслуживания

- •Идентификатор протокола

- •7» Бшдта) Данные пользователя б вызове

- •Поток бит

- •Новый пакет (кадр)

- •Станция 1 ведет передачу

- •Передатчик Коаксиальный кйбель

- •Глава 15. Принципы организации многопроцессорных и многомашинных вычислительных систем (комплексов) и суперЭвм 489

- •1S в 7 о Слада па адресу ь

16 Разрядов

по которому произойдет передача управления.

Код N=AqAiA2 определяет адрес вектора прерывания соответствующей прерывающей программы, а точнее, начальный адрес группы ячеек ОП, хранящей информацию о начальном адресе прерывающей программы. В рассматриваемом МП сохранение в памяти вектора состояния прерываемой программы и замена его в регистрах вектором прерывания прерывающей программы выполняются в основном не аппаратурными, а программными средствами. Поэтому в данном случае элементы вектора прерывания хранятся в ОП в виде операндов фрагмента

Передача д стек а восстановление содержимого регистров

|

В*И+1

Адрес

ПрП

п

Область

стека

I

(яс)-в

(яс)-б

(1ГС)-+

(яс)-г

(ус)

»АПрП

АПрП+1

лпрп+г

fl

{

СчКм

СчК,

ст |

F |

|

В |

С |

|

Л |

Е |

|

И |

1 |

|

УС | |

|

СчК | |

|

15 |

0 |

Аккуму-

Регистр

лятар признаков

8**

Регистры

МП

Передачи

^ В стек и Восстановление содержимого

СчК

Пр

еры дающая ограмма ПрП)

Содственяо

программа

одрадотки

прерывания

Область

докторов

прерывания

PUSH

PSW

АЛрПет

PUSH

И

PUSH

и

El

PUSH

в

JMPJflАПрПщл

UI

POP

В

POPS

POP

Н

POP

PSWКоманды досстаяовяения из стеки содержимого регистров

El

RETВозврат

к прерванной программе

Рис. 10.5. Процедура прерывания программ в МП К580:

IMP — передача управления;DI иEI —запрещение и разрешение прерывания;PUSH иPOP —запись в стек и считывание из стека;RET —загрузка из стека счетчика командСчК(возврат к прерванной программе)

программы, выполняющей указанные процедуры (рис. 10.5). Код N может не только формироваться аппаратурой, как это было описано выше, но и передаваться источником прерывания, например периферийным устройством, по шине данных интерфейса вместе с запросом прерывания (см. гл. 11).

Управление переходит к команде, загружающей в СчК адрес

начала прерывающей программы. Начальная часть этой программы помещает в стек содержимое регистра-аккумулятора А и регистра признаков F (команда PUSH PSW), а также и других программно-доступных регистров МП, если прерывающая программа будет их использовать, при этом каждой командой передачи в стек передается содержимое соответствующей пары регистров. Далее выполняется собственно программа обработки прерывания.

Перед выходом из прерывающей программы последняя восстанавливает из стека состояния регистров, в том числе аккумулятора и регистра признаков, которые они имели перед прерыванием, и управление переходит к прерванной программе (команда RET). Перед выполнением процедуры запоминания и восстановления содержимого регистров прерывание запрещается (команда D/), а по их завершении разрешается (команда EL).

Организация однокристальных 16-разрядных микропроцессоров

На основе л-МОП-технологии с кремниевыми затворами удалось реализовать принцип пропорционального уменьшения размеров МОП-схем, достигнуть большей степени интеграции (около 30 тыс. транзисторов на кристалле размером 5,5 X Х5,5мм) невысокого быстродействия. Задержка на элемент уменьшилась, она имеет тот же порядок, что и в ТТЛ-схемах с диодами Шотки, имеющими значительно большие размеры и потребляемую мощность.

На МОП БИС указанного типа фирмой Intel (США) был создан однокристальный 16-разрядный МП 8086 (прототип отечественного МП КМ1810ВМ86, в дальнейшем для сокращения именуемого К1810), который по уровню производительности и логической организации не уступает средним моделям малых ЭВМ. Приборы выпускаются в 40-контактном корпусе.

'Производительность МП К1810 составляет при 'тактовой частоте 5 МГц 2,5 млн. операций типа регистр-регистр. Это достигнуто благодаря повышению быстродействия схем и архитектурным усовершенствованиям. Архитектура МП К1810 имеет следующие особенности:

выполнение аппаратурными средствами арифметических операций над 8- и 16-разрядными двоичными числами со знаком и без знака, десятичными двоично-кодированными числами, логических операций под цепочками данных, расширенные возможности работы с отдельными разрядами слов;

наличие 16-разрядного АЛУ с аппаратурной реализацией умножения и деления;

|

/

Сумматор

ж

АЛгб/$з

^ Старшие

ABn/Sц.

I биты

-*»AJ)J8fSs

\

адреса и -+AB„/Se)

С Ч

Б. М. Каган

15

состояния

Зкстракодовый

сегмент ES

Чтение

Запись

РРА

Разреш. регистр адреса ПБ Передача

байта П/ВВ Память/ВВ ОД Строб данных

ПЕР/ПР Обмен данными

Сегмент

стека

Блок

регистров переад- ресации

SS

§

6-*-ЗАП

Сегмент

данных

Сегмент

кода

CS

устройство

СС

Синхросигнал СБР Сброс ПРО Проверка

ГТ

Готов

МИН/МАКС

.

ЗПР

Запрос прерывания

НМТ

Немаскируемое прерывание ППР

Подтверждение прерывания

ЗПДП

Запрос ПДП

ППДП

подтверждение ПДП

Внутренняя

шина ван-

"

О

ных (16)

Аккумулятор

\_7S_7

Регистр

признаков (флажков)

| |

AL | |

|

ВН |

BL | |

|

СИ |

CL | |

|

ВН |

JJL | |

|

Указатель стека |

$Р | |

|

Указатель базы |

ВР | |

|

Индекс-регистр операнда SI | ||

|

Индекс-регистр результата UI | ||

|

15

Блок

общих

регист

ров Ж

База

Счетчик

Данные

15

Устройства

] * сопряжения

с шиной

И

Я |

Б |

|

|

5 |

|

/ |

* |

|

|

3 |

|

|

1 |

|

|

1 |

шина

(16)

Очередь

команд

Сигналы

« у

правде-

< ния

МП у

Указателе

(счетчик) команд IP

А-шина

Г

Рис.

10.6. Структурная схема 16-разрядного МП

К1810

регистровая структура с удвоенным по сравнению с К580 числом общих регистров, практически неограниченное число уровней векторного прерывания;

полная совместимость по системе команд с МП К580 (в том числе работа с 8-разрядными командами последнего) и одновременно наличие новых, эффективных 16-разрядных команд;

сегментная адресация, позволяющая прямо адресовать одномегабайтную память (оперативную, дисковую и т.п.), производить динамическое перемещение программ;

использование одного уровня напряжения питания 5 В. Связь между МП, ОП и периферийными устройствами осуществляется с помощью интерфейса И41 (мультишина)' (см. гл. 11).

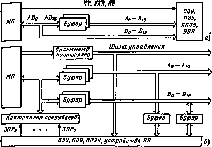

На рис. 10.6 представлена структурная схема МП К1810, в которой имеются относительно автономные устройства: а) устройство сопряжения с шиной (УСШ), обеспечивающее опережающую выборку команд и формирование очереди выбранных байт последовательности команд в специальной регистровой памяти (емкость 6 байт), а также формирование физического адреса памяти, чтение операндов из памяти или регистров ввода-вывода и запись результата операции в память или регистры ввода-вывода; б) операционное устройство (ОУ), извлекающее команды из очереди и реализующее предписанные командами операции в 16-разрядном АЛУ.

Устройство сопряжения с шиной помимо регистров очереди команд имеет блок 16-разрядных регистров переадресации, 16-разрядный сумматор адреса. Сюда же можно отнести указатель (счетчик) команд.

Такая структура при определенном соотношении тактовой частоты МП и длительности цикла памяти позволяет получить эффективное совмещение процессов выборки и исполнения команд. Одному циклу основной памяти (800 не) соответствуют четыре такта работы МП К1810. При совмещении за время одного цикла основной памяти выполняются две однобайтные команды.

Операционное устройство включает в себя блок 16-разрядных общих регистров, содержащий четыре регистра данных: аккумулятор АХ, базовый регистр ВХ, «счетчик» СХ и «данные» DX, регистры — указатели стека SP и базы ВР и индексные регистры операнда SI и результата D/, а также АЛУ и 16-разрядный регистр признаков (флажков) F.

Устройство управления и синхронизации управляет УСШ и ОУ, а также обменом данными с периферийными устройствами, включая обработку запросов прерывания и реализацию прямого доступа к памяти.

Рис.

10.7. Конфигурации МП-систем: а

— минимальная; б — максимальная

Микропроцессор К1810 имеет специальные аппаратурные средства (сегментная адресация и др.), поддерживающие мультипрограммный режим работы и облегчающие создание на основе этого МП многопроцессорных систем, в том числе содержащих арифметические сопроцессоры, позволяющие в несколько раз увеличить скорость выполнения арифметических операций с плавающей точкой и вычисление некоторых, функций.

Микропроцессор может работать в минимальной или максимальной конфигурации (рис. 10.7). Соответствующий режим работы устанавливается управляющим сигналом МИН/МАКС. При этом в максимальной конфигурации используется дополнительная микросхема — системный контроллер, вырабатывающий сигналы, управляющие записью и считыванием информации в памяти и в периферийных устройствах, и сигналы, подтверждающие прерывание. В минимальной конфигурации управляющие сигналы для памяти и устройств ввода-вывода вырабатывает сам МП К1810.

На рис. 10.8 представлена программистская модель МП К1810, содержащая его программно-доступные регистры [25, 35].

Регистры данных АХ, ВХУ СХ, DX служат для хранения операндов и результатов операций. Возможна адресация как Целых регистров, так и их младшей L и старшей Н частей. Не-

Регистры

. данных

s

Регистры

общего

назначения

Регистры

индексные и указатели

Сегментные

регистры

АХ

АН

т 1 'таГ~

ВХ

ВН

Т 1 ~BL

СХ

СИ

пг 1 ~L

их

ЛН

т 1 1>L

SP

BP

SI

UI

CS

US

SS

ES

Аккумулятор

База

Счетчик

Данные

\

Указатель

стека Указатель базы данных Индекс

источника Индекс приемника

Сегмент

кода

Сегмент

данных

Сегмент

стека

Сегмент

дополнитель ный

| IP ^Указатель (счетчик) команд

75

14 73 11 11 10 9 0 7 5 5 *32 1 О

Г?! 11111 о Мо М i щРееистРзнаков

ПереносЧетность

Вспомогательный,

перенос

Нуль

Знак

Пошаговый,

режим Разрешение прерывания Направление

сканирования Переполнение

Рис.

10.8. Программистская модель МП К1810

которым регистрам наряду с общим придается и специальное назначение. В последнем случае возможно в соответствующих командах адресовать эти регистры неявно самим кодом операции (подразумеваемая адресация). Так, регистр АХ используется в качестве аккумулятора, регистр ВХ — как базовый регистр, СХ — как счетчик в командах сдвигов, управления вычислительными циклами и в операциях с цепочками байт, а регистр DX не-

' явно адресуется в командах умножения и деления, а в некоторых операциях ввода-вывода хранит адрес порта ввода-вывода.

В МП К1810 используется сегментация памяти, организуемая с помощью сегментных регистров: кода CS, данных DS, стека S5 и экстракода (дополнительного сегмента) £S, хранящих базовые адреса сегментов текущей программы. Эти базовые адреса должны быть кратны 16. Размер сегментов 64 Кбайт. Допускается перекрытие сегментов.

Группу указательных и индексных регистров, задающих внутрисегментные смещения, образуют регистры указателя стека SPt указателя базы стека (данных) ВР, индекса операнда (источника) SI и индекса результата (приемника) DI. К.этой группе можно отнести и регистр указателя (счетчика) команд IP.

' Регистр признаков (флажков) F, который правильнее называть регистром состояния микропроцессора, имеет 16 разрядов, причем младшие 8 разрядов соответствуют регистру признаков (флажков) МП К580. В регистре признаков формируются: а) признаки результата: переполнения OF (при операциях с целыми числами); знака результата SF\ нуля ZF\ вспомогательного переноса AF (перенос из третьего или заем в третий разряд); четности PF (четное число единиц в младшем байте результата); переноса CF (перенос из старшего или заем в старший разряд результата); б) признаки управления: пошагового режима TF (управляет пошаговыми прерываниями); разрешения прерывания IF (разрешает или запрещает маскируемые прерывания); направления DF (указывает направления обработки цепочки данных, начиная с элемента с наименьшим адресом при DF=0 или с наибольшим адресом при DF= 1).

Четыре 16-разрядных указательных и индексных регистров (SPt BP, S/, DI) могут участвовать в выполнении арифметических и логических операций над двухбайтными словами.

Память имеет байтовую организацию — двухбайтовое слово размещается в смежных ячейках, причем старший байт занимает ячейку с большим номером. Адресом слова служит адрес младшего байта. Рекомендуется слова размещать по четным адресам.

Хотя все регистры данных, указателей и сегментов 16-раз- рядные, на шину адреса выдаются и используются при обращениях к ОП 20-разрядные исполнительные (физические) адреса, позволяющие обращаться к ОП емкостью 1 Мбайт. Это становится возможным благодаря механизму сегментации памяти. В адресуемом пространстве выделяются сегменты, содержащие

Кбайт. Допускается перекрытие сегментов. Базовые (начальные) 16-разрядные адреса сегментов, хранящиеся в соответству- Юц*их сегментных регистрах, трактуются как 20-разрядные с ну-

ПамятьРис.

10.9. Сегментация адресного пространства

памяти

I

$