637_Nosov_V.I._Seti_radiodostupa_CH.2_

.pdf

увеличивается выигрыш от использования избыточного кодирования. Избыточное кодирование сверточным кодом со скоростью Rc 3 4, позволяет

4, позволяет

на приемной стороне обнаруживать и исправлять ошибки в трехбитовых информационных блоках.

Второй цифровой поток поступает на дифференциальный кодер (кодер относительности), с помощью которого на приемной стороне устраняется неоднозначность фазы опорного напряжения в фазовом детекторе. После дифференциального кодирования сигнал поступает на кодер 2, в котором входной цифровой поток разбивается на одиннадцать параллельных потоков. Информационные биты этих одиннадцати потоков суммируются по модулю два и результат суммирования помещается в избыточный двенадцатый бит. Таким образом, в этом кодере осуществляется проверка блока из одиннадцати информационных бит на четность, что позволяет на приемном конце обнаружить наличие ошибки в этом блоке.

С выходов кодеров 1 и 2 сигналы поступают на преобразователи параллельного кода в последовательный код (p/s – parallel / serial). Поскольку цифровые потоки с третьего по шестой не содержат избыточных бит и не обрабатываются в кодерах, для сохранения синхронности всех шести потоков на входе схемы размещения, они проходят через линию задержки.

В устройстве размещения шесть входных потоков, которые имеют 64 различных состояния, размещаются на фазово-амплитудной плоскости модулятора, т.е. на синфазной I и квадратурной Q осях. При этом на выходе устройства размещения, при использовании процедуры прореживания сигнальных точек созвездия, будут три цифровых потока символов для синфазного канала I1, I2 , I3 и три потока для квадратурного канала – Q1,Q2 ,Q3

(смотри раздел 4).

Цифровые потоки символов в многоуровневом кодере для 64 КАМ таблица 6.2 имеют различное количество избыточных бит. В первом потоке избыточное кодирование со скоростью Rd1 3 4 обеспечивает на приемной

4 обеспечивает на приемной

стороне обнаружение и исправление ошибок.

Во втором потоке избыточное кодирование со скоростью Rd 2 11 12

обеспечивает на приемной стороне обнаружение ошибки в блоке из одиннадцати информационных бит. Остальные четыре из шести цифровых потоков символов не имеют избыточных бит, т.е. ошибки в них даже не контролируются. Таким образом, обеспечивается минимальная избыточность при кодировании цифровых сигналов.

Теперь стоит задача так разместить эти шесть цифровых потоков символов, чтобы с наибольшей вероятностью исправлять ошибки символов в этих потоках на приемной стороне, т.е. в данном случае в аппаратуре используется принцип кодирования с учетом структуры модулированного сигнала, т.е. реализуется «кодем» (кодер совместно с модулятором).

Необходимо так разместить первый цифровой поток символов, чтобы он определял при модуляции соседние точки на созвездии сигнальных точек. Объясняется это тем, что при прохождении через радиотракт из-за действия

201

Рассмотрим, как на приемной стороне исправляются ошибки в шести цифровых потоках символов, при условии, что избыточные биты были введены только в первый и второй цифровые потоки.

На выходе демодулятора 64-КАМ после принятия решения о текущем принятом уровне сигнала рисунки 6.12 и 6.13 , соответствующий уровень поступает на АЦП, в котором в соответствии с таблицей 6.3 преобразуется в одно из восьми состояний трех цифровых потоков по синфазному I1I2 I3 и

квадратурному Q1Q2Q3 каналам.

Таблица 6.3 Преобразование восьмиуровневого сигнала в АЦП

№ |

Входной |

Выходные сигналы в каналах P(Q) |

||

|

сигнал АЦП |

I1(Q1) |

I2 (Q2) |

I3 (Q3) |

1 |

7L |

0 |

0 |

0 |

2 |

5L |

0 |

0 |

1 |

3 |

3L |

0 |

1 |

0 |

4 |

1L |

0 |

1 |

1 |

5 |

-1L |

1 |

0 |

0 |

6 |

-3L |

1 |

0 |

1 |

7 |

-5L |

1 |

1 |

0 |

8 |

-7L |

1 |

1 |

1 |

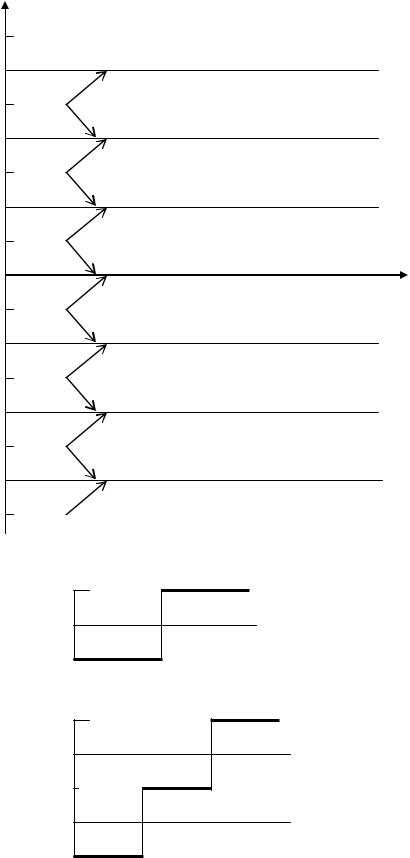

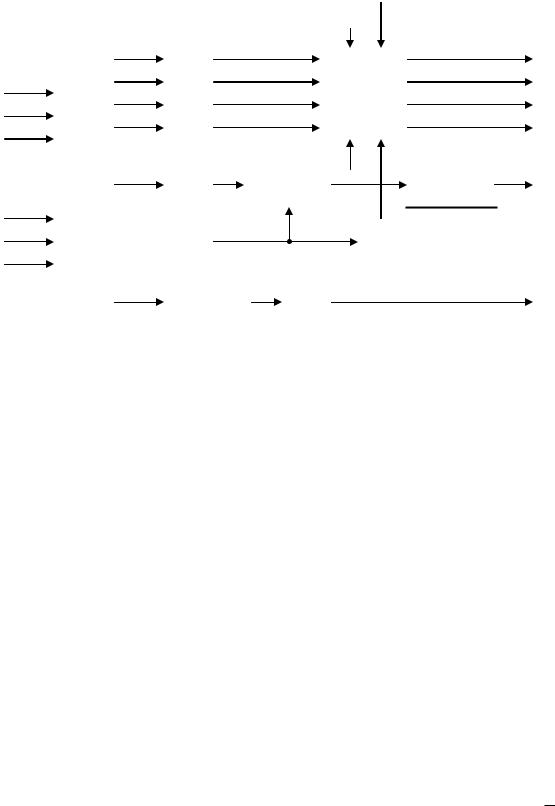

На выходе демодулятора в управляющей логике на основе раздельного анализа «глазковых» диаграмм в синфазном и квадратурном каналах фиксируется знак отклонения принятого уровня от номинального значения в момент принятия решения. Поскольку при 64 КАМ анализируется восьмиуровневый сигнал, то при фиксации положительного и отрицательного отклонения принятого сигнала, получается шестнадцать различных состояний рисунок 6.14. Такое количество состояний можно закодировать четырехразрядным двоичным кодом и передать с помощью четырех двоичных цифровых потоков. Такие четыре дополнительных цифровых потока передаются в устройство декодирования вместе с тремя информационными цифровыми потоками, как по синфазному каналу, так и по квадратурному каналу рисунок 6.12.

На вход декодера с выхода демодулятора 64-КАМ поступают по три информационных двоичных цифровых потока по синфазному I1I2 I3 и

квадратурному Q1Q2Q3 каналам и по четыре вспомогательных (служебных) цифровых потока I4I5I6I7 по синфазному каналу и Q4Q5Q6Q7 по квадратурному

каналу.

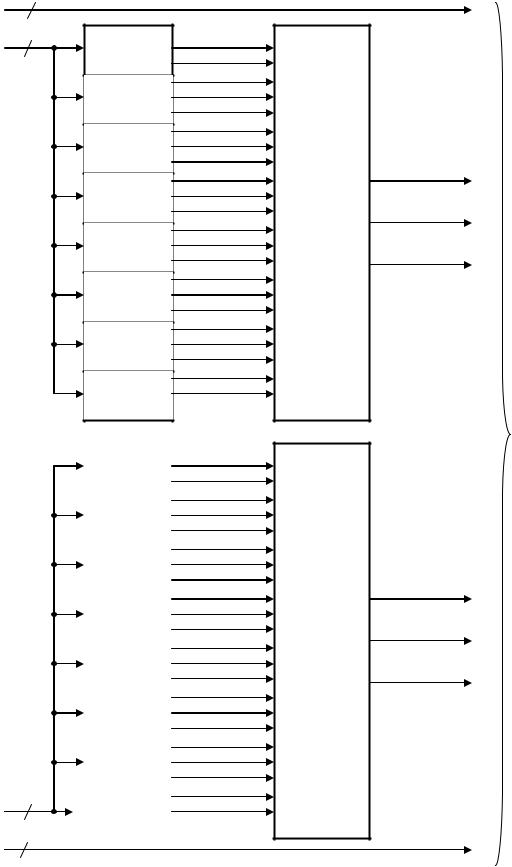

Структурная схема устройства обнаружения и исправления ошибок приведена на рисунке 6.15.

На входах устройства обнаружения и исправления ошибок приходят по семь цифровых потоков I1I2 I3I4 I5I6 I7 по синфазному каналу и Q1Q2Q3Q4Q5Q6Q7

по квадратурному каналу.

203

Операция обратная размещению (mapping), проведенному в модуляторе 64-КАМ (смотри раздел 4), деразмещение (demapping) осуществляется на входе декодера рисунок 6.15. В устройстве деразмещения шесть входных информационных потоков I1I2I3Q1Q2Q3 преобразуются в шесть потоков

d6d5d4d3d2d1 согласно кодовой таблице для 64-КАМ (смотри раздел 4). В полученных шести потоках d6d5d4d3d2d1 избыточные биты есть в

первом d1 цифровом потоке со скоростью Rc = 3/4 и во втором d2 цифровом потоке со скоростью Rc = 11/12, таблица 6.2.

7L |

+ |

000 |

||||

|

|

|

|

|

||

- |

000 |

|||||

|

||||||

5L |

+ |

001 |

||||

|

|

|

|

001 |

||

- |

||||||

|

||||||

3L |

+ |

010 |

||||

|

|

|

|

|

010 |

|

|

- |

|||||

1L |

|

+ |

011 |

|||

|

|

|

|

011 |

||

|

|

- |

||||

-1L |

|

+ |

100 |

|||

|

|

|

|

|

||

|

|

- |

100 |

|||

-3L |

+ |

101 |

||||

|

|

|

|

101 |

||

- |

||||||

|

||||||

-5L |

|

+ |

110 |

|||

|

|

|

|

|

||

|

- |

110 |

||||

|

||||||

-7L |

|

+ |

111 |

|||

|

|

|

|

|

||

|

|

- |

111 |

|||

Рисунок 6.14 Формирование четырех дополнительных цифровых потоков.

Эти избыточные биты были заполнены символами «0» или «1» в сверточном кодере для потока d1 и в кодере проверки на четность для потока d2 в кодере на передающей стороне рисунок 6.10.

Поток d1 с выхода устройства деразмещения поступает на декодер Витерби, который позволяет обнаружить и исправить одиночные ошибки в информационных символах закодированных сверточным кодом [23].

Цифровой поток d2 рисунок 6.15 с выхода устройства деразмещения через устройство задержки на время обработки сигнала в декодере Витерби потока d1 поступает на декодер проверки на четность. В этом декодере последовательный блок из двенадцати символов преобразуется в параллельный и все 12 символов подаются на сумматор по модулю два. Если на выходе сумматора получится

206

ноль, то количество единиц в блоке четное и ошибки в тракте передачи в этом блоке не произошло.

|

P4 – P7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q4 – Q7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1 |

|

d5 |

|

2 |

|

|

|

|

|

Решающее |

|

|

D5 |

||||||||

|

d4 |

|

|

|

|

|

|

|

D4 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

устройство |

|

|

||||||||

P2 |

|

d3 |

|

|

|

|

|

|

|

|

|

|

D3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

P3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Деразме |

d2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

щение |

|

1 |

|

|

Декодер |

|

|

|

|

|

|

|

Диф. |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

четности |

|

|

|

|

|

|

|

Декодер |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|||

Q3 |

|

d1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Декодер |

|

|

3 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

Витерби |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 6.15 Устройство деразмещения входных сигналов и исправление ошибок

Если же на выходе сумматора получится единица, т.е. число единиц в блоке нечетное, то фиксируется наличие ошибки символа в одном из двенадцати символов.

Из рисунка 6.15 следует, что результат декодирования потока d1 в декодере Витерби используется в декодере четности потока d2 и при принятии решения по потокам d3 – d6. Результат декодирования потока d2 в декодере четности так же используется при принятии решения по потокам d3 – d6. Кроме того, при принятии решения в потоках d3 – d6 используются четыре дополнительных потока I4I5I6I7 по синфазному и Q4Q5Q6Q7 по квадратурному

каналам. Эти потоки несут информацию о знаке отклонения принимаемого уровня от номинального значения перед принятием решения о текущем принятом уровне на выходе демодулятора 64-КАМ.

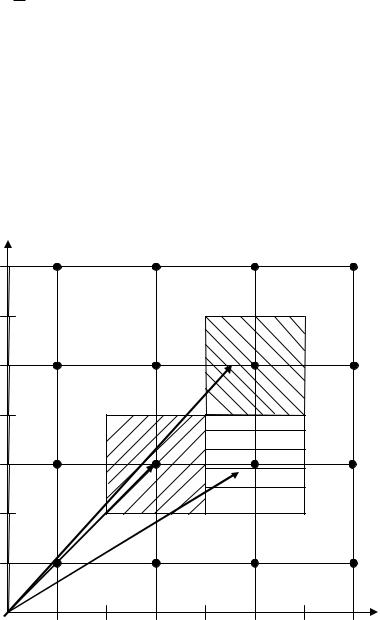

Рассмотрим процедуру исправления ошибок в потоках d2d3d4d5d6 . Из

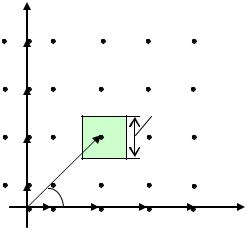

рисунка 6.16 следует, что ошибка при приеме сигнальной точки под номером 19 произойдет, если под воздействием шумов, помех и искажений она переместится за пределы квадрата со стороной d, построенного вокруг этой точки.

Если эта сигнальная точка будет смещена на расстояние меньшее

2d , то будет зафиксирована одна из соседних сигнальных точек под номерами 11,18,20 или 27. Если же эта сигнальная точка будет смещена на расстояние

2d , то будет зафиксирована одна из соседних сигнальных точек под номерами 11,18,20 или 27. Если же эта сигнальная точка будет смещена на расстояние

207

больше, чем

2d по одной из диагоналей, то будет зафиксирована одна из сигнальных точек, расположенных по диагонали от рассматриваемой сигнальной точки 19 – точки 10,12, 26 или 28.

2d по одной из диагоналей, то будет зафиксирована одна из сигнальных точек, расположенных по диагонали от рассматриваемой сигнальной точки 19 – точки 10,12, 26 или 28.

Входные цифровые информационные потоки многоуровневого кодера I1I2 I3 и Q1Q2Q3 по синфазному и квадратурному каналам, соответственно, и

выходные потоки d1d2d3d4d5d6 устройства деразмещения, соответствующие

рассматриваемым сигнальным точкам на фазово-амплитудной плоскости рисунок 6.16, приведены в таблице 6.4.

Q |

|

|

|

|

7L |

25 |

17 |

9 |

1 |

|

|

|

|

5L |

26 |

18 |

б |

10 |

2 |

|

3L |

27 |

19 |

а |

11 |

3 |

|

|||||

|

|

|

|

|

|

1L |

28 |

20 |

|

12 |

4 |

|

|

|

|

|

P

1L |

3L |

5L |

7L |

Рисунок 6.16 Возникновение ошибки в потоке d1 а и в потоке d2 б при приеме сигнальной точки 19

Как следует из таблицы 6.4 принятое в данной радиорелейной системе избыточное кодирование позволяет исправлять только наиболее вероятные ошибки, соответствующие приему вместо переданной сигнальной точки, в данном примере под номером 19, одной из соседних точек под номерами 11,18, 20 и 27.

Это связано с тем, что при приеме этих сигнальных точек происходит ошибка в первом потоке d1, которая благодаря наличию в нем избыточного кодирования со скоростью Rb = 3/4, может быть обнаружена и исправлена.

Известно, что исправление ошибки производится инвертированием информационного бита, в котором произошла ошибка. Следовательно, для

208

того, чтобы исправить ошибку необходимо определить ее местоположение в цифровом потоке.

Таблица 6.4 Цифровые потоки для сигнальных точек

|

I1 |

I2 |

I3 |

Q1 |

Q2 |

Q3 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

19 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

11 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

27 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

18 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

20 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

10 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

12 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

26 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

28 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

Из таблицы 6.4 следует также, что при принятом способе избыточного кодирования ошибки, соответствующие приему вместо переданной сигнальной точки, в данном примере под номером 19, одной из ближайших точек по диагонали под номерами 10,12,26 или 28, не могут быть исправлены. Так как в этих случаях нет ошибки в первом цифровом потоке d1 и местоположение ошибки не может быть обнаружено.

Итак, рассмотрим последовательность исправления ошибок в потоках d2d3d4d5d6 при приеме вместо переданной сигнальной точки 19 одной из

соседних точек 11,18,20 или 27. Предположим, что вместо 19 сигнальной точки принята сигнальная точка под номером 18. Эта точка соответствует уровням +5L по синфазному и +3L по квадратурному каналам. Перед принятием решения по принятому уровню на выходе демодулятора 64-КАМ с большой вероятностью по синфазному каналу было занижение уровня +5L. Эта информация передается в многоуровневый декодер в потоках I4I5I6I7 .

Декодер Витерби в потоке d1 определяет ошибку и ее местоположение и исправляет ее. В декодере четности также обнаруживается ошибка в блоке из одиннадцати информационных символов в потоке d2, но не определяется ее местоположение. Согласно таблице 6.2 ошибочным символом в потоке d2 с большой вероятностью будет символ, расположенный над ошибочным символом в потоке d1, так как блок из шести символов расположенных в столбце таблицы соответствует одной сигнальной точке.

В соответствии с рисунком 6.15 происходит исправление ошибочного символа в потоке d2. Если декодер Витерби в потоке d1 и декодер четности в потоке d2 обнаруживают ошибки, то с большой вероятностью можно утверждать, что произошла ошибка при приеме сигнальной точки. В решающем устройстве для потоков d3d4d5d6 с помощью потоков I4I5I6I7 в

данной ситуации принимается решение, что вместо сигнальной точки под номером 18 нужно зафиксировать сигнальную точку под номером 19. В результате такого решения в потоках d6d5d4d3 кодовая комбинация 0001,

209

соответствующая сигнальной точке 18, заменяется на кодовую комбинацию 0011, соответствующую точке 19.

Аналогичные действия производятся при приеме сигнальной точки под номером 20 и в результате решения в потоках d6d5d4d3 кодовая комбинация

1111, соответствующая сигнальной точке 20, заменяется на кодовую комбинацию 0011, соответствующую сигнальной точке 19.

Теперь предположим, что вместо 19 сигнальной точки принята сигнальная точка под номером 11. Эта точка соответствует уровням +3L по синфазному и +5L по квадратурному каналам. Перед принятием решения по принятому уровню на выходе демодулятора 64-КАМ с большой вероятностью по квадратурному каналу было занижение уровня +5L. Эта информация передается в многоуровневый декодер в потоках Q4Q5Q6Q7 .

Декодер Витерби в потоке d1 определяет ошибку, ее местоположение и исправляет ее. При этом в декодере четности не обнаруживается ошибка в блоке из одиннадцати информационных символов в потоке d2. Этот факт указывает на то, что смещение принимаемой сигнальной точки произошло в одну из соседних точек по квадратурной оси.

В этом случае в потоке d2 не осуществляется исправление символа, и информация об этом передается в решающее устройство для потоков d6d5d4d3 .

В этом решающем устройстве с помощью потоков Q4Q5Q6Q7 в данной

ситуации принимается решение, что вместо сигнальной точки под номером 11 нужно зафиксировать сигнальную точку под номером 19. В результате такого решения в потоках d6d5d4d3 кодовая комбинация 0111, соответствующая

сигнальной точке 11, заменяется на кодовую комбинацию 0011, соответствующую точке 19.

Аналогичные действия производятся при приеме сигнальной точки, под номером 27 и в результате решения в потоках d6d5d4d3 кодовая комбинация

0010, соответствующая сигнальной точке 27, заменяется на кодовую комбинацию 0011, соответствующую точке 19.

Таким образом, реализованный в рассматриваемой аппаратуре кодем (кодер и модулятор), в котором избыточное кодирование введено с учетом расположения сигнальных точек на фазово-амплитудной плоскости модулятора, позволяет при малой избыточности кода 10Мбит/с/ 165Мбит/с 6% получить высокую исправляющую способность. Так, если без введения корректирующего кода (FEC) вероятность ошибки в стволе составляет PB = 10-

6, то с введением такого корректирующего кода – PB 10-9.

210