- •Федеральное агентство связи

- •«Поволжский государственный университет телекоммуникаций и информатики»

- •Системы и сети передачи дискретных сообщений

- •1. Принципы построения и основные характеристики систем передачи дискретных сообщений

- •1.1. Основные понятия: информация, сообщение, сигнал

- •1.2. Первичное кодирование дискретных сообщений

- •1.3. Основные преобразования в системе пдс

- •1.4. Структурная схема системы пдс

- •1.5. Стыки в системах пдс

- •1.6. Способы передачи и обработки сигналов в системах пдс

- •1.7. Внешние и внутренние параметры систем пдс

- •2. Характеристики каналов систем передачи дискретных сообщений

- •2.1. Непрерывные каналы связи

- •2.2. Дискретный канал непрерывного времени и искажения единичных

- •2.2.1. Аналитическое описание краевых искажений

- •2.2.2. Аналитическое описание дроблений

- •2.3. Методы регистрации единичных элементов.

- •2.3.1. Регистрация методом стробирования

- •2.3.2. Интегральный метод регистрации

- •2.3.3. Комбинированный метод регистрации

- •2.3.4. Регистрация со стиранием

- •2.4. Классификация и основные характеристики дискретных каналов

- •2.4.1. Пропускная способность дискретного канала

- •2.5.Основные аналитические модели дискретных каналов

- •2.5.1 Модель канала с независимыми ошибками

- •2.5.2. Модель неоднородного канала

- •2.5.3. Двухпараметрическая модель(модель вкас, модель Пуртова)

- •3.Методы сопряжения источников дискретных сообщений с дискретными каналами

- •3.1 Основы эффективного кодирования

- •3.2. Метод Шеннона-Фано

- •3.3. Метод Хаффмена

- •3.4.Особенности сопряжения источников дискретных сообщений с асинхронными и синхронными дискретными каналами

- •3.4.1. Сопряжение синхронного оу с синхронным дк

- •3.4.2. Сопряжение стартстопных оу с синхронным дк (метод наложения)

- •3.4.3. Сопряжение стартстопных оу с синхронными дк (метод скользящего индекса)

- •1 Зоне – 00

- •2 Зоне – 01

- •3 Зоне – 10

- •4 Зоне – 11

- •4.Принципы построения и техническая реализация корректирующих кодов

- •4.1 Основные характеристики спдс

- •4.2. Классификация методов повышения верности

- •4.3 Системы пдс без ос с многократным повторением

- •4.4. Системы пдс без ос с корректирующими кодами

- •Для биномиальной модели дискретного канала

- •4.3.1. Декорреляция ошибок в системах пдс

- •4.4. Принципы помехоустойчивого кодирования

- •4.5. Основные характеристики помехоустойчивых кодов

- •4.6. Классификация помехоустойчивых кодов

- •4.7. Коды Хемминга

- •4.8. Матричное представление кодов с поэлементным формированием проверочных разрядов

- •4.10 Техническая реализация кодов Хэмминга

- •1 Dc 1

- •1 2 3 4 5 6 7 8 9

- •4.11. Циклические коды

- •4.12. Выбор образующего полинома

- •4.13. Определение места ошибки в кк циклического кода

- •4.14 Матричное представление кодов с формированием проверочных элементов в целом

- •4.15 Техническая реализация циклических кодов

- •4.16. Итеративные коды

- •5. Адаптация в системах передачи дискретных сообщений

- •5.1. Принципы адаптации. Классификация систем пдс с ос

- •5.2 Основные параметры систем с ос.

- •5.3 Система пдс с рос – ож. Алгоритм работы.

- •5.4. Структурная схема системы пдс с рос – ож.

- •5.5 Основные параметры системы рос-ож

- •5.6. Система пдс с рос-пп (нп)

- •5.7. Алгоритмы работы систем пдс с рос-пПбл

- •5.8. Структурная схема системы рос-пПбл

- •5.9. Параметры системы рос-пПбл

- •5.10. Системы пдс с рос и накоплением правильно принятых комбинаций

- •5.11. Система пдс с рос и адресным переспросом ( рос – ап)

- •5.12. Сравнение методов повышения верности в системах пдс

- •6. Методы и устройства синхронизации и фазирования

- •6.1. Задачи синхронизации и фазирования в системах пдс

- •6.2. Классификация методов реализации утс

- •6.3. Резонансные утс

- •6.4. Замкнутые утс с непосредственным воздействием на задающий генератор (зг)

- •6.5. Замкнутые утс без непосредственного воздействия на зг

- •6.6. Влияние погрешности тактовой синхронизации на достоверность приема

- •6.8. Системы фазирования по циклам. Предъявляемые требования

- •6.9. Классификация уцф.

4.15 Техническая реализация циклических кодов

Для умножения и

деления многочленов, при реализации

кодеров и декодеров циклических кодов,

используются регистры сдвига. Для

умножения применяются обычные регистры,

а для деления на Р(х) – регистры сдвига

с обратными связями. При реализации

кодеков циклических кодов для построения

регистров сдвига с обратными связями

используют три правила:

Для умножения и

деления многочленов, при реализации

кодеров и декодеров циклических кодов,

используются регистры сдвига. Для

умножения применяются обычные регистры,

а для деления на Р(х) – регистры сдвига

с обратными связями. При реализации

кодеков циклических кодов для построения

регистров сдвига с обратными связями

используют три правила:

Число ячеек регистра сдвига с обратными связями равно степени образующего полинома.

Число сумматоров по модулю 2 равно весу образующего полинома минус 1

Сумматоры по модулю 2 ставятся перед не нулевыми членами образующего полинома (сумма по модулю 2 старших разрядов делимого и делителя всегда равна нулю – смотри любой пример)

Построение кодера и декодера рассмотрим на примере.

Пример. Циклический код (7,4),d0=3. Р(х)→ х3+х+1. Построить кодер и декодер

Решение. Структурная схема кодера представлена на рисунке 4.11

Вход Р3 Выход

1 2 3

Кл.1

РС

1 х х2 х3

1 2 3

Кл.2

Рис. 4.11

Схема кодера состоит из регистра задержки и регистра сдвига с обратными связями.

В регистре задержки производится умножение комбинации исходного кода на хr. Число ячеек в РЗ равно степени образующего полинома. У нас r=3 и 3 ячейки в РЗ

В

регистре сдвига (РС) обеспечивается

деление на образующий полином. Число

ячеек РС=3, т.к. r=3;

число

![]() =2, т.к.r=3

и -1=2;

=2, т.к.r=3

и -1=2;

![]() стоят перед х0(1)

и х; перед х3

ставить

стоят перед х0(1)

и х; перед х3

ставить

![]() не надо.

не надо.

Работа схемы происходит следующим образом.

Члены исходного полинома Q(х) простого кода вводятся одновременно в РС и РЗ. При этом Кл.1 замкнут, а Кл.2 разомкнут. Из РС выводится остаток от предыдущего деления. Через r тактов (у нас 3) и РЗ, и РС заполнятся и старший член Q(x) окажется в 3 ячейке и РЗ, и РС.

Далее Кл.1 размыкается, а Кл.2 замыкается, создавая цепь обратной связи. С этого момента (с 4 такта) начинается деление Q(x)* хr на Р(х); и вывод информационной части из РЗ. Через k-тактов (у нас k=4) процесс деления в РС закончится, а из РЗ выйдут все информационные разряды.

После этого Кл.1 замыкается, а Кл.2 размыкается. Из РС остаток за r тактов (r=3)передается так в канал. В то же время и РС и РЗ заполняются новой КК простого кода.

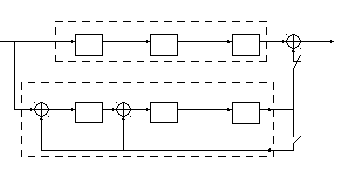

Структурная схема декодера представлена на рис. 4.12

Вход РН Выход

12 3 4 5 6 7

1 х х2х3 DC

1 2 3

PC

Рис.4.12

Декодер состоит из регистра накопителя (РН), регистра сдвига (РС), дешифратора и сумматора по модулю 2, исправляющего ошибки.

В РН число ячеек определяется длиной КК циклического кода.

РС строится аналогично РС в кодере.

ДС настроен на синдром, указывающий на ошибки в 7 разряде (старшем).

Алгоритм исправления ошибок в данном случае (при исправлении однократной ошибки) будет проще, чем рассмотренный ранее.

Действительно, можно записать:

![]()

F(x)= F(x)+E(x), где

![]()

F(x)- принятая КК

F(x)- переданная КК

E(x)- полином, вектор ошибок

![]()

Если F(x), то Е(х)=0,т.е. ошибок нет. Единица в Е(х) указывает на номер разряда, где произошла ошибка.

Исправление ошибки происходит следующим образом. Пусть после деления принятой КК получился остаток 101 (смотри образующую матрицу в примере- последняя строка), он соответствует ошибке в старшем разряде (7). В этот момент все 7 разрядов КК будут зафиксированы в РН. Со следующим тактом старший разряд КК поступает в сумматор по модулю 2. дешифратор настроен на эту комбинацию (101). Т.е. на его выходе появится 1. Она складывается со старшим разрядом КК и ошибка исправляется.

Если ошибка произошла во втором от старшего разряде, то на первом такте остаток будет 111 и дешифратор не сработает. Однако на втором такте вектор ошибки опять будет таким же, как и на первом такте. Поэтому и остаток будет 101. Сработает дешифратор и ошибка во втором разряде исправляется.

Также происходит и исправление ошибок в других разрядах.

При реализации дешифраторов для исправления многократных ошибок используется алгоритм в 4.13.