- •Основы теории передачи данных

- •Лекция 1 История развития техники передачи дискретных сообщений

- •Особенности систем дискретной связи

- •Структурная схема системы передачи дискретной информации

- •Виды систем передачи дискретной информации

- •Понятие кодирования

- •Основные понятия в области кодирования

- •Параметры кодов

- •Классификация кодов

- •Стандартные первичные коды

- •1. Стандартный пятиэлементный код

- •2. Стандартный семиэлементный код

- •Лекция 2 Понятие о дискретной модуляции

- •Основные понятия дискретной модуляции

- •Виды дискретной модуляции

- •1. Виды параметрической модуляции. Несущий сигнал - постоянный ток

- •Несущий сигнал - переменный ток

- •2. Относительная модуляция

- •Способы увеличение пропускной способности канала с использованием свойств дискретной модуляции

- •Прохождение дискретного канала по каналу связи Общие сведения о линиях и каналах связи

- •Проводные и кабельные каналы

- •Радиолинии и радиоканалы

- •Перспективные типы линий и каналов

- •Способы передачи сигнала по каналу связи

- •Сочетание последовательного и параллельного методов передачи сигнала по каналу связи

- •Распределители. Основные характеристики

- •Лекция 3 Общие сведения о каналах связи для передачи дискретных данных

- •Способы повышения пропускной способности канала связи

- •Скорость передачи дискретной информации

- •Виды помех в канале связи

- •Механизм появления искажений импульсов

- •Классификация искажений

- •Характеристика искажений преобладания

- •Характеристика характеристических искажений

- •Характеристика случайных краевых помех

- •Закон распределения вероятностей искажений

- •Лекция 4 Прием элементов дискретных сигналов Понятие регистрации сигнала

- •Метод стробирования

- •Интегральный метод регистрации

- •Понятие об ошибках. Поток ошибок

- •Классификация ошибок

- •Коэффициенты ошибок

- •Расчет вероятности ошибок

- •Математические модели ошибок

- •Общие сведения об измерении искажений и ошибок

- •Методика измерения искажений

- •Методика измерения ошибок

- •Лекция 5 Методы повышения верности передачи дискретных данных

- •Избыточность сигналов дискретной информации

- •Методы повышения верности передачи дискретных данных в системах без обратной связи

- •Методы повышения верности передачи дискретных данных в системах с обратной связью

- •Принципы помехоустойчивого кодирования

- •Доля ошибок, обнаруживаемых корректирующим кодом

- •Доля ошибок, исправляемых корректирующим кодом

- •Кодовое расстояние

- •Связь расстояния Хэмминга и корректирующих свойств кода

- •Определение требуемого числа проверочных разрядов

- •Классификация помехоустойчивых кодов

- •Лекция 6 Коды Хэмминга Общие сведения

- •Понятие синдрома

- •Построение кода Хэмминга

- •Понятие проверочной матрицы

- •Обнаружение ошибок кодом Хэмминга (9,5)

- •Понятие порождающей матрицы

- •Связь порождающей и проверочной матриц кода Хэмминга

- •Матричное построение систематических кодов с поэлементным формированием проверочной группы

- •Дуальные коды

- •Лекция 7 Циклические коды Общие сведения

- •Построение разрешенных комбинаций циклического кода

- •Обнаружение ошибок при циклическом кодировании

- •Определение места ошибки. Выбор образующего полинома

- •Матричное представление циклических кодов

- •Общие сведения об итеративном коде

- •Метод исправления ошибок. Порождающая матрица итеративного кода

- •Лекция 8 Принципы построения кодирующих устройств Код с поэлементным формированием проверочной группы

- •Кодирующее устройство циклического кода

- •Принципы использования детекторов качества сигналов

- •Понятие о непрерывных и сверточных кодах

- •Содержание

Метод исправления ошибок. Порождающая матрица итеративного кода

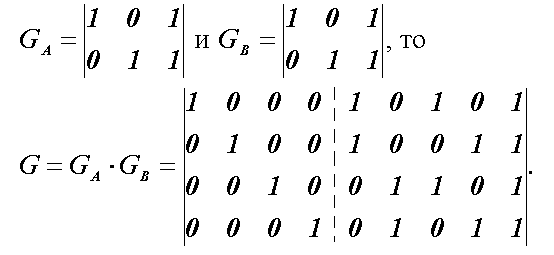

Если не выполняется проверка на четность для i-й строки и j-го столбца то элемент, стоящий на пересечении i-й строки и j-го столбца заменяется на обратный. При использовании в качестве итерируемых кодов систематических кодов к итеративному коду также применим матричный способ описания. Можно показать, что порождающая матрица итеративного кода, использующего два систематических кода с порождающими матрицами GA и GB, равна G = GAGB, где GAGB есть векторное произведение порождающих матриц. Так, если, например,

Такая матрица позволяет сформировать код n=9, k=4, d0=4.

Даже простейший итеративный код обладает высокими обнаруживающими способностями. При действии пакетов ошибок обнаруживается любой пакет ошибок длиной l+1 и менее, где l - длина строки.

Существенным недостатком итеративных кодов, использующих проверки на четность, является их избыточность, составляющая обычно 15 -20% и значительно превышающая избыточность эквивалентных по свойствам циклических кодов. Однако при использовании программных методов кодирования и декодирования с помощью ЭВМ проще работать с итеративными кодами. Поэтому на практике они широко используются в системах передачи данных.

Лекция 8 Принципы построения кодирующих устройств Код с поэлементным формированием проверочной группы

Шифратор

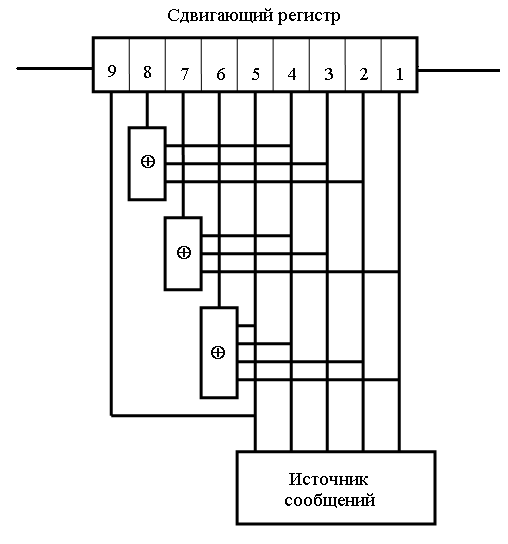

Аппаратурная реализация шифратора, обеспечивающего определение вида проверочных элементов кодовой комбинации, может быть выполнена с помощью структурной схемы, приведенной на рисунке. В данном случае рассмотрен вариант кода (9,5). В основу схемы положен сдвигающий регистр на n ячеек. В первые k ячеек регистра (k=5) записываются значения информационных элементов кодовой комбинации, поступающие в параллельном коде непосредственно из источника сообщений.

Проверочные элементы записываются в остальные r ячеек (r=4), где они формируются по ранее определенному правилу, т. е. в соответствии с условными номерами информационных элементов, составляющих проверочные группы. Эти правила для кода Хемминга (9,5) рассмотрены ранее и имеют вид:

(*)

(*)

Так, в ячейку 6 регистра следует записать проверочный элемент b4. Значение этого элемента (0 или 1) определяется суммированием по модулю 2 информационных элементов a1, a2, a4, a5 и т. д.

2. Декодер

В приемном устройстве решаются следующие задачи:

преобразование последовательного n-элементного кода в параллельный и запись кодовых комбинаций в ячейки параллельного регистра;

анализ принятых кодовых комбинаций с целью выявления ошибки и определения ее места;

исправление обнаруженной ошибки;

преобразование исправленной информационной группы элементов в последовательный k-элементный код.

Преобразование последовательного кода в параллельный осуществляется электронными преобразователями различных видов, например, сдвигающим регистром. Таким образом, в конце очередной n-разрядной кодовой комбинации значения ее элементов записываются в регистре. Из ячеек регистра кодовая комбинация поступает в устройство анализа и исправления ошибок, которое выполняет функции дешифратора.

а) Обнаружение ошибки

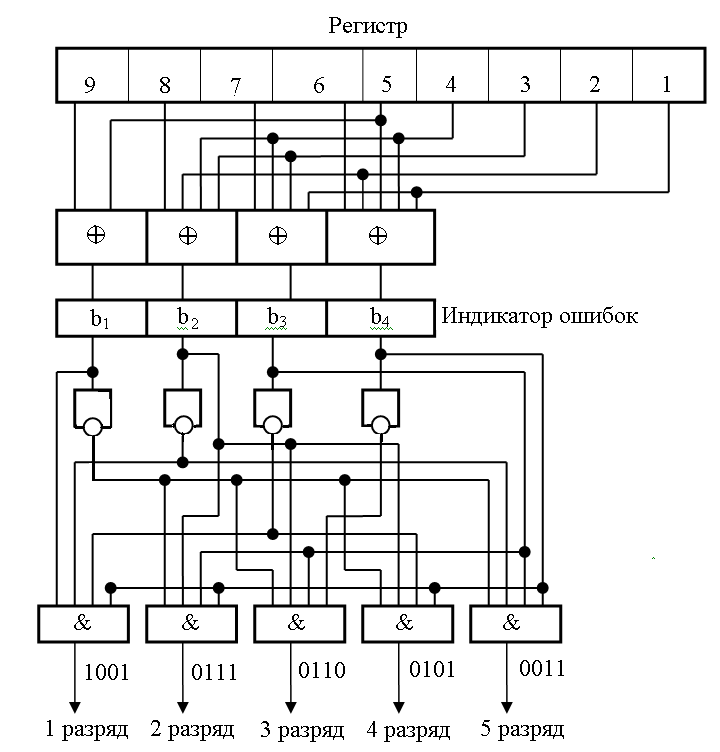

Структурная схема декодера кода (9,5) приведена на рисунке. С ячеек девятиразрядного запоминающего регистра элементы кодовой комбинации поступают в устройство анализа, в качестве которого используются сумматоры по модулю 2. На каждый из r сумматоров (число сумматоров равно числу проверочных элементов кодовой комбинации, т.е. в примере их 4) поступают соответствующий принятый проверочный элемент b'i (разряды регистра 6 – 9) и та совокупность информационных элементов, которая определяет его значение в соответствии с требованиями проверок (см. выражения (*)). Так, на сумматор № 1 поступает принятый проверочный элемент b'4, а также информационные элементы а1, а2, а4, а5. На сумматор № 2 поступает принятый проверочный элемент b'3, и информационные элементы а1, а3, а4 и т.д.

Результаты суммирования (0 либо 1) записываются в ячейки r-разрядного параллельного регистра, выполняющего функции индикатора ошибок. На выходе индикатора ошибок может появиться одно из 2r-1 двоичных чисел, определяющих условный номер ошибочно принятого элемента. В данном примере таких чисел может быть только 9, т.к. кодовая комбинация имеет только 9 элементов.

На практике отмечаются только ошибки, возникшие в информационной части кодовой комбинации. Для рассматриваемого случая (k=5) в индикаторе ошибок может быть записано только шесть двоичных чисел: 0000, 0011, 0101, 0110, 0111, 1001. Первое число указывает на отсутствие ошибок. Второе число указывают на наличие ошибки в первом элементе информационной части (условный номер элемента а3). Третье – на ошибку во втором элементе информационной части (условный номер элемента а5) и т.д. Т.о. двоичные числа определяют условный номер элемента, который использовался при составлении уравнений (*) при нахождении проверочных элементов кодовой комбинации.

Автоматическое определение номера элемента, в котором обнаружена ошибка, производится с помощью цифровых фильтров, настроенных на числа 0011, 0101, 0110, 0111, 1001. На выходе соответствующего фильтра сигнал возникает лишь в случае, когда в индикаторе ошибки записано двоичное число, соответствующее данному фильтру. Принцип построения таких фильтров ясен из схемы, где функции фильтра выполняет схема совпадения (схема И) на четыре входа.

Предположим, что ошибка произошла в старшем разряде информационной части кодовой комбинации (элемент с условным обозначением а3). В этом случае в индикаторе ошибок будет сформировано число 3 (0011). Чтобы это число дало отклик на выходе соответствующей схемы И (на рисунке – 5 разряд), необходимо обеспечить формирование единиц на всех ее четырех входах. Для этого с третьей и четвертой ячеек индикатора ошибок (ячейки b1, b2) следует подавать сигнал через инверторы (схема «НЕ»). Любое другое число, сформированное в регистре индикатора ошибок, не будет соответствовать настройке этой схемы И и отклика на ее выходе не даст.

б) Исправление ошибки

Процесс исправления ошибки сводится к изменению ошибочно принятого элемента кодовой комбинации. Это происходит в устройстве для исправления ошибок, которое представляет собой регистр сдвига, обеспечивающий наряду с исправлением ошибки преобразование параллельного кода в последовательный. Изменение ошибочно принятого информационного элемента осуществляется его суммированием по модулю 2 с единицей, формируемой на выходе схемы И устройства обнаружения ошибок, соответствующей данному элементу. Если ошибки нет, то на выходе схемы И будет нуль, при наличии ошибки — единица. В случае, когда ошибки нет (независимо от того нуль или единица представляют данный информационный элемент), суммирование элемента с нулем результата не изменит, т.к. 1 0=1; 0 0=0. Наличие ошибки изменит элемент на противоположный, т. е. 1 1=0; 0 1=1.

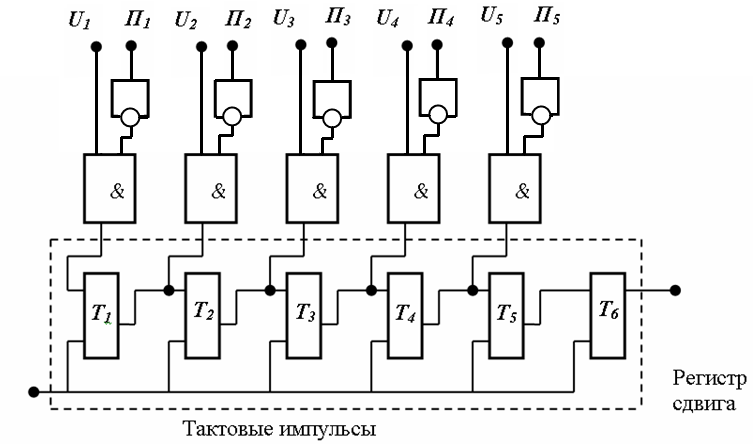

Суммирование по модулю 2 реализуется схемой совпадения (схема И), на входы которой соответственно поступают элемент информационной комбинации и напряжение, снимаемое с выхода схемы И устройства обнаружения ошибок после инвертирования схемой НЕ. Этот принцип иллюстрируется рисунком ниже. Буквой Ui обозначен элемент информационной комбинации i-го разряда, буквой Пi – элемент на выходе схемы Иi устройства обнаружения ошибок, которая контролирует Ui. Исправленные элементы поступают в ячейки регистра сдвига. Регистр сдвига устройства исправления ошибок содержит одну дополнительную ячейку. После записи в ячейки 1-5 регистра исправленные элементы продвигаются тактовыми импульсами. После первого тактового импульса на выход регистра поступит элемент 5-го разряда, затем 4-го и т.д.