- •Cистемы счисления.

- •Преобразование чисел из одной системы счисления в другую. Правила перевода целых чисел

- •Правила перевода правильных дробей

- •Правило перевода дробных чисел

- •Виды двоичных кодов

- •Беззнаковые двоичные коды.

- •Прямые знаковые обратные двоичные коды.

- •Знаковые дополнительные двоичные коды.

- •Правила выполнения простейших арифметических действий. Правила сложения

- •Правила вычитания

- •Правила умножения

- •Правила деления

- •Дополнительный код числа.

- •Алгоритм получения дополнительного кода отрицательного числа.

- •Представление вещественных чисел в компьютере.

- •Нормализованная запись числа.

- •Представление чисел с плавающей запятой.

- •Алгоритм представления числа с плавающей запятой.

- •Конвейерная организация

- •Определение понятия "архитектура"

- •Архитектуры cisc и risc

- •1.1. Основные определения

- •1.2. Обзор 32-разрядного микропроцессора

- •1.2.1. Основные блоки

- •1.2.2. Устройство управления памятью

- •1.2.3. Архитектура режима реальных адресов и защищенного режима

- •1.3. Типы данных

- •Арифметико-логическое устройство

- •Системная шина

- •Состав магистрали

- •Виды шин

- •Шина с тремя состояниями

- •Как происходят операции на магистрали?

- •Шина usb

- •Память эвм

- •Организация внутренней памяти процессора.

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •12.3.1. Статические озу (sram)

- •12.3.1.1. Элемент памяти ram в ттл-исполнении

- •Активация ячейки памяти

- •12.3.2.2. Особенности динамических озу

- •12.3.3.3. Некоторые виды озу

- •Современная оперативная память

- •12.6. Перепрограммируемые постоянные запоминающие устройства

- •Находящиеся на свету сппзу и reprom могут быть случайно стерты.

- •История Кэш-памяти

- •] Функционирование

- •Кэш центрального процессора

- •Уровни кэша

- •Ассоциативность кэша

- •Кэширование внешних накопителей

- •Организация кэш-памяти

- •1. Где может размещаться блок в кэш-памяти?

- •2. Как найти блок, находящийся в кэш-памяти?

- •3. Какой блок кэш-памяти должен быть замещен при промахе?

- •4. Что происходит во время записи?

- •Принцип действия флэш

- •Архитектура флэш-памяти.

- •Доступ к флэш-памяти

- •Последовательный асинхронный адаптер (com порт)

- •Принципы построения параллельного порта.

- •Чтение/запись в lpt порт (Часть 1)

- •Внутренности lpt порта

- •Запись/чтение данных в регистр Data

- •Запись/чтение данных в регистр Control

- •Запись/чтение данных в регистр Status

- •Понятие прерывания.

- •Подсистема прерываний мпс

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Классификация и структура микроконтроллеров

- •4.2. Процессорное ядро микроконтроллера

- •4.2.1. Структура процессорного ядра мк

- •4.2.2. Система команд процессора мк

- •4.2.3. Схема синхронизации мк

- •4.3. Память программ и данных мк

- •4.3.1. Память программ

- •4.3.2. Память данных

- •4.3.3. Регистры мк

- •4.3.4. Стек мк

- •4.3.5. Внешняя память

Типы и характеристики стандартных шин

Типы и характеристики стандартных шин, используемых в настоящее время, приведены в таблице 10.1.

Табл. 10.1

Характеристики стандартных шин.

Тип/назначение |

Разрядность |

Тактовая частота (МГц) |

Пропускная способность (Мб/с) |

ISA/общая |

16 |

8 |

16 |

EISA/общая |

32 |

8 |

33 |

VLB (VESA) |

32 |

40 |

130 |

VLB2/локальная |

64 |

40 |

400 |

PCI/ввод/вывод |

32 |

33, 66 |

120, 133 |

SBUS/ввод/вывод |

32, 64 |

20, 25 |

80, 100 |

MBUS/процессор-память |

64 |

50 |

125 (400) |

XDBUS/процессор-память |

64 |

50 |

310 (400) |

AGP/локальная графическая |

32 |

133 |

533 |

PCI-X |

64 |

133 |

1060 |

Системная шина ISA (Industry Standard Architecture) впервые стала применяться в ПК IBM PC/AT на базе процессора 12826. Данная шина позволяет передавать параллельно 16 бит данных и обращаться к 16 Мбайт системной памяти. В современных компьютерах используется как шина ввода/вывода для организации связи с медленно действующими периферийными устройствами. С появлением процессоров i386, i486 системная шина ISA стала "узким местом" ПК на их основе.

Системная шина EISA (Extended Industry Standard Architecture), разработанная в 1988 году, обеспечивает адресное пространство в 4 Гбайта, 32-битовую передачу данных, тактируется частотой около 8 Мгц, имеет максимальную теоретическую скорость передачи данных 33 Мбайт/с и совместима с шиной ISA.

Шина МСА также обеспечивает 32-разрядную передачу данных, тактируется частотой 10 МГц, но не совместима с шиной ISA и используется только в компьютерах компании IBM.

Локальная шина VESA-Local-Bus (VLB) предназначалась для увеличения быстродействия видеоадаптеров и контроллеров дисковых накопителей. Она подключалась непосредственно к процессору i486, и только к нему. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VLB версии 2, который предусматривает использование 64-битовой шины данных и увеличение количества разъемов расширения. Ожидаемая скорость передачи данных - до 400 Мбайт/сек.

Шина PCI (Peripheral Component Interconnection) в первом варианте использовалась как локальная шина и предназначалась для тех же целей, что и предыдущая шина (VLB). В действующем втором варианте шина PCI относится к шинам ввода/вывода. В данном случае соединение шин центрального процессора и PCI осуществляется через так называемую РС1-перемычку, мост PCI или контроллер, которые согласуют шину центрального процессора с шиной PCI. Это означает, что PCI может работать с процессорами различных платформ и поколений.

Шина VME приобрела большую популярность как шина ввода/вывода в рабочих станциях и серверах на базе RISC-процессоров. Эта шина высоко стандартизирована, имеет несколько версий этого стандарта: VME32, VME64.

В однопроцессорных и многопроцессорных рабочих станциях и серверах на основе микропроцессоров архитектуры SPARC одновременно используются несколько типов шин: Sbus, Mbus и XDBus, причем шина Sbus применяется в качестве шины ввода/вывода, a Mbus и XDBus — в качестве шин для объединения большого числа процессоров и памяти.

Локальная шина AGP (Accelerated Graphics Port) первоначально предназначалась исключительно для графики и была способна повысить производительность видео-приложений. Для использования технологии AGP необходим набор микросхем Intel 440LX, который позволяет разгрузить сравнительно "узкую" (133 Мб/с) шину PCI от жадного на ресурсы видеоадаптера и подключить последний к специально предназначенной для него более "широкой" (528 Мб/с) шине AGP. На долю же PCI остаются более медленные устройства, функционирование которых существенно улучшается благодаря отключению от шины более быстродействующих устройств, то и дело создающих "пробки" в стремительном потоке данных. Набор 440LX не только имеет поддержку AGP, но и допускает использование в машинах на базе Pentium II быстродействующей памяти SDRAM, которая обеспечивает более высокую производительность, чем ОЗУ типа EDO DRAM, применяемое в машинах Pentium II со старым набором микросхем.

PCI-X - расширение шины PCI, которая работает на тактовой частоте 133 МГц. Шина PCI-X обладает обратной совместимостью с PCI, требует нового набора микросхем Intel 450 NX, кроме того, благодаря новой схеме обмена регистр-регистр достигается пропускная способность 1,06 Гб/с (8 Гбит/с), что обеспечивает почти шестикратный выигрыш в производительности. В первую очередь PCI-X предназначена для подключения высокопроизводительных адаптеров типа Gigabit Ethernet, Ultra 3SCSI и Fibre Channel (FC-AL).

В целом же шинная архитектура настольного ПК нового (на ближайшие два-три года) поколения содержит несколько шин с различной пропускной способностью:

шины (1Гб/с), соединяющей ядро Pentium II с кэш-памятью второго уровня,

трех шин (528 Мб/с), соединяющих новый набор AGPset с ядром процессора, SDRAM и графическим акселератором,

шины PCI (133 Мб/с).

Применение такой шиной организации увеличивает быстродействие компьютеров при выполнении целочисленных операций, действий с плавающей запятой и работе с мультимедиа-приложениями.

Таймер. Интервальный таймер

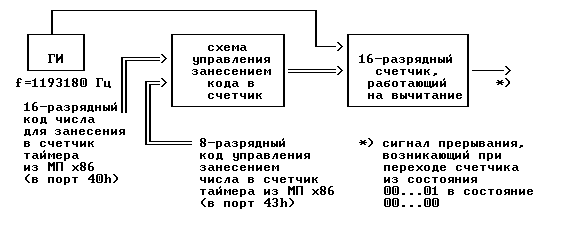

Другим аппаратным устройством, имеющим важнейшее значение для организации вычислительного процесса, является таймер. Его использование позволяет программно-аппаратным способом задавать программные события, наступающие по истечении заданного промежутка времени, считая от момента задания этих событий. Эти события реализуются путем выработки сигнала прерывания от таймера и включения соответствующего обработчика прерывания. Рассмотрим более подробно работу таймера на примере его устройства в ЭВМ типа IBM PC с МП типа 80х86.

Этот

таймер состоит из трех почти одинаковых

каналов – каналов "0", "1" и

"2". При работе программ главным

образом используется канал "0",

поэтому он и будет рассмотрен; на рис.1

приведена его схема. Генератор импульсов

(ГИ) вырабатывает с частотой f=1193180 Гц

непрерывную последовательность

импульсов, поступающих на импульсные

входы всех трех каналов. При каждом

поступлении импульса на вход 16-разрядного

счетчика из содержимого последнего

вычитается "1" и при переходе этого

счетчика из состояния 000...01 в состояние

000...00 вырабатывается сигнал прерывания,

поступающий в СПП для включения последним

программы-обработчика прерывания от

таймера. Если исходное состояние счетчика

таймера равно 00...0, то при поступлении

очередного импульса из ГИ состояние

счетчика становится равным 11...1 и далее

уменьшается на "1" при каждом

поступлении импульса из ГИ. В этом случае

сигнал прерывания будет выработан

таймером после поступления на его вход

65536 импульсов, т.е. по прошествии интервала

времени, примерно равного 55 мсек, что

соответствует частоте срабатывания

таймера, примерно равной 18,2 Гц. В случае,

если интервал времени срабатывания

таймера должен иметь меньшее значение,

чем 55 мсек, то в счетчик таймера необходимо

занести код, соответствующий числу

импульсов N, вычисляемому по формуле

![]() где F - требуемое значение частоты

срабатывания таймера, причем должно

выполняться неравенство F > 18,2 Гц.

Например, для F = 72,8 Гц получим, что N =

16389,8; округляя, получим, что в счетчик

таймера должен быть занесен двоичный

код 0 100 000 000 000 110.

где F - требуемое значение частоты

срабатывания таймера, причем должно

выполняться неравенство F > 18,2 Гц.

Например, для F = 72,8 Гц получим, что N =

16389,8; округляя, получим, что в счетчик

таймера должен быть занесен двоичный

код 0 100 000 000 000 110.

Занесение требуемого кода в счетчик таймера производится следующим образом. Сначала МП х86 должен выполнить команду программы, которая производит передачу в порт таймера с шестнадцатеричным номером 40h требуемый двоичный код. Затем МП х86 должен выполнить команду программы, которая производит передачу в порт таймера с шестнадцатеричным номером 43h байта, в котором указывается номер программируемого канала таймера, режим работы этого канала и количество передаваемых в счетчик таймера байтов - 1 или 2. После этого в запрограммированном канале таймера немедленно начинает функционировать сначала схема управления занесением кода в счетчик таймера и затем сам счетчик таймера в соответствии с полученным заданием.

Рассмотрим теперь работу программы, которую обычно называют интервальным таймером. Необходимость использования этой программы определяется тем обстоятельством, что в большинстве типов ЭВМ, в том числе и в ЭВМ типа IBM PC, используется только один таймер, хотя во многих случаях при функционировании достаточно сложных программ возникает необходимость организации нескольких параллельно существующих программ, которые должны быть включены в различные заранее определенные моменты времени. Один из возможных способов организации интервального таймера состоит в следующем. Этой программой, для управления процессом параллельного выполнения нескольких программ, в оперативной памяти составляется таблица, в которой для каждой из этих программ выделяется несколько строк, содержащих следующие параметры:

адрес начала i-й программы;

значение Т(i) интервала времени, по истечении которого должна быть включена эта программа, причем отсчет этого интервала начинается с момента организации интервальным таймером этой программы;

текущее значение интервала времени t(i), по истечении которого должна быть включена эта программа;

признак c(i) режима включения этой программы - циклический или разовый (пусть, например, с(i)=0 для разового режима).

Кроме того, в этой таблице должна быть еще одна строка, общая для всех программ, в которой содержится значение интервала времени Т, которое задано для текущего включения таймера.

Тогда при каждом включении программы-обработчика прерывания от таймера в этой таблице корректируются все интервалы времени, величина которых больше нуля, путем уменьшения их значений на величину Т. Если после корректировки окажется, что для каких-то программ величина t(i)=0 или t(i)<0, то должно быть организовано последовательное включение этих программ. Если для каких-то программ с(i)=1, то должно быть выполнено присвоение t(i)=T(i) и затем организовано очередное включение этих программ по истечении соответствующих им интервалов времени, равных t(i).

Таймеры предназначены для формирования временных интервалов, позволяя микропроцессорной системе работать в режиме реального времени.

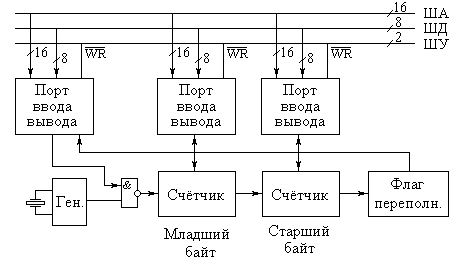

Таймеры представляют собой обычные цифровые счётчики, которые подсчитывают импульсы от высокостабильного генератора частоты. К системной шине микропроцессора таймеры подключаются при помощи параллельных портов.

Генератор частоты, входящий в состав таймера, определяет минимальный интервал времени, который может определять таймер. Интервалы времени, задаваемые таймером, могут устанавливаться только из дискретного набора допустимых времён. Дискретность установки этих интервалов времени тоже определяется частотой задающего генератора. Разрядность цифрового счётчика, входящего в состав таймера, определяет максимальный интервал времени, который может определять таймер.

Обычно используются 16-ти разрядные таймеры, поэтому, для подключения такого таймера к 8-ми разрядному процессору требуется два параллельных порта. Кроме того, таймером нужно управлять. Таймер нужно включать и выключать, часто требуется определять не возникало ли переполнение таймера (факт переполнения легко запомнить в дополнительном триггере, подключенном к выходу переноса счетчика таймера). Этот триггер называется флагом переполнения таймера. Триггер (флаг) включения и выключения таймера и флаг переполнения таймера подключают к системной шине микропроцессора через дополнительный порт ввода вывода.

Структурная схема таймера, построенного по описанным выше принципам, приведена на рисунке 1.

Рисунок 1. Структурная схема таймера.

В зависимости от типа использованного цифрового счетчика таймеры бывают суммирующие или вычитающие. Если в таймере используется суммирующий счётчик, то таймер называется суммирующим. Если в таймере используется вычитающий счётчик, то таймер называется вычитающим.

Использование вычитающего счётчика позволяет проще задавать интервалы времени. В этом случае записываемый в таймер код будет соответствовать интервалу времени:

![]()

В случае использования суммирующего таймера код, записываемый в таймер для задания интервала времени, определяется из другой формулы:

![]()

В этой формуле код, который заносится в таймер, представляет собой дополнение кода интервала времени до максимального кода, который можно записать в таймер. Максимальный код таймера определяется по разрядности таймера. В рассмотренном примере разрядность таймера равна 16. Это означает, что максимальный код равен 65535.

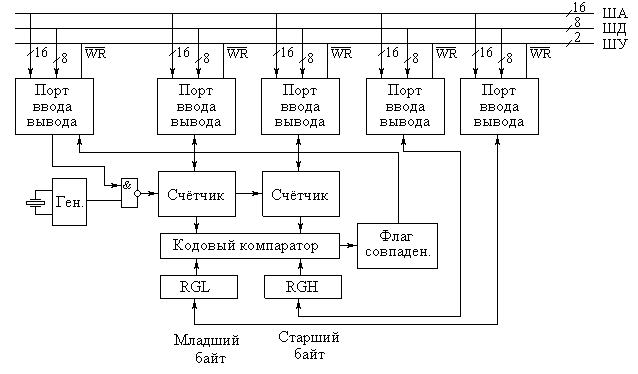

Достаточно часто суммирующие таймеры используются в режиме свободнобегущего таймера. Схема такого таймера приведена на рисунке 2.

Рисунок 2. Структурная схема свободнобегущего таймера с модулем сравнения.

Свободнобегущие таймеры используются как системные часы, задающие время внутри микропроцессорной системы. Для задания промежутков времени микропроцессор считывает значение текущего системного времени и суммирует с ним код задаваемого промежутка времени. Полученный результат записывается в регистр сравнения таймера. При совпадении значений таймера и регистра сравнения устанавливается флаг совпадения. Значение этого флага можно определить программным опросом или воспользоваться механизмом прерывания работы процессора.

Часто с одним свободно бегущим таймером работает несколько модулей сравнения. В этом случае они образуют набор модулей сравнения (PCA). Практически все современные микроконтроллеры и сигнальные процессоры оснащены таймерами с такими наборами модулей.

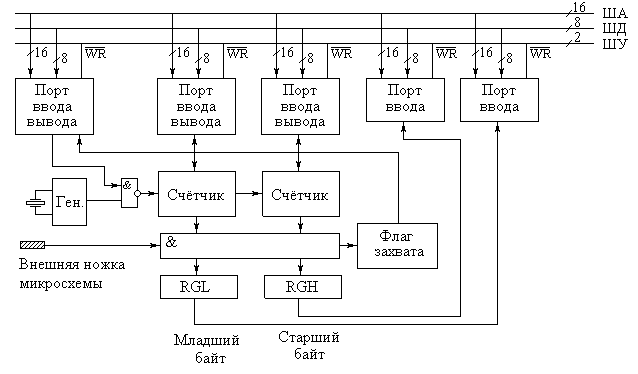

Кроме модулей сравнения с свободнобегущим таймером работают модули захвата, которые позволяют аппаратно запоминать время какого-либо внешнего события без участия центрального процессора. Структурная схема свободнобегущего таймера с модулем захвата приведена на рисунке 3.

Рисунок 3. Структурная схема свободнобегущего таймера с модулем захвата.