- •Cистемы счисления.

- •Преобразование чисел из одной системы счисления в другую. Правила перевода целых чисел

- •Правила перевода правильных дробей

- •Правило перевода дробных чисел

- •Виды двоичных кодов

- •Беззнаковые двоичные коды.

- •Прямые знаковые обратные двоичные коды.

- •Знаковые дополнительные двоичные коды.

- •Правила выполнения простейших арифметических действий. Правила сложения

- •Правила вычитания

- •Правила умножения

- •Правила деления

- •Дополнительный код числа.

- •Алгоритм получения дополнительного кода отрицательного числа.

- •Представление вещественных чисел в компьютере.

- •Нормализованная запись числа.

- •Представление чисел с плавающей запятой.

- •Алгоритм представления числа с плавающей запятой.

- •Конвейерная организация

- •Определение понятия "архитектура"

- •Архитектуры cisc и risc

- •1.1. Основные определения

- •1.2. Обзор 32-разрядного микропроцессора

- •1.2.1. Основные блоки

- •1.2.2. Устройство управления памятью

- •1.2.3. Архитектура режима реальных адресов и защищенного режима

- •1.3. Типы данных

- •Арифметико-логическое устройство

- •Системная шина

- •Состав магистрали

- •Виды шин

- •Шина с тремя состояниями

- •Как происходят операции на магистрали?

- •Шина usb

- •Память эвм

- •Организация внутренней памяти процессора.

- •Методы управления памятью без использования дискового пространства (без использования внешней памяти).

- •Организация виртуальной памяти.

- •Страничное распределение.

- •Сегментное распределение.

- •Странично - сегментное распределение.

- •12.3.1. Статические озу (sram)

- •12.3.1.1. Элемент памяти ram в ттл-исполнении

- •Активация ячейки памяти

- •12.3.2.2. Особенности динамических озу

- •12.3.3.3. Некоторые виды озу

- •Современная оперативная память

- •12.6. Перепрограммируемые постоянные запоминающие устройства

- •Находящиеся на свету сппзу и reprom могут быть случайно стерты.

- •История Кэш-памяти

- •] Функционирование

- •Кэш центрального процессора

- •Уровни кэша

- •Ассоциативность кэша

- •Кэширование внешних накопителей

- •Организация кэш-памяти

- •1. Где может размещаться блок в кэш-памяти?

- •2. Как найти блок, находящийся в кэш-памяти?

- •3. Какой блок кэш-памяти должен быть замещен при промахе?

- •4. Что происходит во время записи?

- •Принцип действия флэш

- •Архитектура флэш-памяти.

- •Доступ к флэш-памяти

- •Последовательный асинхронный адаптер (com порт)

- •Принципы построения параллельного порта.

- •Чтение/запись в lpt порт (Часть 1)

- •Внутренности lpt порта

- •Запись/чтение данных в регистр Data

- •Запись/чтение данных в регистр Control

- •Запись/чтение данных в регистр Status

- •Понятие прерывания.

- •Подсистема прерываний мпс

- •Интерфейсы ввода-вывода

- •Классификация интерфейсов

- •Типы и характеристики стандартных шин

- •Классификация и структура микроконтроллеров

- •4.2. Процессорное ядро микроконтроллера

- •4.2.1. Структура процессорного ядра мк

- •4.2.2. Система команд процессора мк

- •4.2.3. Схема синхронизации мк

- •4.3. Память программ и данных мк

- •4.3.1. Память программ

- •4.3.2. Память данных

- •4.3.3. Регистры мк

- •4.3.4. Стек мк

- •4.3.5. Внешняя память

12.3.1. Статические озу (sram)

12.3.1.1. Элемент памяти ram в ттл-исполнении

Статические ОЗУ могут быть построены на биполярных транзисторах. Используется известная ТТЛ-технология (см. гл. 6 «Семейства схем»). Основой ячейки является триггер на двух мультиэмиттерных транзисторах согласно рис. 12.17. Триггер управляется Х-адресной шиной, 7-адресной шиной и двумя разрядными линиями записи—считывания. Такой элемент памяти может запомнить 1 бит. Элемент содержит значение 1, если Тх открыт, а Т2 заперт. И значение 0, если Т2 открыт, а Тх заперт.

Активация ячейки памяти

Если на обоих адресных шинах X и Г действует 0-сигнал (О В, заземление), то ячейка памяти не активирована. Ток эмиттера открытого транзистора течет на землю. По разрядным линиям SLV SL2 ток не протекает.

Если

только на одной адресной шине действует

1-сигнал, то элемент памяти остается

неактивным, так как эмиттерный ток

открытого транзис-

Если

только на одной адресной шине действует

1-сигнал, то элемент памяти остается

неактивным, так как эмиттерный ток

открытого транзис-

тора может протекать через другую адресную шину. Только когда по обеим адресным шинам проходит 1-сигнал, то есть +5 В, элемент памяти активируется, и эмиттерный ток открытых транзисторов течет по соответствующим линиям записи—чтения.

Чтение

После активации элемента памяти по iSX-линиям течет ток открытого транзистора. На рис. 12.17 транзистор Т2 открыт. Ток эмиттера протекает через

SL2 и на выходе Q через усилитель выдает 1-сигнал. Элемент памяти сохранил значение 0. Если после активации ток протекает по линии SLV то элемент памяти сохранил значение 1.

Запись

Для записи 1 в элемент, содержащий 0, необходимо подать 1-сигнал или +5 В на SL2 и 0-сигнал, или 0 В на SLV При хранении 0 проводит транзистор Т2. Он запирается после подачи на его третий эмиттер, подключенный к SLV +5 В. Транзистор Тх открывается, и его эмиттерный ток может течь через SLV После завершения активации элемент памяти сохраняет это состояние.

Для записи 0 в элемент, содержащий 1, необходимо подать 1-сигнал или +5 В на SLl и 0-сигнал, или 0 В на SL2. Триггер переключится по алгоритму, описанному выше, и сохранит значение 0.

Элементы памяти на ТТЛ-элементах работают очень быстро. Но зато они отличаются высоким энергопотреблением.

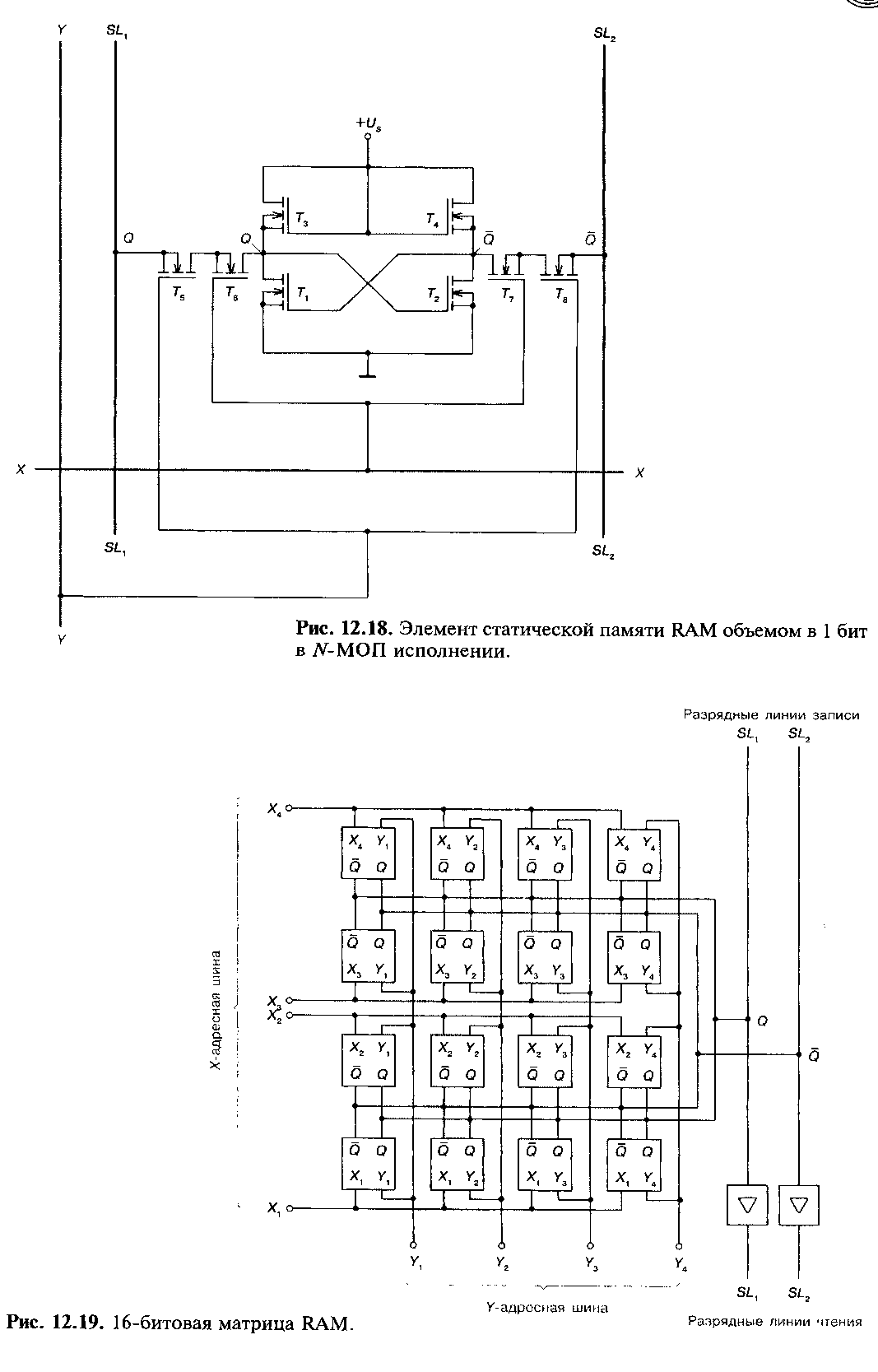

72.3.1.2. Элементы памяти RAM в Ы-МОП-исполнении

Элементы памяти RAM в TV-МОП-исполнении имеют по сравнению с ТТЛ-элементами существенные преимущества. Они потребляют меньше энергии и могут производиться с более высокой степенью интеграции. На квадратном миллиметре чипа может размещаться больше МОП-элементов памяти. Однако МОП-схемы имеют большее время переключения, т. е. они медленнее ТТЛ-схем (см. гл. 6 «Семейства схем»).

Структура типичного RAM-элемента представлена на рис. 12.18. Транзисторы Т{ и Т2 собраны по схеме триггера. Транзисторы Т3 и Т4 работают вместо нагрузочных сопротивлений. Если Тг заперт, а Т2 открыт, то элемент памяти сохранил значение 1. При 0 Ту открыт, а Т2 заперт.

Активация элемента памяти

Элемент активизируется, если на адресные шины Хи Глодается 1-сигнал. Транзисторы Г5, Г6, Т7 и Г8 открываются и соединяют выходы триггера Q и

Q с линиями чтения—записи SLX и SL2.

Чтение

После активации ячейки памяти из нее можно считывать данные. Если SLX проводит 1-сигнал, то элемент сохраняет единицу. Если SL2 проводит 1-сигнал, то элемент сохраняет 0.

Запись

В элемент памяти, содержащий 0, требуется записать 1. При О Тх открыт, а Т2 заперт. Если на SL2 действует 0-сигнал, то Тх запирается, а Т2 открывается. Триггер переключается в 1-состояние. Это состояние сохраняется после завершения активации.

72.3.7.3. Структура RAM с двухкоординатной адресацией

RAM-элементы памяти собираются в RAM-матрицы памяти. Матрица на рис. 12.19 имеет объем памяти 16 бит. Каждый элемент доступен индивидуально. Говорят, что каждый бит может быть адресован. Если бы мы хотели узнать, например, содержимое памяти запоминающего элемента 8, то на адресных шинах Х3 и Y4 должен быть 1-сигнал. На разрядных линиях SLX и

SL2 появляются выходные сигналы Q и Q.

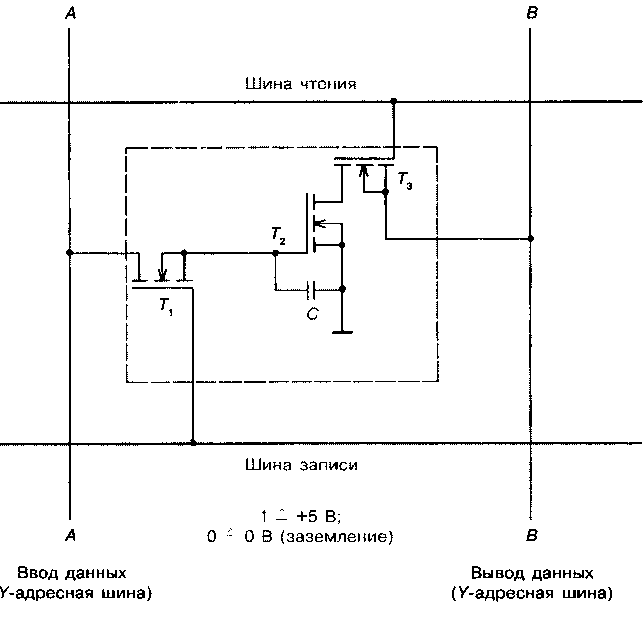

12.3.2. Динамические ОЗУ (DRAM)

12.3.2.1. Элемент памяти динамического ОЗУ

Типичный элемент памяти динамического ОЗУ состоит из трех самозапирающихся MOS-FET-транзисторов согласно рис. 12.20. Информация сохраняется в емкости С. Если С заряжен, то элемент памяти содержит 1. Если С не заряжен, то элемент памяти содержит 0.

Запись

l

l

X

Рис.

12.20.

Типичный

элемент памяти динамической RAM.

Вследствие этого транзистор Тх открывается (низкоомен между истоком и стоком). При подаче на информационный вход 1-сигнала емкость С заряжается. Значение 1 сохранено. При заряженном конденсаторе С транзистор Т2 всегда низкоомен (открыт). Если на адресной шине X действует 0-сигнал, то элемент памяти больше не активизирован. Транзистор Тх запирается и предотвращает утечку заряда С. Для записи 0 следует активизировать элемент памяти (1-сигнал на адресной шине X). При этом Тх отпирается. Если 0-сигнал (0 = О В, земля) прикладывается на линию входных данных А, то емкость С может разрядиться через транзистор Tv Значение 0 сохранено. При разряженном конденсаторе С транзистор Т2 всегда заперт.

Чтение

Для считывания данных на шину вывода В прикладывается 1-сигнал (+ 5 В). Элемент памяти активизируется через шину чтения L. На L также прикладывается 1. При этом транзистор Т3 открывается.

Если записана 1, то транзистор Тъ открыт и ток через шину В через Г3 и Т2 течет на землю. Это признак записанной 1.

Если записан 0, то С разряжен, а Т2 заперт. Через шину В ток течь не может. Это признак записанного 0.

Во время чтения содержание элемента памяти не меняется.

Регенерация

Емкость С очень мала. Она составляет в зависимости от степени интеграции от 0,1 пФ до 1 пФ. Соответственно мал и сохраненный заряд. Очень маленький ток утечки быстро понижает заряд. Поэтому заряд должен быть через короткие промежутки времени снова восстановлен. Обычно подзарядка происходит каждые 2 мс.

Цикл регенерации начинается с чтения содержимого элемента памяти. Если оно равно 1, то Тх открывается и С заряжается. Если содержание памяти 0, то зарядка не происходит.

Для регенерации необходим особенный задающий генератор синхронизирующих импульсов и схема управления. Оба этих элемента включены в состав микросхем.