Давыд Цуриков. Диссертация. 2015 г

..pdf

|

|

|

|

|

91 |

|

|

|

|

|

|

димости вместо «узлового» идентификатора используется «рукавный», так как в силу со- |

|||||||||||

глашений подраздела 2.2.1 он однозначно определяет структуру матрицы: |

|

||||||||||

|

|

|

|

σ[0,3,2]00 σ[0,3,2]03 σ[0,3,2]02 |

|

||||||

|

|

σ sw |

=σ[0,3,2] = σ[0,3,2]30 σ[0,3,2]33 σ[0,3,2]32 |

|

(264) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[0,3,2]20 |

σ |

[0,3,2]23 |

σ |

[0,3,2]22 |

|

|

|

|

|

|

σ |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

0,6 |

|

|

|

|

|

|

0,4 |

|

|

|

|

|

|

|

|

|

|

μA |

|

|

|

1 |

μA |

0,4 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

2 |

|

|

|

|

|

2 |

||

J, |

0,2 |

|

|

J, |

|

|

|

|

|

||

|

|

|

0,2 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

0 |

20 |

|

40 |

|

|

0 |

|

|

20 |

40 |

|

|

U||, mV |

|

|

|

|

|

|

U||, mV |

|

|

|

|

|

|

|

c |

|

|

|

|

|

|

|

|

|

1,5 |

|

|

|

|

|

|

|

|

|

|

μA |

1,0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

J, |

|

|

|

|

|

|

|

|

|

|

|

0,5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

20 |

|

|

40 |

|

|

||

|

|

|

|

|

U||, mV |

|

|

|

|

|

|

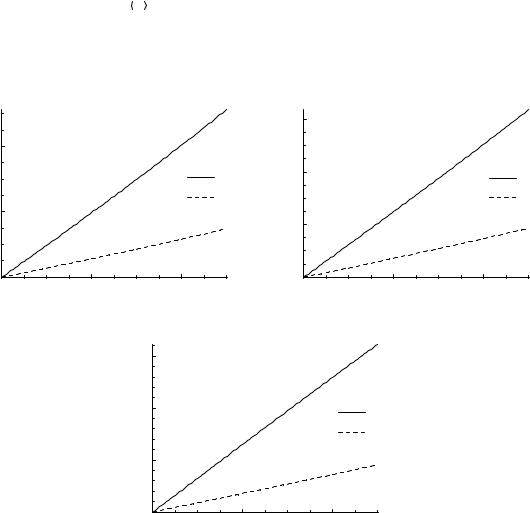

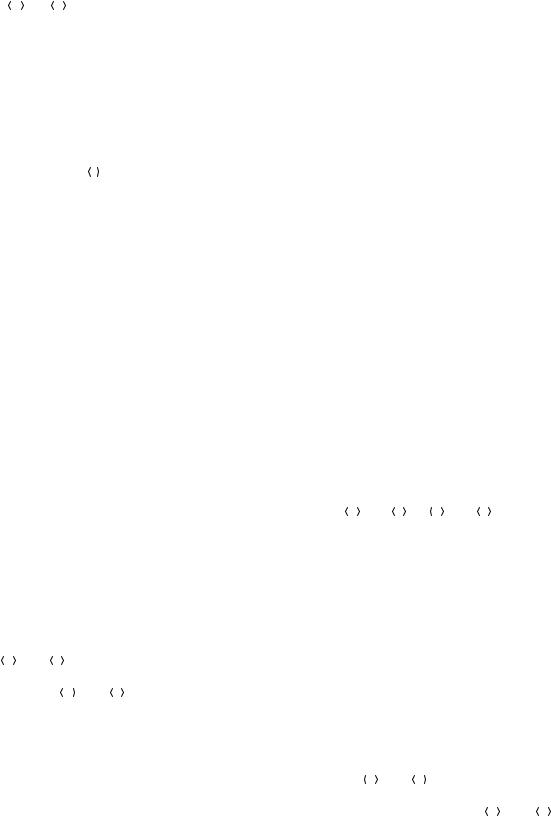

Рис. 22. Вольт-амперные характеристики двухузлового переключателя: |

|

||||||||||

a – InP, b – GaAs, c – GaSb; 1 – J 3 , 2 – J 2 . |

|

|

|

|

|

|

|||||

|

|

Таблица 14. Относительные токи через двухузловой переключатель |

|||||||||

в диапазоне U = 0–50 мВ

величина |

определение |

InP |

GaAs |

GaSb |

|

|

|

|

|

эффективность |

J 3 / (J 3 + J 2 ) |

> 0.774 |

> 0.773 |

> 0.779 |

|

|

|

|

|

невязка |

2 | (J 0 + J 3 + J 2 ) / (J 0 − J 3 − J 2 ) | |

< 8.42 10−6 |

< 4.37 10−6 |

< 6.21 10−6 |

92

Таблица 15. Проводимость двухузлового переключателя

при малых напряжениях смещения

п/п |

|

InP |

|

|

GaAs |

|

|

GaSb |

|

|

|

|

|

|

|

|

|

|

|

|

50.2 |

9.83 |

2.83 |

55.2 |

12.4 |

3.60 |

38.8 |

32.7 |

8.91 |

σ[0,3,2] , мкСм |

|

12.5 |

|

|

15.9 |

|

|

21.4 |

|

9.83 |

40.4 |

12.4 |

42.9 |

32.7 |

26.4 |

||||

|

|

40.4 |

|

|

42.9 |

|

|

26.4 |

|

|

2.83 |

19.5 |

3.60 |

24.8 |

8.91 |

45.2 |

Как видно из таблицы 15, элементы σ[0,3,2]03 и σ[0,3,2]02 растут с уменьшением эффективной массы электронов, что согласуется с ВАХ (рис. 22). Приведённые в ней проводимости полностью описывают квантовый электронный транспорт через переключатель (рис. 21) с оптимальными параметрами (табл. 13) при малых напряжениях смещения.

Резюме

В данном разделе была обоснована модель двухузлового переключателя на базе QIYсети. Его характерной особенностью является локализация управляющего электрического поля в области перед ветвлением. Для полупроводников с малой эффективной массой электрона (InP, GaAs, GaSb) устройство показало высокую эффективность при реалистичных значениях геометрических параметров и напряжённостей электрического поля. Его вольт-амперные характеристики оказались близкими к линейным, что делает приемлемым для его проводимости приближение малых напряжений смещения. Таким образом, было установлено, что вещественная матрица размером 3×3 с хорошей точностью полностью описывает квантовый электронный транспорт в двухузловом переключателе.

3.5.Логический элемент XOR

вдвумерной полупроводниковой структуре

Рассмотренный в разделе 3.4 двухузловой переключатель является простейшим устройством, управляющим токами за счёт эффектов квантовой интерференции. Для реализации на его основе логического элемента потребуется каскад из таких устройств [55, 56]. Это увеличит конечные размеры элемента и усложнит его конструкцию. Предпочтительны устройства, в которых логическая операция выполняется напрямую за счёт квантовой интерференции [57, 59]. При этом во всех случаях актуальны обратимые логические элементы в связи с их пониженным энергопотреблением [56].

В проекте двухузлового переключателя оптимизировалось положение уровня Ферми, напряжённость электрического поля, а также длины узла и рукава. Динамическое варьи-

93

рование геометрии прибора затруднено в реальном эксперименте. Поэтому предпочтительны устройства с фиксированными размерами всех элементов, функциональность которых достигается только за счёт электрических полей и положения уровня Ферми.

3.5.1. Проект устройства

Структура и эффективность

Логический элемент XOR осуществляет бинарную логическую операцию исключающего ИЛИ (сложение по модулю два), которая является обратимой (табл. 16).

Таблица 16. Таблица истинности логической операции XOR

бит 1 |

0 |

0 |

1 |

1 |

бит 2 |

0 |

1 |

0 |

1 |

XOR |

0 |

1 |

1 |

0 |

|

|

|

|

|

Согласно таблице 16, он может находиться в четырёх состояниях: "00", "01", "10", "11". Каждому из них соответствует значение выходного бита. В терминах электронного транспорта в низкоразмерных полупроводниковых структурах оно кодируется протекающим через устройство током: J 00 , J 01 , J 10 , J 11 . Принцип его работы запишем в виде:

J 00 |

= J 11 |

(265) |

J 00 |

≠ J 01 |

(266) |

J 10 |

= J 01 |

(267) |

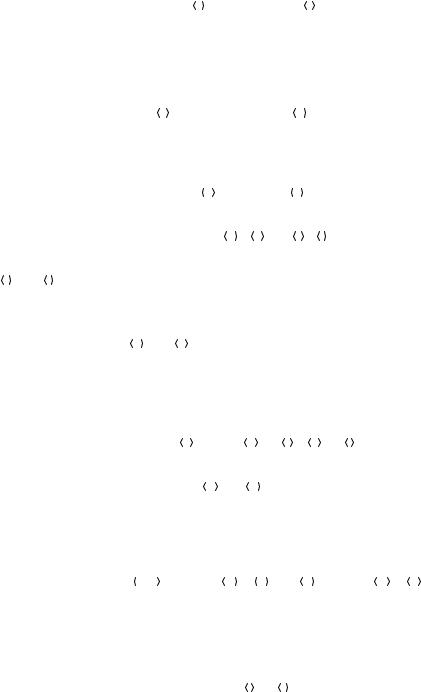

Состояние устройства формируют напряжения на его элементах, кодирующих входные биты. Также на токи влияют рассеивающие свойства прочих элементов и симметрия устройства. Для выполнения соотношений (265)–(267) удобно использовать логический элемент XOR, имеющий гексагональную структуру (рис. 23). Тогда в терминах структуры

QIY-сети (237) имеем

Q ={{1},{2},{4},{5}} |

|

I ={{6,13},{7,14},{8,15},{9,16},{10,17},{11,12}} |

(268) |

Y ={{0,12,6},{1,13,7},{2,14,8},{3,15,9},{4,16,10},{5,17,11}} |

|

Для достижения малых размеров устройства зафиксируем геометрию сети, задав её внутренним рукавам нулевую длину

{ak = 0}k I |

(269) |

94

и единичную безразмерную длину её I-узлам в конкретизации (238)

{a[K] =1}K I |

(270) |

В этом случае рассеянием электронов в сети будут управлять только напряжённости элек-

трического поля в I-узлах {E[K]}K I (рис. 24).

1

1

13 |

7 |

|

0 |

6 |

|

12 |

14 |

2 |

8 |

|

15

9 3

|

11 |

10 |

16 |

5 |

17 |

|

4 |

|

|

Рис. 23. Структура логического элемента XOR с 6-ю управляющими узлами: чёрные – кодирующие, заштрихованные – настроечные.

1 2 3

|

E U |

E L |

E R |

Source |

Drain |

E L |

E R |

|

E D |

Рис. 24. Конструкция логического элемента XOR: 1 – металл, 2 – диэлектрик, 3 – полупроводник.

95

В конструкции логического элемента XOR указаны напряжённости электрического поля с четырьмя различными значениями. Поясним их в терминах их безразмерных ана-

логов (241):

{ε |

:= 2m B3e |

−2E |

|

} =L,R ,U,D |

(271) |

|

|

e |

0 |

|

|

||

Функциональность устройства обеспечивают напряжённости электрического поля в настроечных узлах

ε L := ε[6,13] = ε[11,12], ε R := ε[8,15] = ε[9,16] |

(272) |

Состояние устройства задают напряжённости электрического поля в кодирующих узлах:

ε U := ε[7,14], ε D := ε[10,17] |

(273) |

ε U ,ε D {ε 0 ,ε1 } |

(274) |

где ε 0 и ε1 – безразмерные напряжённости электрического поля, которые интерпрети-

руются как значения входных битов «0» и «1» соответственно.

Значения величин ε U и ε D (274) определяют четыре возможных состояния логиче-

ского элемента XOR: «00», «01», «10», «11». Отвечающие им значения выходного бита определяется соответствующими токами в рукаве 3 (рис. 23):

{J kl := J 3 | ε U = ε k , ε D = ε l }k ,l=0,1 |

(275) |

Для выполнения (266) положим J 00 > J 01 (см. подраздел 3.5.2). Тогда с учётом требований (265) и (267) запишем эффективность логического элемента XOR как относительное преобладание токов в симметричных режимах над токами в несимметричных режимах:

δ XOR =[min(J 00 , J 11 ) − J 01 ] / max(J 00 , J 11 ) |

(276) |

Функциональность устройства достигается следующим образом. За счёт его симметрии (рис. 24) выполняется равенство (267). Неравенство (266) обеспечит соглашение

ε1 < ε 0 = 0 |

(277) |

Максимизация эффективности (276) как функции параметров устройства приведёт к приближённому выполнению равенства (265).

Параметры

Как и при моделировании двухузлового переключателя (подраздел 3.4.1), значения и диапазоны безразмерных параметров логического элемента XOR получим на основе их

96

размерных аналогов. Для данного устройства принятые выше геометрические характери-

стики QIY-сети (239) дополним на основе соглашений (269) и (270): |

|

{Ak = 0 нм}k I, {A[K] =10 нм}K I |

(278) |

Для оптимизации уровня Ферми логического элемента XOR установим обоснованный выше диапазон: EFXOR (E=1, E=3 ) (табл. 10). Уровни Ферми в резервуарах (внешних рука-

вах) определяются на основе напряжения смещения U :=U 03 (223) согласно выражениям

EF0 = EFXOR +eU / 2, EF3 = EFXOR −eU / 2 |

(279) |

Напряжение смещения с учётом [41, 43] зафиксируем на уровне U = 50 мВ. Положим также T = = 300 K . Для напряжённостей электрического поля выберем максимальное зна-

чение с учётом установленного в подразделе 3.2.1: {E = −7 107 –0 В/м} =1,L,R . На основе значений и диапазонов размерных параметров с учётом (263) и таблицы 8 для процедуры оптимизации получим таблицу 17.

Таблица 17. Значения и диапазоны безразмерных параметров

логического элемента XOR

п/п |

me / m0 |

μ= |

υ |

ε 0 |

ε1 |

ε L |

ε R |

ε XOR |

|

|

|

|

|

|

|

|

F |

InP |

0.080 |

5.43 |

10.50 |

0 |

[–147, 0] |

[–147, 0] |

[–147, 0] |

[π2 ,(3π)2 ] |

|

|

|

|

|

|

|

|

|

GaAs |

0.063 |

4.27 |

8.27 |

0 |

[–116, 0] |

[–116, 0] |

[–116, 0] |

[π2 ,(3π)2 ] |

|

|

|

|

|

|

|

|

|

GaSb |

0.041 |

2.78 |

5.38 |

0 |

[–75, 0] |

[–75, 0] |

[–75, 0] |

[π2 ,(3π)2 ] |

|

|

|

|

|

|

|

|

|

3.5.2. Оптимизация параметров

Оптимизация

Эффективность логического элемента XOR (276) определяется отношением протекающих через него электрических токов в трёх режимах: «00», «01», «11». Для их вычисления применим предложенную в главе 2 схему расчёта квантового электронного транспорта в низкоразмерных полупроводниковых структурах. В данном случае она запишется следующим образом.

|

97 |

|

1. |

Расчёт S-матриц Q-узла (рис. 16a) и Y-узла (рис. 16c) при r Q = r Y =1/ 2 и |

|

|

b Q = b Y =1 методом ND-map согласно (127) и (129). Расчёт S-матрицы I-узла |

|

|

(рис. 16b) при a I = b I =1, ε I = ε 0 согласно (121) и (257). |

|

2. |

Расчёт трёх S-матриц I-узла (рис. 16b) при a I = b I =1 и текущих трёх значениях ε I : |

|

|

ε I = ε1 , ε I = ε L , ε I = ε R согласно (121) и (257). |

|

3. |

Расчёт трёх S-матриц логического элемента XOR (рис. 23, рис. 24) согласно (167), |

|

|

(160) и (236) при {ak = 0,bk =1}k I , текущих ε1 , ε L и ε R |

в трёх режимах: «00» – |

|

ε U = ε 0 , ε D = ε 0 ; «01» – ε U = ε 0 , ε D = ε1 ; «11» – ε U |

= ε1 , ε D = ε1 . |

4.Расчёт безразмерных электрических токов на основе S-матриц логического элемента

XOR в режимах «00», «01», «11» согласно (224) и (198) при фиксированных μ= , υ (табл. 17) и текущем значении εFXOR .

Найдём максимум эффективности логического элемента XOR δ XOR (276) как функ-

ции его варьируемых параметров ε1 , ε L , ε R , εFXOR . Для этого оптимизируем их в за-

данных диапазонах (табл. 17) с помощью генетического алгоритма (приложение G). В представленной выше схеме на основе него организуется цикл обработки п. 2–4 до дости-

жения максимума функции δ XOR , при этом п. 1 осуществляется однократно. Такая организация расчётов обеспечивает высокую скорость оптимизации. Её результаты запишем в терминах размерных параметров устройства (табл. 18).

Таблица 18. Оптимальные параметры и эффективность

логического элемента XOR (T = = 300 K)

п/п |

me / m0 |

E 1 , В/м |

E L , В/м |

E R , В/м |

E XOR , эВ |

δ XOR |

|

|

|

|

|

F |

|

InP |

0.080 |

−2.63 107 |

−1.17 105 |

−1.02 107 |

0.097 |

0.813 |

GaAs |

0.063 |

−3.32 107 |

−1.80 107 |

−3.14 107 |

0.147 |

0.840 |

GaSb |

0.041 |

−5.01 107 |

−4.27 107 |

−6.07 107 |

0.232 |

0.945 |

В рассчитанной модели устройства эффективность в виде (276) обеспечивала выпол-

нение неравенства (266) для J 00 > J 01 . Также проводилась оптимизация параметров при

J 00 < J 01 с δ XOR =[J 01 −max(J 00 , J 11 )] / J 01 . Расчёты показали, что в этом случае эф-

фективность устройства существенно (>10%) уступает рассмотренному выше варианту

98 (результаты не приводятся). Поэтому предпочтение было отдано оптимизации на основе

(276) для J 00 > J 01 .

Интерпретация

Как видно из таблицы 18, эффективность логического элемента XOR растёт с уменьшением эффективной массы электрона. Здесь это является спецификой выбранного диапазона напряжённостей электрического поля и геометрии устройства. Например, при рас-

ширении диапазона {E = −108 –0 В/м} =1,L,R после оптимизации устройство из InP по эф-

фективности будет превосходить устройство из GaAs. Расчёты показали, что при уменьшении диапазона значений напряжённостей электрического поля на порядок функциональность устройства сохраняется. Это будет приемлемым, если полагать допустимой эффективность устройства на уровне 20%. Также в таблице 18 заметна тенденция, обнаруженная в случае двухузлового переключателя: приближение оптимального уровня Ферми к энергии второго канала (табл. 10) с уменьшением эффективной массы электронов.

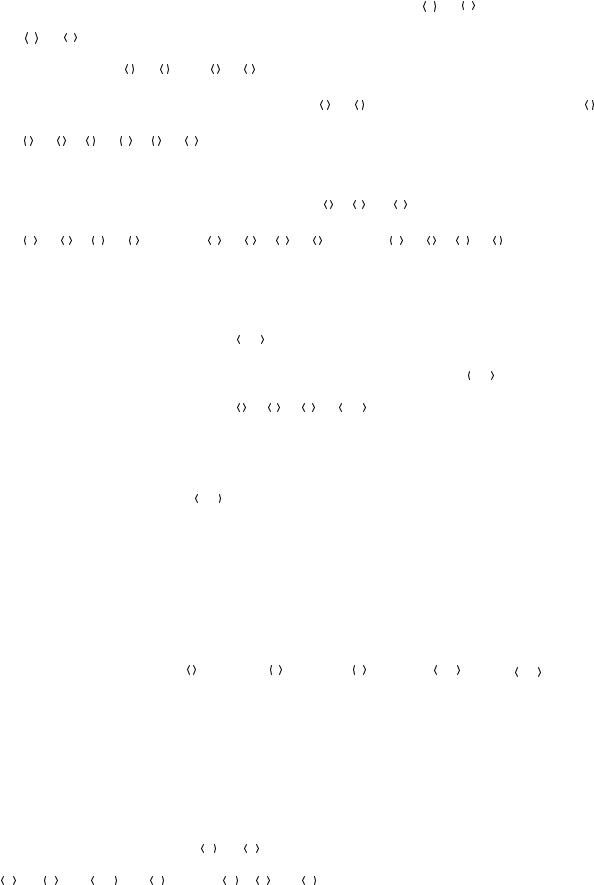

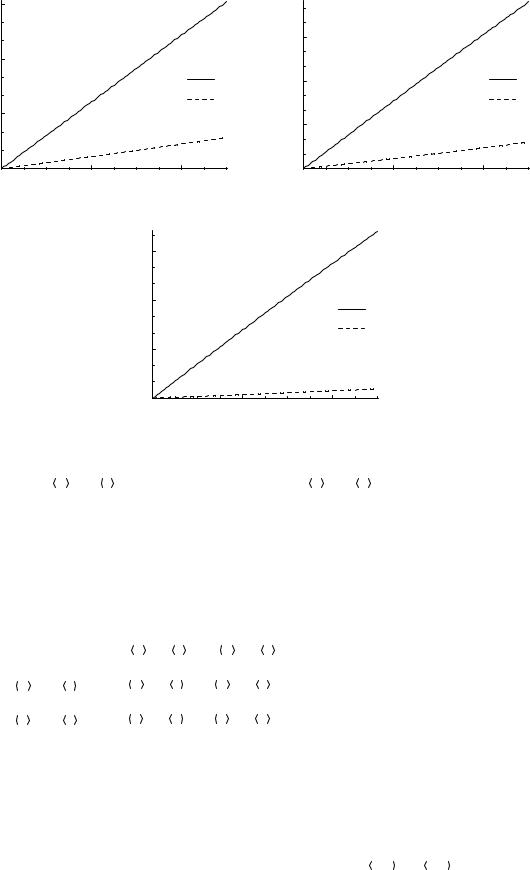

Построим вольт-амперные характеристики логического элемента XOR с параметрами из таблицы 18 (рис. 25). Как и в случае двухузлового переключателя, ВАХ близки к линейным. Также очевидно отсутствие прямой зависимости величины токов в режимах "00" и "11" от эффективной массы электронов. Величина токов в режимах "01" и "10" меняется пропорционально эффективности устройства. Характерной особенностью ВАХ логиче-

ского элемента XOR является попарное слияние графиков J 00 и J 11 , J 01 и J 10 . Дополним ВАХ логического элемента XOR таблицей относительных токов (табл. 19).

Определение эффективности в таблице 19 эквивалентно определению (276) с учётом оптимизации параметров устройства. В рассмотренном диапазоне напряжений она является строго убывающей функцией и её значения всюду превосходят значение при U = 50 мВ.

Разброс J 00 и J 11 для всех трёх материалов составляет менее 0.4%. Это позволяет изо-

бразить на ВАХ J 00 и J 11 одним графиком, так как они визуально сливаются. Данный эффект является «побочным» следствием максимизации эффективности (276) и обеспечивает приближённое выполнение равенства (265). Как и ожидалось, в силу симметрии уст-

ройства приближённо выполняется равенство (267). Разброс J 01 и J 10 для всех трёх ма-

териалов составляет менее 0.002%, что также позволяет изобразить на ВАХ J 01 и J 10 одним графиком. Его отличие от нуля связано с погрешностью расчёта токов через устройство. Её оценка снизу (невязка) всюду составляет менее 0.0004%, что является приемлемым значением.

|

|

|

|

99 |

|

|

|

0,9 |

a |

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

0,9 |

|

|

|

0,6 |

|

|

|

|

|

|

|

μA |

|

|

1 |

μA0,6 |

|

|

1 |

J, |

|

|

2 |

J, |

|

|

2 |

0,3 |

|

|

|

|

|

||

|

|

|

0,3 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

20 |

|

40 |

0 |

|

20 |

40 |

|

U||, mV |

c |

|

U||, mV |

|

||

|

|

|

|

|

|

|

|

|

|

|

0,9 |

|

|

|

|

|

μA |

0,6 |

|

|

1 |

|

|

|

|

|

|

|

|||

|

J, |

|

|

|

2 |

|

|

|

|

|

0,3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

20 |

40 |

|

|

|

|

|

|

U||, mV |

|

|

|

Рис. 25. Вольт-амперные характеристики логического элемента XOR: a – InP, b – GaAs, |

|||||||

c – GaSb; 1 – J 00 |

и J 11 |

(графики сливаются), 2 – J 01 |

и J 10 |

(графики сливаются). |

|||

Таблица 19. Относительные токи через логический элемент XOR |

|||||||

в диапазоне U = 0–50 мВ

величина |

|

|

определение |

|

InP |

GaAs |

GaSb |

|

|

|

|

|

|

|

|

||

эффективность |

1−(J 01 |

+ J 10 ) / (J 00 |

+ J 11 ) |

> 0.813 |

> 0.840 |

> 0.944 |

||

|

|

|

|

|

|

|

|

|

разброс J 00 |

и J 11 |

2 | J 00 |

− J 11 |

| /(J 00 |

+ J 11 ) |

< 0.00321 |

< 0.00341 |

< 0.00198 |

разброс J 01 |

и J 10 |

2 | J 01 |

− J 10 |

| /(J 01 |

+ J 10 ) |

<1.89 10−6 |

<1.68 10−6 |

<1.77 10−5 |

невязка |

|

2 | (J 0 + J 3 ) / (J 0 − J 3 ) | |

< 8.03 10−7 |

<1.45 10−6 |

< 3.48 10−6 |

|||

Поскольку ВАХ логического элемента XOR близки к линейным (рис. 25), его проводимость (221) на данном участке слабо зависит от уровней Ферми резервуаров. Применим для неё приближение малых напряжений смещения (227): σ XOR ≈σ XOR . С учётом найденных оптимальных параметров устройства (табл. 18) запишем его таблицу истинности в терминах приближённой проводимости (табл. 20).

100

Таблица 20. Таблица истинности логического элемента XOR

при малых напряжениях смещения

п/п |

|

E U , В/м |

E D , В/м |

|

σ XOR 30 , См |

|||||||||

|

0 |

|

|

|

|

0 |

|

|

1.83 10−5 |

|||||

InP |

0 |

|

|

|

|

−2.63 107 |

|

|

3.30 10−6 |

|

||||

|

−2.63 107 |

0 |

|

|

3.30 10−6 |

|||||||||

|

|

|

|

|||||||||||

|

|

−2.63 107 |

|

−2.63 107 |

|

|

1.84 10−5 |

|||||||

|

0 |

|

|

|

|

0 |

|

|

2.34 10−5 |

|||||

GaAs |

0 |

|

|

|

|

−3.32 107 |

|

|

3.44 10−6 |

|

||||

|

−3.32 107 |

|

0 |

|

|

3.44 10−6 |

|

|||||||

|

|

|

|

|

|

|||||||||

|

|

−3.32 107 |

−3.32 107 |

|

2.34 10−5 |

|||||||||

|

0 |

|

|

|

|

0 |

|

|

2.11 10−5 |

|||||

GaSb |

0 |

|

|

|

|

−5.01 107 |

|

|

1.02 10−6 |

|

||||

|

− |

|

10 |

7 |

|

0 |

|

|

1.02 |

|

10 |

−6 |

|

|

|

|

5.01 |

|

|

|

|

|

|

|

|

|

|||

|

|

−5.01 107 |

|

−5.01 107 |

|

|

2.11 10−5 |

|||||||

Таблица истинности логического элемента XOR (табл. 20) демонстрирует принцип его работы. Значения входных битов определяются напряжённостями электрического поля в

кодирующих узлах E U и E D (рис. 24). Напряжённость, равная E 0 , соответствует логи-

ческому «0», напряжённость, равная E 1 – логической «1». С учётом (277) и (241)

E 0 = 0 В/м, а E 1 для каждого полупроводника указана в таблице 18. Значение выходного бита определяется проводимостью устройства при заданных E U и E D . Сопоставив таб-

лицы истинности логического элемента (табл. 20) и логической операции XOR (табл. 16),

можно видеть, что для всех материалов проводимость 10−5 См соответствует логиче-

скому «0», а проводимость 10−6 См – логической «1». Ячейки, отвечающие логической

«1», всюду для наглядности затенены.

С точки зрения эксперимента, проведённая в этом подразделе оптимизация напряжённостей электрического поля логического элемента XOR носит оценочный характер. Это означает, что расчёты указывают только их порядок, при котором достигается функциональность устройства. Уточнение рабочих значений напряжённостей возможно с дальнейшим совершенствованием модели. Однако их точный расчёт затруднён из-за проблемы применимости приближений, которые неизбежно будут использоваться. Расчёт же из пер-