- •Мікропроцесорні системи зміст

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •5.3. Dsp сімейства tms320с1х

- •1. Однокристальні універсальні мікропроцесори

- •Класифікація мікропроцесорів (мп)

- •Восьмирозрядний мікропроцесор i8080

- •Восьмирозрядні мікропроцесори 8085 і z80

- •Шістнадцятирозрядний мікропроцесор 8086

- •Арифметичний співпроцесор 8087

- •Мікропроцесор Intel 8088

- •16-Розрядний мікропроцесор 80286

- •Мікропроцесор 80386

- •Арифметичні співпроцесори 80287 і 80387

- •Мікропроцесор 486 dx

- •Мікропроцесор Pentium

- •1.12 Мікропроцесор Pentium Pro, Pentium II

- •1.13. Мікропроцесор amd-k6

- •Оцінка продуктивності мп

- •2. Схеми підтримки. Контролери

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

- •2.5. Програмований контролер переривання 8259а

- •2.6. Контролер прямого доступу до пам’яті 8237а

- •2.7. Інтервальний таймера 8254.

- •Сi – вхід лічильника;

- •2.8. Система реального часу

- •3. Процесори зі скороченою кількістю команд (risc-процесори)

- •3.1. Особливості risc-процесорів

- •3.2. Risc-процесор Alpha 21164 компанії dec

- •3.3. Risc-процесор PowerPc620

- •3.4. Risc-процесор mips-10000

- •3.5. Risc-процесор ра-8000

- •3.6. Risc-процесор UltraSparc іі

- •3.7. Risc-процесори UltraSparc ііі, UltraSparc іv

- •4.Системні ресурси та системні шини. Чипсети

- •4.1. Системні шини

- •4.2. Розподіл і організація пам'яті пк

- •4.3. Кеш пам’ять

- •4.4. Чипсети

- •Характеристика чипсетів

- •4.4.2. Чипсети серії 440

- •5. Цифрові сигнальні процесори (dsp)

- •5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

- •5.2. Особливості роботи сигнальних процесорів

- •5.3. Dsp сімейства tms320с1х

- •5.4. Сигнальні процесори сімейства tms320с2х

- •5.5. Процесори dsp сімейства tms320c5x

- •5.6. Сигнальні процесори tms320c2xx і 320с54х

- •5.7. Сигнальний процесор tms320с30

- •5.8. Сигнальні процесори сімейства tms320с4х

- •5.9. Сигнальні процесори сімейства tms320c8x

- •5.10. Процесор сімейства tms320c62xх

- •5.11. Dsp процесори сімейства tms320c67х

- •5.12. Сигнальні процесори dsp сімейства adsp21xx

- •5.13. Сигнальні процесори dsp сімейства аdsp 21ххх

- •6. Мультипроцесорні обчислювальні системи

- •6.1. Класифікація обчислюваних систем

- •6.2. Характеристика СуперЕом серії Cray

- •6.3. Системи з масовим паралелізмом

- •Закон Амдала

- •6.5. Закон Густафсона

- •6.6. Грід – система

- •6.6.1. Ресурси Грід

- •6.6.2. Архітектура Грід-систем

- •Протоколи глобального Гріда

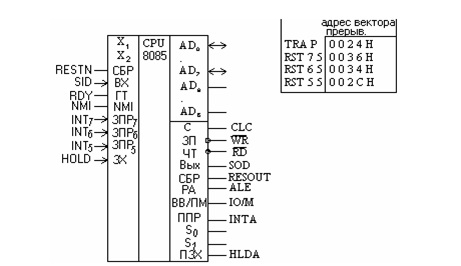

Восьмирозрядні мікропроцесори 8085 і z80

Восьмирозрядний МП 8085 (рис. 1.5.) представляє собою поліпшений варіант МП ВМ80. Він виконаний за допомогою КМОП-технології, завдяки чому має менше споживання, більшу швидкодію і використовує тільки одне джерело живлення +5 В.

Усередині кристала розташований генератор, який тактує імпульси, що працює на частоті 3 МГц. Особливість даного МП полягає в тому, що в ньому молодші вісім розрядів об'єднані з шиною даних, у зв'язку з чим з'явилася можливість збільшити число виходів, які використовуються для керуючих сигналів.

Рис 1.5. Схема УГЗ МП 8085

Сигнали ініціалізації пристроїв:

- вхідний і вихідний сигнали скидання (RESIN, RESOUT).

Cинхронізації:

- вхідні виводи х1, х2 (використовують для підключення кварцового резонатора);

- вихідний сигнал С.

Управління шин:

- захоплення HOLD;

- підтвердження захоплення HOLDA.

Преривання (у цьому МП кількість входів преривання збільшено до 5):

- вхід немаскуючого преривання - NMI (найвищий пріоритет, використовується при пошкодженні живлення);

- три входи векторних преривань INT7.5, INT6.5, INT5.5;

- вихід підтвердження преривання - INTA.

Особливість МП і в тому, що в ньому є входи і виходи, що дозволяють приймати інформацію і видавати її в послідовному коді: SID і SOD.

Загальні сигнали управління

- IO / M вв / пм - вивід / пам'ять;

- RDY ГТ - готовність;

- RD ЧТ - читання;

- WR ЗП - запис;

- ALE РА - дозвіл адреси. Дозволяє ідентифікувати інформацію за адресою.

- S1, S0 - сигнали стану (S1 = 0, S0 = 0 - МП в стані зупинки).

Даний МП реалізує ті ж команди, що і ВМ80 і використовує дві додаткові:

- SIM - встановити маску переривань;

- RIM - скинути маску переривань.

Використовуючи такий МП, можна істотно зменшити число кристалів при побудові МПС.

Восьмирозрядний мікропроцесор Z80 (рис. 1.6.)

Рис. 1.6. Схема УГЗ МП Z80

Даний МП (рис. 1.6.) представляє собою також покращений варіант ВМ80, використовує одне джерело живлення +5 В, містить внутрішній генератор і не вимагає додаткового системного контролера.

У ньому істотно розширено набір команд за рахунок збільшення РЗП (регістрів загального призначення) (рис. 1.7.) та включення нових команд. Число команд з урахуванням модифікації близько 560. Програмістська модель містить в 2 рази більше регістрів: ті ж регістри, що і ВМ80, але і також регістри зі штрихом.

Рис. 1.7. Схема РЗП

З'явилося два індексних шістнадцятирозрядних регістра Ix і Iy і два восьмирозрядних регістра: I - повернення переривання; R - оновлення.

Вивід RFM - регенерація пам'яті.

Шістнадцятирозрядний мікропроцесор 8086

МП 8086 виготовляється за допомогою вдосконаленої n-МОН технології, тому вимагає одного джерела живлення +5 В, розташовується в корпусі з 40 виводами.

На кристалі 5,5 х5, 5 мм цього МП розташовується 29 тис. активних елементів. Тактова частота - 5, 8, 10 МГц. Середня швидкість виконання операції - 0,33 млн. операцій з фіксованою комою в секунду (MIPS).

Даний МП має більш розвинену систему команд, що містить 133 базових команди замість 78 восьмирозрядного МП8080. Використовує всі відомі способи адресації, обробляє 16-і і 8-розрядні операнди.

Операція ділення і множення в даному МП реалізується апаратно. Якщо використовувати разом МП 8086 і арифметичний співпроцесор 8087 можлива реалізація операцій з плаваючою точкою.

Особливість даного МП - організація конвеєрної реалізації команд. У цьому МП 16-розрядна ШД об'єднана з 16 молодшими розрядами адреси, а загальне число адресних шин доведено до 20, завдяки чому адресується розмір оперативної пам'яті збільшений до 1 Мб.

Даний МП може бути використаний для побудови простих і складних МПС. У простих системах керуючі сигнали виробляє сам МП. У складних - частина виробляє сам МП, частина - інші схеми. Для переводу МП з режиму мінімальної конфігурації в режим максимальної є спеціальний вхід min / max (рис. 1.8.).

Рис. 1.8. Схема УГЗ МП 8086

Де:

TEST - перевірка (тестування)

min/max мін/макс. конфігурації.

NMI – немаскуюче переривання.

RST - системне скидання

RDY – готовність

INT - запит преривання

DEN - строб даних

BHE - передача старшого байта

ALE - дозвіл адреси

DT/R - прийом/передача

Структурна схема МП 8086 приведена на рис. 1.9.

Рис. 1.9. Структурна схема МП 8086

До складу МП включені наступні блоки: операційний пристрій, пристрій управління; пристрій сполучення з шиною.

Операційний пристрій містить:

АЛУ (16 розрядів);

регістр ознак F (прапорів) - 16 розрядів, в яких молодші 8 розрядів повністю відповідають 8-розрядному регістру F МП 8080;

регістри загального призначення, що містять регістр А (16 розрядів), регістр С (16 розрядів), регістр D (16 розрядів), регістр В (16 розрядів), регістр покажчика вершини стека SP (16 розрядів), регістр бази BP (16 розрядів) , 2 індексних регістра (16 розрядів): SI - джерела, DI – приймача;

Пристрій сполучення з шиною:

буфер адреси даних (16 розрядів), який пов'язує вхідні системну шину з внутрішньої 16-розрядної шиною.

буфер / адреси керування (4 розряду).

Пристрій керування включає блок управління МП, блок керування шиною, блок керування прямим доступом до пам'яті.

До складу ПК входить черга команд, яка складається з 6 восьмирозрядних регістрів, інформація з яких витягується побайтно. Як тільки з черги команд витягли 2 байта, відразу ж з ОП завантажується чергові 2 байта.

СМА суматор адреси, який містить блок сегментних регістрів: CS - сегмент команд; DS - сегмент даних; SS - сегмент стека; ES - сегмент додаткових даних; 16-розрядний покажчик команди IP, який на відміну від лічильника команд МП 8080 зберігає зсув команди. Адреса наступної команди є сумою двох складових, вмісту сегментного регістра CS і адресного регістру IP, тобто (IP) + (CS). І тільки в тому випадку, коли вміст сегментного регістра дорівнює нулю лічильник команд 8080 МП і регістр покажчика команд 8086 МП є аналогами.

Програмна сумісність 8 і 16 розрядних МП досягається за рахунок наступної аналогії між РЗП цих 2 моделей (таблиця 1.4).

Таблиця 1.4

|

8080 |

A |

B |

C |

D |

E |

H |

L |

SP |

PC |

F |

|

8086 |

AL |

CH |

CL |

DH |

DL |

BH |

BL |

SP |

IP |

FL |

Вся пам'ять, що адресується ємністю 1 МБ розбивається на 4 ділянки довжиною 256Кб (рис. 1.10.).

Рис. 1.10. Рис. 1.11.

Будь-які дві сусідні байти можна інтерпретувати як одне 16-бітове слово. Адресою слова вважається адреса його молодшого байта. Слова доцільно розміщувати по парних адресах, тоді за один цикл роботи шини можна вважати одне слово. Один сегмент пам'яті має довжину 64 КБ. Кожен сегмент має власну початкову адресу (покажчик сегмента), який розміщується в одному з сегментних регістрів. Початкові адреси сегментів повинні бути кратні 16. Окремі сегменти можуть бути такими, що не перекриваються/перекриваються, сусідніми. Інформація, яка необхідна для визначення 20 бітної фізичної адреси отримується шляхом підсумовування покажчика сегмента і відносної адреси (рис. 1.11.).