- •Мікропроцесорні системи зміст

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •5.3. Dsp сімейства tms320с1х

- •1. Однокристальні універсальні мікропроцесори

- •Класифікація мікропроцесорів (мп)

- •Восьмирозрядний мікропроцесор i8080

- •Восьмирозрядні мікропроцесори 8085 і z80

- •Шістнадцятирозрядний мікропроцесор 8086

- •Арифметичний співпроцесор 8087

- •Мікропроцесор Intel 8088

- •16-Розрядний мікропроцесор 80286

- •Мікропроцесор 80386

- •Арифметичні співпроцесори 80287 і 80387

- •Мікропроцесор 486 dx

- •Мікропроцесор Pentium

- •1.12 Мікропроцесор Pentium Pro, Pentium II

- •1.13. Мікропроцесор amd-k6

- •Оцінка продуктивності мп

- •2. Схеми підтримки. Контролери

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

- •2.5. Програмований контролер переривання 8259а

- •2.6. Контролер прямого доступу до пам’яті 8237а

- •2.7. Інтервальний таймера 8254.

- •Сi – вхід лічильника;

- •2.8. Система реального часу

- •3. Процесори зі скороченою кількістю команд (risc-процесори)

- •3.1. Особливості risc-процесорів

- •3.2. Risc-процесор Alpha 21164 компанії dec

- •3.3. Risc-процесор PowerPc620

- •3.4. Risc-процесор mips-10000

- •3.5. Risc-процесор ра-8000

- •3.6. Risc-процесор UltraSparc іі

- •3.7. Risc-процесори UltraSparc ііі, UltraSparc іv

- •4.Системні ресурси та системні шини. Чипсети

- •4.1. Системні шини

- •4.2. Розподіл і організація пам'яті пк

- •4.3. Кеш пам’ять

- •4.4. Чипсети

- •Характеристика чипсетів

- •4.4.2. Чипсети серії 440

- •5. Цифрові сигнальні процесори (dsp)

- •5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

- •5.2. Особливості роботи сигнальних процесорів

- •5.3. Dsp сімейства tms320с1х

- •5.4. Сигнальні процесори сімейства tms320с2х

- •5.5. Процесори dsp сімейства tms320c5x

- •5.6. Сигнальні процесори tms320c2xx і 320с54х

- •5.7. Сигнальний процесор tms320с30

- •5.8. Сигнальні процесори сімейства tms320с4х

- •5.9. Сигнальні процесори сімейства tms320c8x

- •5.10. Процесор сімейства tms320c62xх

- •5.11. Dsp процесори сімейства tms320c67х

- •5.12. Сигнальні процесори dsp сімейства adsp21xx

- •5.13. Сигнальні процесори dsp сімейства аdsp 21ххх

- •6. Мультипроцесорні обчислювальні системи

- •6.1. Класифікація обчислюваних систем

- •6.2. Характеристика СуперЕом серії Cray

- •6.3. Системи з масовим паралелізмом

- •Закон Амдала

- •6.5. Закон Густафсона

- •6.6. Грід – система

- •6.6.1. Ресурси Грід

- •6.6.2. Архітектура Грід-систем

- •Протоколи глобального Гріда

5.9. Сигнальні процесори сімейства tms320c8x

Процесором TMS320c8x є процесор принципово нової архітектури, оскільки він був випущений для обробки зображень 2D і 3D-графики, компресії і декомпресії аудіо-видеоданих. TMS320c8x має другу назву MVP (Multimedia Video Processor). На чипі даного процесора розташовано 4 млн. транзисторів, корпус має 305 виводів.

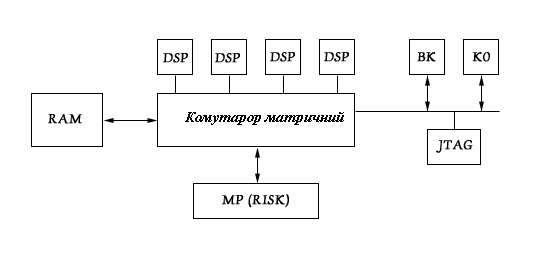

В інтегральній схемі TMS320c8x об'єднано 5 повнофункціональних процесорів: чотири підлеглих процесора DSP і п'ятий – головний процесор (MP), що є 32-розрядним RISC-процесором з вбудованим високопродуктивним процесором з плаваючою точкою (рис.5.10). Зв'язок головного процесора з чотирма робочими процесорами здійснюється через комутатор (рис.5.11). До складу сигнального процесора входить також внутрішньокристалічна пам'ять SRAM, ємкістю 44-50 кБ, доступ до якої також здійснюється через матричний комутатор.

Рис.5.10.Структурна схема процесора TMS320C8X.

Контролер обміну (КО) управляє операціями обміну всіх процесорів як усередині кристала (через комутатор), так і поза кристалом; за допомогою вхідних в його склад інтерфейсних схем підтримує всі види зовнішньої пам'яті (SRAM, ORA, VRAM). Контролер обміну підтримує як лінійну, так і координатну адресацію при роботі з 2D і 3D графічними зображеннями.

Рис.5.11. Структурна схема головного процесора сімейства TMS320C8X

Основними компонентами головного процесора MP є регістровий файл, конвеєрний процесор з ПЗ продуктивністю 100 MFLOPS, цілочисельний пристрій множення-складання, чотири акумулятори АКК1-АКК4, таблиця зайнятості регістрів, пристрій барабанного зрушення, внутрішньокристалічні КЕШ команд і даних по 4кБ. Кожен з чотирьох підлеглих DSP процесорів може виконувати за один такт одночасно операцію множення, зсуву або підсумовування і два звернення до пам'яті. Ці процесори працюють з 32-розрядними числами і 64-розрядними командами. До складу локальних процесорів входять помножувач, 32-розрядний АЛП, пристрій барабанного зсуву (ПБЗ), два блоки генерації адреси, 44 програмно доступних регістра (десять – адреси, вісім – даних, шість – індексних і двадцять додаткових).

5.10. Процесор сімейства tms320c62xх

Серія DSP процесорів TMS320c62xх складається з моделей TMS320c6202, 6203 і 6204, що є сигнальними процесорами з фіксованою комою, що використовують командні слова великої довжини VLIW (Very Long Instruction Word). Процесори даного сімейства використовують тактові частоти 200, 250 і 300 Мгц, відповідно чому їх продуктивність складає 1600 MIPS, 2000 і 2400 MIPS.

Процесори містять 8 функціональних пристроїв: шість АЛП 32/40-розрядних і два 16-розрядні помножувачі. Об'єм внутрішньокристальної пам'яті в процесорі 6202 складає 3 Мбіта (пам'ять програм - 256 КБ, пам'ять даних - 128 КБ), в процесорі 6203 - 7 Мбіт (відповідно 384 КБ і 512 КБ) і в процесорі 6204 - 1Мбіт (64 КБ і 64 КБ).

Структурна схема DSP даної сімейства приведена рис.5.12.

Рис.5.12. Структурна схема DSP TMS320C62XX

Де:

МПП - мультиканальный послідовний порт

ВRAM - зовнішня RAM

КДПП - контролер доступу до пам'яті програм

КДПД - контролер доступу до пам'яті даних

РГУ - регістр управління

РФ - регістровий файл

Кпр - контролер переривання

L, M, S, DA - функціональний модулі АЛУ( зрушення, множення, зворотна адресація)

Залежно від типу DSP корпус може містити 352 або 384 виводи, що включають виводи інтерфейсу із зовнішньою пам'яттю, виводи головного інтерфейсу, портів, виводи сигналів управління, переривання, тактування, тестування.

Процесор CPU може оперувати з 8, 16 і 32-розрядними даними. Для застосувань, що вимагають високої точності обчислень, передбачена робота з 40-розрядними операндами. Процес обробки VLIW починається з вибірки з пам'яті команд 256-розрядного пакету. Набір пристроїв вибірки - декодування - диспетчеризації команд може направляти до функціональних модулів до восьми 32-розрядних команд за один такт по кожному з двох шляхів обробки (А і В) через два регістрові файли РФА і РФВ, кожен з яких включає 16 32-розрядних регістра.