- •Мікропроцесорні системи зміст

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •5.3. Dsp сімейства tms320с1х

- •1. Однокристальні універсальні мікропроцесори

- •Класифікація мікропроцесорів (мп)

- •Восьмирозрядний мікропроцесор i8080

- •Восьмирозрядні мікропроцесори 8085 і z80

- •Шістнадцятирозрядний мікропроцесор 8086

- •Арифметичний співпроцесор 8087

- •Мікропроцесор Intel 8088

- •16-Розрядний мікропроцесор 80286

- •Мікропроцесор 80386

- •Арифметичні співпроцесори 80287 і 80387

- •Мікропроцесор 486 dx

- •Мікропроцесор Pentium

- •1.12 Мікропроцесор Pentium Pro, Pentium II

- •1.13. Мікропроцесор amd-k6

- •Оцінка продуктивності мп

- •2. Схеми підтримки. Контролери

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

- •2.5. Програмований контролер переривання 8259а

- •2.6. Контролер прямого доступу до пам’яті 8237а

- •2.7. Інтервальний таймера 8254.

- •Сi – вхід лічильника;

- •2.8. Система реального часу

- •3. Процесори зі скороченою кількістю команд (risc-процесори)

- •3.1. Особливості risc-процесорів

- •3.2. Risc-процесор Alpha 21164 компанії dec

- •3.3. Risc-процесор PowerPc620

- •3.4. Risc-процесор mips-10000

- •3.5. Risc-процесор ра-8000

- •3.6. Risc-процесор UltraSparc іі

- •3.7. Risc-процесори UltraSparc ііі, UltraSparc іv

- •4.Системні ресурси та системні шини. Чипсети

- •4.1. Системні шини

- •4.2. Розподіл і організація пам'яті пк

- •4.3. Кеш пам’ять

- •4.4. Чипсети

- •Характеристика чипсетів

- •4.4.2. Чипсети серії 440

- •5. Цифрові сигнальні процесори (dsp)

- •5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

- •5.2. Особливості роботи сигнальних процесорів

- •5.3. Dsp сімейства tms320с1х

- •5.4. Сигнальні процесори сімейства tms320с2х

- •5.5. Процесори dsp сімейства tms320c5x

- •5.6. Сигнальні процесори tms320c2xx і 320с54х

- •5.7. Сигнальний процесор tms320с30

- •5.8. Сигнальні процесори сімейства tms320с4х

- •5.9. Сигнальні процесори сімейства tms320c8x

- •5.10. Процесор сімейства tms320c62xх

- •5.11. Dsp процесори сімейства tms320c67х

- •5.12. Сигнальні процесори dsp сімейства adsp21xx

- •5.13. Сигнальні процесори dsp сімейства аdsp 21ххх

- •6. Мультипроцесорні обчислювальні системи

- •6.1. Класифікація обчислюваних систем

- •6.2. Характеристика СуперЕом серії Cray

- •6.3. Системи з масовим паралелізмом

- •Закон Амдала

- •6.5. Закон Густафсона

- •6.6. Грід – система

- •6.6.1. Ресурси Грід

- •6.6.2. Архітектура Грід-систем

- •Протоколи глобального Гріда

2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

Дана мікросхема програмованого послідовного інтерфейсу PSI використовується для обміну інформацією між МП і зовнішніми пристроями, що працюють в послідовному коді. Як правило, її використовують для зв'язку МП з віддаленими терміналами (через модем). Схема 8251 виконує більш складну роботу, ніж 8255. У ній здійснюється перетворення інформації з паралельної форми на послідовну, обрамлення перетвореної інформації шляхом додавання до неї службових даних: стартових, стопових посилок, контрольних бітів і спеціальних байтів синхронізації.

Така мікросхема може працювати в асинхронному режимі з максимальною швидкістю 9,6 Кбіт / с, а в синхронному режимі - 56 Кбіт / с. УГЗ схеми PSI показано на рис. 2.9.

Схема пов’язана з СШД за допомогою 8-ми інформаційних виходів D0-D7, на які надходить або з яких видається паралельний код. Вона має інформаційний вхід послідовного коду - вхід приймача RxD, вихід послідовного коду - XD

.

Рис. 2.9. УГЗ схеми PSI

де:

керуючі входи:

![]() -

вибір кристала;

-

вибір кристала;

![]() -

запис;

-

запис;

![]() -

читання;

-

читання;

CLC - синхронізація;

C/![]() - керування чи дані;

- керування чи дані;

SD - вид (вибір) синхронізації;

RST - скидання;

![]() –синхронізація

приймача;

–синхронізація

приймача;

![]() –синхронізація

передавача;

–синхронізація

передавача;

RxRD - готовність приймача;

TxRD - готовність передавача;

ТXE - кінець передачі.

Сигнали управління модемом:

![]() -

готовність

приймача

терміналу;

-

готовність

приймача

терміналу;

![]() –готовність

передавача

терміналу;

–готовність

передавача

терміналу;

![]() –запит

приймача

терміналу;

–запит

приймача

терміналу;

![]() –запит

передавача

терміналу.

–запит

передавача

терміналу.

Структурна схема PSI приведена на рис. 2.10.

Рис. 2.10. Структурна схема PSI

де:

БД - буфер даних (який пов'язує СШД МП з внутрішньою ШД) i містіть два регістри Рг1 і Рг2 (вхідній і вихідний).

ПД - блок передавача, де здійснюється перетворення паралельного коду в послідовний.

ПР - блок приймача, де здійснюється перетворення послідовного коду в паралельний.

БУ - блок управління включає регістр режиму РгР, реєстр наказу РгН, реєстр стану РгС, реєстр синхронізації байта Перша і іншого РгС1 и РгС2, схема управління СУ;

СУМ - схема управління, модемом.

Дана схема, як зазначалось вище, працює в асинхронному або синхронному режимі. Асинхронний режим - режим посимвольного вводу/виводу інформації. Символ може містити від 5 до 8 розрядів. До інформаційних розрядів кожного символу додається службова інформація: біт парності/непарності (ч/н), стартова () i степові посилки тривалістю 1, 1,5 і 2 .

При роботі в синхронному режимі (передача групи символів), кожної посилки містіть 1 або 2 синхронізуючих байта СБ, після чого йдуть інформаційні байти (БД - байт даних) (рис. 2.11.)

|

СБ1 |

СБ2 |

БД1 |

БД2 |

… |

… |

Рис. 2.11.

Програмування даного кристала здійснюється за допомогою керуючих слів режиму та наказу, які слідують в певному порядку після появи сигналу системного скидання RST, який обнуляє всі регістри схеми PSI.

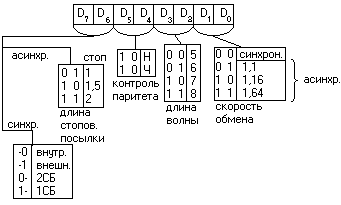

Окремі розряди керуючого слова режиму, які заносяться в регістр режиму, мають наступний зміст: (рис. 2.12.).

Рис. 2.12.

Де: АР - асинхронний режим,

СР - синхронний режим,

Ч - парність,

Н - непарність.

Після надходження сигналу системного скидання RST обнуляються всі регістри схеми, після чого необхідно виконати повторне програмування роботи схеми (рис. 2.13.).

1.Завантажується керуюче слово режиму.

2. Один або два синхробайти (для синхронізації режиму).

3. Керуюче слово наказу.

Після чого можна передавати інформаційні байти.

Рис. 2.13.

Де: АР - асинхронний режим,

УСП - керуюче слово наказу,

УСР - керуюче слово режиму,

КП - кінець передачі.

Окремі розряди керуючого слова наказу мають наступний зміст:

D0 - дозвіл передачі

D2 - дозвіл прийому

D1 - формування сигналу готовності передавача терміналу

D3 - розрив передачі (якщо 0 - здійснюється нормальна робота, 1 - розрив, на виході передавача низький потенціал)

D4 - скидання помилок

D5 - формування сигналу готовності приймача терміналу

D6 — розряд внутрішнього програмного скидання

D7 — розряд дозволу пошуку символу синхронізації.

МП за допомогою команди «вводу» може отримати зі схеми 8251 байт її внутрішнього стану, який має три розряди, що фіксують помилки під час роботи:

D 3 — помилка паритету

D4 - помилка переповнення

D5 — помилка кадру (відсутність стопової посилки при роботі схеми в асинхронному режимі).

При виконанні асинхронного вводу поява низького рівня на вході приймача інтерпретується як стартова посилка.

Усередині схеми 8251 є спеціальний лічильник, який підраховує кількість інформаційних біт і визначає момент появи стопової посилки. По завершенні часу, який виділяється для цієї посилки, повинен виробитися сигнал «готовність приймача». Якщо цей сигнал не виробляється, в розряді D5 слова стану з'являється 1.

При синхронному вводі робота схеми починається з пошуку синхробайта.

При цьому прийнята інформація порівнюється з кодами, які зберігаються у відповідних регістрах. При співпадінні інформації виробляється високий потенціал на виході SYNDET, який є двонаправленим, цей сигнал можна використовувати як сигнал ЗБР. Тільки після вироблення цього сигналу МП почне приймувати інформацію зі схеми ВВ51.