- •Структура и принцип действия микропроцессора классической архитектуры

- •2. Выполнение процессором командного цикла.

- •Машинный и командный цикл cisc микропроцессора

- •4. Структура команд. Способы адресации. Длинное командное слово

- •5 . Организация подпрограмм и использование стековой области памяти.

- •6.Аппаратные средства интрфейса.

- •7.Програмные средства интерфейса для управления электроприводами

- •8. Параллельный и последовательный интерфейс. Области применения

- •9. Принцип действия программируемого таймера.

- •10. Ввод и вывод информации с применением программируемого контроллера прерываний.

- •11.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •12. Программная реализация интервалов времени.

- •13 Аппаратная реализация интервалов времени

- •14. Микросхемы памяти, их основные характеристики и классификация

- •15. Функциональная схема устройства оперативной памяти

- •16. Постоянные запоминающие устройства, их типы и области применения.

- •17. Применение пзу в качестве функционального преобразователя (фп).

- •18.Цифро-аналоговое преобразование.

- •19.Аналого-цифровое преобразование.

- •23. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •24. Влияние времени выполнения программы микроконтроллером на запас устойчивости замкнутой системы.

- •25. Микроконтроллер как динамическое звено.

- •26. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •27. Рекурсивные и нерекурсивные цифровые фильтры, их передаточные функции и структурные схемы. Алгоритм и программа цифрового фильтра.

- •28. Цифровое дифференцирование и интегрирование.

- •31. Паралельная обработка информации. Классификация вычислительных систем с параллельной обработкой информации.

- •32. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •33. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •35. Гарвардская архитектура восьмиразрядных микроконтроллеров pic.

- •36. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •37. Функциональная схема микроконтроллера pic16 и назначение входящих в него устройств.

- •38. Система команд микроконтроллера msp430. Пример составления программы.

- •39 .Система команд микроконтроллеров архитектуры adsp-bf. Пример составления программы

- •40Режимы энергопотребления микроконтроллеров.Примеры

- •41 Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •42. Система команд микроконтроллеров arm7. Пример составления программы.

- •43. Способы повышения эффективности использования конвейера.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Алгоритм расчета сигнала управления в замкнутой системе.

- •47. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием таймера счетчика

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Применение программируемого таймера в системах управления эп.

- •53. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •54 Алгоритм нечеткого управления

- •55. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •56. Применение искусственной нейронной сети в качестве устройства управления.

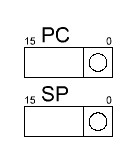

38. Система команд микроконтроллера msp430. Пример составления программы.

2 ,

4, 6 байт – длина команды. Адрес 16-ти

разрядного слова. Адрес расположения

команды всегда чётный, а в двоичной

системе исчисления чётное число всегда

оканчивается нулём.

,

4, 6 байт – длина команды. Адрес 16-ти

разрядного слова. Адрес расположения

команды всегда чётный, а в двоичной

системе исчисления чётное число всегда

оканчивается нулём.

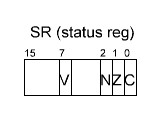

Z =1

если 0. V

– флаг переполнения, равен 1 если число

выходит за допустимые пределы для

знаковых чисел.

=1

если 0. V

– флаг переполнения, равен 1 если число

выходит за допустимые пределы для

знаковых чисел.

Прерывание называется режим работы процессора когда основная или фоновая программа прерывается по запросу внешнего устройства, выполняется ввод/вывод, возврат в основную программу и продолжение её выполнения. Позволяет разгрузить основную программу от опроса внешних устройств.

Наличие прерываний позволяет микроконтроллеру оперативно реагировать на внешнюю обстановку. 27 команд

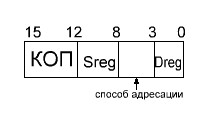

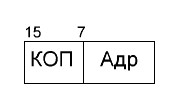

Адресная часть содержит информацию об операндах.

Команда с двумя операндами. 4 бита содержат операции.

D – регистр назначения

S – регистр источник

4 бита позволяют адресоваться к внутренним

регистрам процессора.

бита позволяют адресоваться к внутренним

регистрам процессора.

–

с

одним операндом

–

с

одним операндомБез операнда – команды условного и безусловного перехода

MOV R5, R6 – содержимое R5 помещается в R6, но остаётся в R5.

Ортогональная система команд позволяет с помощью каждой команды обращаться по всем адресам со всеми возможными способами адресации.

Пример:

MOV R5, R15 – R5 в R15

MOV.b R4, R5 – младший бит R4 в младший бит R5

39 .Система команд микроконтроллеров архитектуры adsp-bf. Пример составления программы

-Allreg определяет любой из регистров: R[7:0], P[5:0], SP, FP, I[3:0], M[3:0], A0.X, RETS, RETI, RETN, RETE, LC[1:0], USP и другие;

- DIVS, DIVQ – операции деления со знаком и без;

- MAX, MIN – оп-ции опред. наиб. и наим. из значений в регистрах-ист.;

- ABS абсолютное значение старшей и младшей частей 32 р. регистра;

- RND – округление полуслова

Общая характеристика системы команд:

Система команд ориентирована на С и С++

R1=R2 | R2 R1 - присвоения

R3.H=R7.L | R7.L R3H

R3=AO;

P4=R2;

R2.L=0×FEC3

Арифметическое устр-во допускает выполнение логич. операций с целыми, дробными, знаковыми и беззнаковыми данными.

R1=R2+R3 (S) – суммирование с записью в R1 с учётом насыщения

R2.H=R3.L+R4.H - без учёта насыщения

R2+=R3 | R2=R2+R3;

R2-=R4 | R2=R2+R4;

R2+=0×02 | R2=R2+02;

R3=(R2<<=0X02)

Для 16-разр. Данных в системе команд предусм. одинарные, двойные и тройные итерации. R1=R2+/R3

(R1.H=R2.H+R3.H; R1.L=R2.L-R3.L)

Команды безусловного перехода:

CALL (P3) CALL(PC+P1)

JUMP (P3) – абсолютный переход

JUMP (PC+P1) – относительный переход

Предпочтительнее использовать относительную адресацию.

IF cc JUMP addr cc – назв. флага при котором происх. переход

Флаговый регистр называется ASTAT

сс AZ(ноль); AC(перенос); AN(отрицание); AV(переполнение)

IF cc R4=R5

Если ноль: IF AZ R4=R5

Организация цикла:

addr:P5=#0×FFFF | задано число повторений цикла

L SETUP

(m0,m1)LCO=P5; | m0 – LTO LT1

SETUP

(m0,m1)LCO=P5; | m0 – LTO LT1

m0: A0+=R0*R1 | m1 – LBO LB1

m1:R1=A0 | #FFFFLCO LC1

В этом микропроцессоре для организации циклов исп. 3 вида регистров: LT, LB, LC

LT1 – хранит верхний адрес цикла

LB1 – хранит нижний адрес цикла

LC – количество повторений цикла

Чтобы задать цикл необходимо записать m0, m1 и т.д. Это выполн с помощью команды LSETUP

AO=0×00 P5=#0×FFFF

Подпрограмма выдержки времени:

P3=#0×FFA0 0E00

CALL (P3)

m0:R1-=0×FF

m2:R1-=0×01

IF AZ JUMP m1

JUMP m2

m1:R1=0×00

RET

Когда выполняется команда СALL в программном счётчике хранится адрес след. за ней команды.