- •Структура и принцип действия микропроцессора классической архитектуры

- •2. Выполнение процессором командного цикла.

- •Машинный и командный цикл cisc микропроцессора

- •4. Структура команд. Способы адресации. Длинное командное слово

- •5 . Организация подпрограмм и использование стековой области памяти.

- •6.Аппаратные средства интрфейса.

- •7.Програмные средства интерфейса для управления электроприводами

- •8. Параллельный и последовательный интерфейс. Области применения

- •9. Принцип действия программируемого таймера.

- •10. Ввод и вывод информации с применением программируемого контроллера прерываний.

- •11.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •12. Программная реализация интервалов времени.

- •13 Аппаратная реализация интервалов времени

- •14. Микросхемы памяти, их основные характеристики и классификация

- •15. Функциональная схема устройства оперативной памяти

- •16. Постоянные запоминающие устройства, их типы и области применения.

- •17. Применение пзу в качестве функционального преобразователя (фп).

- •18.Цифро-аналоговое преобразование.

- •19.Аналого-цифровое преобразование.

- •23. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •24. Влияние времени выполнения программы микроконтроллером на запас устойчивости замкнутой системы.

- •25. Микроконтроллер как динамическое звено.

- •26. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •27. Рекурсивные и нерекурсивные цифровые фильтры, их передаточные функции и структурные схемы. Алгоритм и программа цифрового фильтра.

- •28. Цифровое дифференцирование и интегрирование.

- •31. Паралельная обработка информации. Классификация вычислительных систем с параллельной обработкой информации.

- •32. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •33. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •35. Гарвардская архитектура восьмиразрядных микроконтроллеров pic.

- •36. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •37. Функциональная схема микроконтроллера pic16 и назначение входящих в него устройств.

- •38. Система команд микроконтроллера msp430. Пример составления программы.

- •39 .Система команд микроконтроллеров архитектуры adsp-bf. Пример составления программы

- •40Режимы энергопотребления микроконтроллеров.Примеры

- •41 Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •42. Система команд микроконтроллеров arm7. Пример составления программы.

- •43. Способы повышения эффективности использования конвейера.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Алгоритм расчета сигнала управления в замкнутой системе.

- •47. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием таймера счетчика

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Применение программируемого таймера в системах управления эп.

- •53. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •54 Алгоритм нечеткого управления

- •55. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •56. Применение искусственной нейронной сети в качестве устройства управления.

Структура и принцип действия микропроцессора классической архитектуры

Микропроцессор – устройство для обработки информации, представленной в двоичном коде, выполненное в виде одной микросхемы.

tT=1МГц – 60 МГц.

ADSP-BF: 600МГц.

В процессоре формируется адрес, поэтому шина адреса направлена в одну сторону. И по этому адресу происходит выборка команд. Команда по шине данных передается в процессор, где формируется код операций выполнения данной команды.

ОЗУ – предназначено для хранения команды программ и данных.

ПЗУ – предназначено для хранения постоянных данных. ПЗУ хранит информацию при отключении источника питания.

УВВ – предназначено для ввода и вывода информации и включение средства интерфейса.

Шины вместе взятые называются магистральными.

Шина включает в себя набор проводников и шинный формирователь

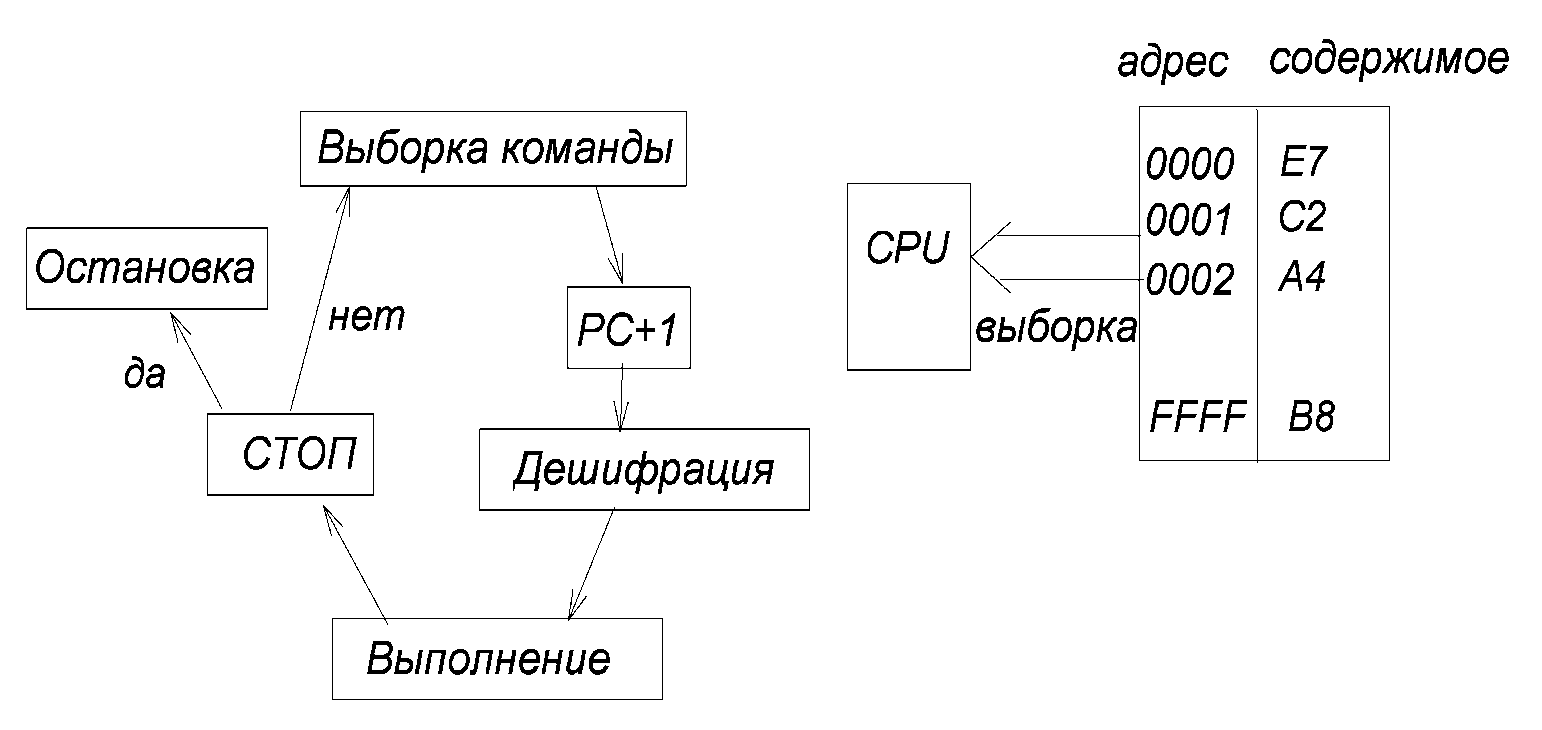

2. Выполнение процессором командного цикла.

Принцип действия микропроцессора заключается в выполнении командного цикла.

Командный цикл – интервал времени, в течение которого выполняется одна команда. Командный цикл может содержать один и более машинных циклов.

Выборка – чтение команды из памяти.

Команды программы записаны в той последовательности, в которой должны выполняться.

Выбирается байт команды, записывается в регистр внутри процессора. Потом программный счетчик инкрементируется. Затем происходит дешифрация, и устройство управления получает информацию о дальнейших действиях, формируется выполнение команды.

Далее управляющим устройством проверяется наличие сигнала «СТОП» ( если «нет», то снова выборка, если «да», то остановка цикла).

Устройство управления может быть выполнено различными методами:

1) Аппаратное (в виде логической схемы)

2) Микропрограммное

Машинный и командный цикл cisc микропроцессора

Командным циклом называется интервал времени, за который выполняется 1 команда.

Машинным циклом называется интервал времени, за который происходит одно обращение к внешним устройствам или памяти.

Машинный цикл – цикл магистрали.

Один командный цикл может содержать несколько машинных циклов.

Если команда оперирует с внутренними регистрами, то машинный цикл может быть один: выборка команд.

Виды машинных циклов:

Запись в память;

Чтение из памяти;

Запись на внешнее устройство чтения;

Прерывание;

Останов.

4. Структура команд. Способы адресации. Длинное командное слово

Команда МП – это такое закодированное двоичное число (слово), которое предопределяет действие МП по обработке информации. Длина команды, как правило, совпадает с длиной слова данных, но она так же может иметь длину, равную 2, 3 и более словам. Каждая команда состоит из кода операции (КОП) и адресной части. КОП сообщает МП что делать и всегда записывается в первом байте. Адресная часть может отсутствовать, то есть команда есть, а адреса нет. Содержание адресной части зависит от способа адресации. При непосредственной адресации в адресной части располагается операнд, при прямой адресации адресная часть содержит адрес операнда. Таким образом, в поле адреса располагается операнд, представляющий собой, либо данные, либо результат операции, либо адрес, по которому хранятся данные.

Способ адресации определяет алгоритм преобразования исходного адреса, указанного в поле адреса команды, в исполнительный, то есть в адрес УВВ памяти или адрес регистра МП. Перечень возможных адресов адресации одной из важнейших характеристик МП. Эффективность использования МП во многом определяется способом адресации к памяти большого объема, так как это является наиболее часто встречаемой операцией, а число бит в команде зависит от используемого способа адресации.

неявная адресация

Тут используется однобайтовая форма команды. Адрес команды неявно задается в КОП команды. Полагают, что операнд находится в определенном внутреннем регистре МП и его специально адресовать не надо. Примером может являться 1-байтовая команда пересылки данных из одного регистра А в другой регистр В, которая состоит из КОП, адреса источника данных (регистр А) и адреса приемника данных (регистр В).

непосредственная адресация

В первом байте – КОП, затем идут данные, занимающие 1 или 2 байта. Тут не используется адрес памяти. Эта адресация выполняется за 2 микроцикла. Сначала идет выборка команды, а потом уже ее выполнение. Команды с такой адресацией могут иметь 2-ух байтный или 3-ех байтный формат. Такая адресация увеличивает производительность и экономит память. , но она обладает наименьшей гибкостью. Пример: LXI В,900H - перенос константы 900H в регистровую пару ВС( КР580)

прямая адресация

В первом байте – КОП, во втором и третьем – адрес (если есть). Адрес указывает область памяти, в которой находятся подлежащие обработке данные. Программист может явным образом задать адрес нужных данных. Такая адресация требует дополнительных микроциклов. Сначала надо произвести выборку КОП команды, затем надо извлечь из памяти еще 2 байта, адрес обрабатываемых данных. Время выполнения адресации в 2 раза больше чем у непосредственной адресации.

косвенная адресация

Реализуется командами длиной в одно слово. Тут кроме КОП еще указывается номер регистра, содержимое которого означает адрес масторасполажения данных в памяти. Например, при такой адресации в 8-разрядном МП указывается в какой регистровой паре находится адрес данных в памяти. Такая адресация удобна при неоднократном обращении к памяти, особенно в случае их организации в виде списка или файла, когда адрес надо вычислять.