- •Федеральное агентство по образованию и науке рф государственное образовательное учреждение высшего

- •1. Предмет и задачи курса

- •2. Мера информации

- •3. Принципы организации и построения эвм

- •3.1. Принцип декомпозиции Глушкова

- •3.2. Принцип программного управления фон Неймана

- •3.3. Принцип микропрограммного управления

- •4. Организация интерфейса

- •4.1. Уровень лэ

- •4.2. Уровень оэ

- •4.3. Уровень сэ

- •5.Обмен информацией между ядром эвм и ву (увв)

- •6.Микрооперация сдвига

- •7. Основные характеристики и режимы работы эвм

- •8. Вычислительные системы

- •9. Арифметико-логическое устройство

- •9.1. Двоичный сумматор

- •9.2. Беззнаковое представление чфз.

- •9.3. Представление чпз

- •9.4. Кодирование

- •9.5. Параллельный сумматор

- •9.6. Десятичный сумматор

- •9.7. Умножитель

- •9.8. Вычисление логических условий

- •9.9. Схема однобайтных логических операций (соло)

- •9.10. Блок контроля и диагностики (бкд)

- •9.11. Пороговая схема

- •Мажоритарные элементы

- •10. Устройства управления в процессоре

- •10.1. Адресный базис (аб)

- •10.2. Стек и его использование в моа

- •10.3. Синтез адреса на структурном уровне

- •Как строится память в современном эвм?

- •11.2. Основная память

- •Триггер.

- •11.3. Зу с однокоординатной выборкой (со словарной организацией)

- •11.4. Зу с двухкоординатной выборкой (с матричной организацией)

- •11.5. Зу с трехкоординатной выборкой (со страничной организацией)

- •Как увеличить ёмкость зу при различных ситуациях?

- •12. Организация оп

- •12.1. Блочная организация памяти.

- •12.2. Циклическая организация памяти

- •12.3. Блочно-циклическая организация памяти.

- •12.4. Многопортовая память

- •12.5. Ассоциативная память

- •13. Кэш память

- •13.1. Архитектура кэш и оп и их взаимосвязь

- •Что влияет на эффективность такой архитектуры оп с кэш?

- •Емкость кэш памяти.

- •13.2. Способы отображения оп на кэш память

10.3. Синтез адреса на структурном уровне

Команда имеет две части.

К

АЧ |

ОЧ |

Как уменьшить адресную составляющую операционной части?

Сжать АЧ внутри ОЧ – путем использования 2х форматных и 2х адресных команд.

Классический метод – одноформатная, одноразрядная команда(все в одном формате, 1 адрес, следовательно 3 одноадресные команды нужно вставить в программу – это неэкономично).

Сейчас применяются 2х адресные команды.

В состав П. входят такие элементы памяти, как регистровая память(16-32 разряда, максимальное число разрядов на один адрес – 4-5)

ОП – разрядность – 20-30 разрядов. Это гораздо больше адресации РОНа.

В качестве приемника может быть РОН или ячейка памяти. В настоящее время в среднем все команды 2х разрядные и как минимум 2х форматные.

Также существует короткий формат команды.

КО – код операции. РОНЫ –источники. Когда 2 ячейки адреса, то результат размещается по 1-му адресу – всего требуется 16 разрядов.

При длинном формате используется и ОП.

Включает в себя: код операции, РОН, в качестве одного из источников информации, все остальное для адресного задания ячейки ОП.

Чтобы вычислить адрес 2го источника, нужно вычислить, какие команды могут быть.

3 опорных точки:

1) Непосредственная адресация. В 20-ти разрядном поле размещается сам операнд, который участвует в операции(чаще всего это const)

2) Прямая адресация. При ней указывается способ вычисления 2-го адреса.

В2 - базовый адрес

D2 –смещение.

Рисунок 123. Сегменты ОП, используемые при прямой адресации

Адрес=В2+D2 Арифметическое сложение по модулю(эта операция осуществляется в ОП)

Косвенная адресация. При такой адресации указывается адрес адреса, т.е. сначала В2 заносится в один из РОНов и в этом поле ОП указывается адрес РОНа. Из РОНа берут адрес и обращаются в ОП. Экономия – за счет формата и того, что команда двухадресная.

11. Память

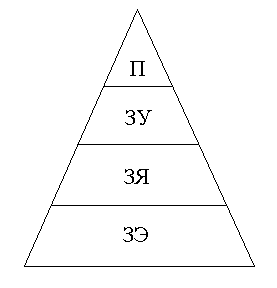

Иерархическое представление структуры памяти в первом приближении изображено на рис. 124:

Краткие обозначения:

П - память

ЗУ – запоминающее устройство

ЗЯ – запоминающая ячейка

ЗЭ – запоминающий элемент

Рисунок 124. Иерархическая структура памяти

Система использует иерархию, связывающую нижний с верхним уровнем:

П=∑ЗУ

ЗУ=∑ЗЯ=ОЭП

ЗЯ=∑ЗЭ

11.1. Режимы работы памяти

Обращение.

Активизирует память. Устанавливаются режимы: запись, чтение, регенерация.

Хранение.

Нет сигнала обращения. Память отключена от внешних устройств и в первую очередь от шины данных.

Память обычно адресуется. Она работает по принципу «Книга – страница – строка – буква».

Основные характеристики.

Емкость информации.

Быстродействие.

Так же вводят еще одну характеристику – стоимость хранения 1бита информации. Чем больше емкость, тем меньше стоимость и чем больше быстродействие, тем больше стоимость.

Типы запоминающих элементов.

Триггер.

Запоминает 1 бит информации.

Запоминающая емкость.

Используется в динамических запоминающих устройствах (ДОЗУ). Плотность записи в ДОЗУ выше на порядок чем в статическом ЗУ и в ДОЗУ есть режим регенерации – постоянного восстановления на запоминающихся ёмкостях.

Плавкие вставки.

Если плавкая вставка разрушается, то это эквивалентно постоянной записи “0”, не разрушается - “1” – постоянно запоминающее устройство (ПЗУ).

Динамическое и статическое ОЗУ – элементы электрозависимой памяти. Работают только при наличии электропитания.

Намагниченность магнитного материала.

Плотность записи очень высока. Используется в винчестере. Винчестер – энергонезависимая память, как и ПЗУ.

Компактные диски.

Память заключена в рельефе дорожки. Способ чтения: на диск попадает луч лазера и по характеру отражения определяется “0” или “1”.