Cборник_ЛР

.pdfЛабораторная работа № 4

ИЗУЧЕНИЕ ДИОДНО-ТРАНЗИСТОРНЫХ (ДТЛ) И ТРАНЗИСТОРНО-

ТРАНЗИСТОРНЫХ (ТТЛ) ЛОГИЧЕСКИХ СХЕМ

Цель работы: изучение принципов работы ДТЛ и ТТЛ схем, приобретение навыков аналитического расчета и экспериментального исследования их статических характеристик.

Теоретические сведения

Введение

Первые схемы диодно-транзисторной логики выпускались за несколько лет до изобретения интегральных схем. Затем с конца 50-х - начала 60-х годов их вместе с другими типами логики стали изготавливать в интегральном исполнении.

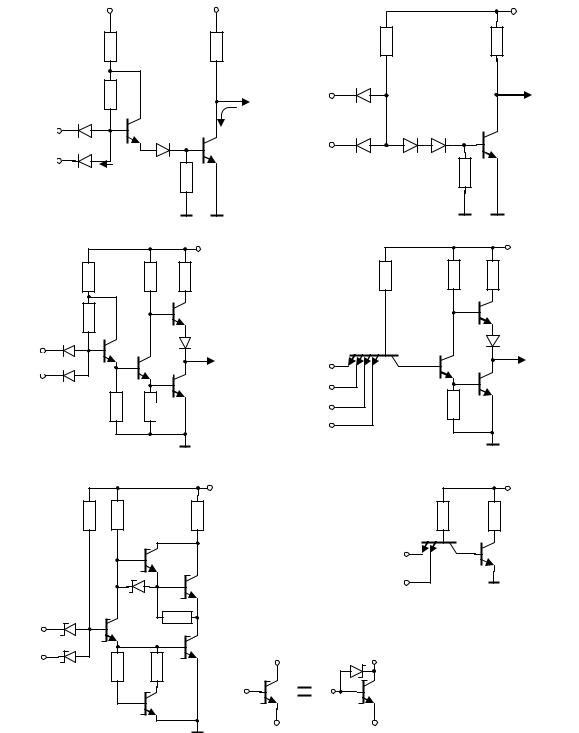

Диодно-транзисторные и транзисторно-транзисторные логические схемы являются функциональными и электрическими аналогами, которые различаются в основном конструкцией входного узла. В ДТЛ схеме входная функция “И” реализована с помощью диодов (рис.4.1а,б,в).

С учетом особенностей интегральной технологии в первой половине 60-х

годов была предложена разновидность транзисторных схем, в которых на входе группу диодов заменил многоэмиттерный транзистор ТТЛ-схемы (рис.4.1,г,е). Это позволило существенно повысить быстродействие схемы. Использование одного источника питания (а в некоторых ДТЛ схемах применяются 3 источника), достаточно высокое быстродействие, высокая помехо

73

|

UИП1 |

|

UИП2 |

|

|

|

UИП |

R1 |

|

|

R4 |

R1 |

|

R3 |

|

R2 |

|

|

Выход |

D1 |

|

|

Выход |

|

|

|

|

|

|

||

D1 |

|

|

0 |

Входы |

|

|

|

Вход A |

|

D3 |

Iвых |

D3 D4 |

|

|

|

|

|

|

T1 |

||||

Uy |

T1 |

|

T2 |

|

|

|

|

Вход B |

|

|

D2 |

|

|

|

|

0 |

|

|

R2 |

|

|

||

D2 I |

R3 |

|

|

|

|

||

|

вх |

|

|

|

|

|

|

|

а |

|

|

|

б |

|

|

|

|

|

UИП |

|

|

|

UИП |

R1 |

R4 |

|

R6 |

R1 |

R4 |

|

R6 |

|

|

|

|

|

|||

R2 |

|

|

T3 |

|

|

|

T3 |

D1 |

|

|

D3 |

|

|

|

D |

|

T1 |

|

|

|

|

||

Входы |

|

Выход |

|

|

T2 |

Выход |

|

|

T2 |

A |

|

||||

|

|

|

|

T4 |

|||

D2 |

|

|

T4 |

B |

|

|

|

|

|

|

C |

R3 |

|

|

|

R3 |

|

R5 |

|

|

|

||

|

|

D |

|

|

|

||

|

|

|

|

|

|

|

|

|

в |

|

|

|

г |

|

|

|

|

|

UИП |

|

|

UИП |

R1 |

R2 |

|

R6 |

|

R1 |

R2 |

|

|

T3 |

|

Входы |

T1 |

T2 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

T4 |

|

|

|

D1 |

D3 |

|

|

|

е |

|

|

|

|

|

|

||

Входы |

T1 |

R5 |

|

|

|

|

|

T5 |

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

D2 |

R3 |

R4 |

|

|

|

|

|

|

T2 |

|

|

|

|

д

Рис.4.1. Разновидности ДТЛ- и ТТЛ-элементов: (а) ДТЛ-элемент с простым выходным каскадом; (б) ДТЛ-элемент с термостабилизецией; (в) ДТЛэлемент со сложным выходным каскадом; (г) ТТЛ-элемент со сложной нагрузкой; (д) ДТЛШ; (е) ТТЛ-элемент с простой нагрузкой.

74

защищенность, устойчивость к технологическому разбросу сделали ТТЛ ИС самыми популярными и распространенными микроэлектронными изде-

лиями 60-х - 70-х годов.

К настоящему времени ТТЛ ИМС и их разновидности с диодами Шоттки

(ТТЛШ) являются компонентной базой биполярных ИС малой и средней сте-

пени интеграции. В самых распространенных маломощных вентилях ТТЛШ входная логическая функция “И” реализуется на диодах Шоттки, поэтому их можно было бы именовать ДТЛШ (рис.1,д) [1, 2].

Работа базовых элементов

Все приведенные на рис.4.1 логические схемы реализуют функцию И-НЕ,

в частности, для входов А и В на выходе имеем AB .

Рассмотрим подробнее назначение и режимы работы элементов ДТЛ-

схемы (рис.4.1,а). Если на оба входа А и В подано напряжение, соответствую-

щее логическому нулю, диоды D1 и D2 будут открыты. От источника питания

UИП1 через резисторы R1, R2 и диоды D1, D2 протекает ток. В состоянии логи-

ческого нуля на входе входной ток вытекает из схемы, а потенциал общего узла анодов диодов U y0 можно легко найти, зная Uвх0 ,

U y0 Uвх0 Uдиода ,

где Uдиода - падение напряжения на открытом диоде.

При этом, если на входах потенциалы различаются, то Uy определяется более низким значением Uвх. Величина U y0 недостаточна для отпирания по-

следовательной цепочки эмиттерный переход транзистора T1 - диод D3 -

эмиттерный переход транзистора T2. Поэтому выходной транзистор T2 за-

крыт, (точнее говоря, T2 работает в нормальном активном режиме (НАР) с то-

ком эмиттера равном нулю). Через резистор R4 ток не протекает, поэтому по-

75

тенциал на выходе Uвых = UИП2. Это состояние соответствует логической еди-

нице,

U вых1 U ИП2 . |

(4.1) |

Если хотя бы на одном из входов (предположим, на входе В) повысить на-

пряжение до величины Uвх1 B UвхA Uвх0 A , то диод D2 закроется, поскольку

Uвх1 B U у0 Uвх0 A U D .

Когда на все входы одновременно подано напряжение логической едини-

цы Uвх1 , диоды D1 и D2 запираются, потому что теперь потенциал Uy ограни-

чен сверху величиной, равной суммарному падению напряжения на прямо-

смещенных эмиттерных переходах транзисторов T1 и T2 и диоде D3. Это зна-

чение U 1y Uвх1 . Транзистор T1 благодаря способу включения резистора R2

(рис.4.1,а) работает в нормальном активном режиме (НАР) и обеспечивает усиление тока в базовой цепи транзистора T2, в результате чего последний входит в режим насыщения. Напряжение на выходе

Uвых UКЭн2 .

Это состояние соответствует логическому нулю

U вых0 U КЭн . |

(4.2) |

Резистор R4 ограничивает ток коллектора транзистора T2, предохраняя его от “сгорания”, и позволяет повысить быстродействие при выключении T2.

Резистор R3 необходим для ускорения выключения транзистора T2 при изме-

нении напряжения на входе с Uвх1 на Uвх0 .

Использование в данной схеме двух источников питания не обязательно.

Однако, увеличение UИП1 и уменьшение UИП2 способствует повышению на-

грузочной способности схемы. При этом минимальное допустимое значение

UИП1 и UИП2 примерно равно падению напряжения на трех прямо смещенных

р-n-переходах.

76

Сходный принцип работы характерен и для других схем данного класса

(см. рис.4.1). Введение сложных выходных каскадов (рис.4.1в,г,д) позволяет существенно увеличить нагрузочную способность. Ряд других усовершенст-

вований касается методов повышения быстродействия, снижения рассеивае-

мой мощности и т.д. Чтобы представить некоторые особенности, связанные с переходом от ДТЛ к ТТЛ-схемам, рассмотрим подробнее назначение и режи-

мы работы элементов TТЛ-схемы со сложным выходным каскадом (рис.4.1,г).

Если на все входы (эмиттеры транзистора T1) одновременно или хотя бы на один из них подано напряжение Uвх0 , то T1 работает в режиме насыщения с током коллектора, равным нулю (ток не может втекать в базy транзистора T2).

Потенциал коллектора T1

U К1 U Б2 U вх0 U КЭн1 ,

который не превышает граничного напряжения UБЭгр2, и поэтому не дает воз-

можности открыться транзистору T2. Следовательно, ток через T2 практиче-

ски не протекает, и он работает в нормальном активном режиме с током эмит-

тера IЭ2 = 0. Поскольку падение напряжения на резисторе R3 также равно нулю, транзистор T4 закрыт, a через резистор R2 протекает только ток базы

T3, создавая незначительное падение напряжения на R2, которым во многих случаях можно пренебречь. Транзистор T3 работает в НАР, диод D также от-

крыт. Это состояние соответствует логической единице на выходе схемы:

I 1

Uвых U ИП U БЭн3 U D вых R2 U ИП U БЭн3 U D .

N 1

Втом случае, когда на входы одновременно поданы потенциалы Uвх1 ,1

эмиттерные переходы транзистора T1 запираются, и он переходит в инверс-

ный активный режим (ИАР). Ток из коллектора T1 втекает в базу транзистора

T2, включая последний и вводя его в насыщение. Ток, протекающий через ре-

зистор R3, повышает потенциал базы транзистора T4, отпирая его и вводя в

режим насыщения. С другой стороны, коллекторный ток транзистора T2 соз-

77

дает большое падение напряжения на R2. За счет этого потенциал базы T3 по-

нижается, и он закрывается. Для того, чтобы надежно запереть транзистор T3

при U |

вх |

U1 |

, последовательно с его эмиттерным переходом включен диод |

|||||

|

вх |

|

|

|

|

|

|

|

D. Это состояние эквивалентно логическому нулю на выходе схемы |

||||||||

|

|

|

U 0 |

U * |

I 0 |

r U |

КЭн4 |

, |

|

|

|

вых |

КЭн4 |

К4 |

К |

|

|

где UКЭн* - напряжение коллектор-эмиттер насыщения транзистора без учета падения напряжения на rК; rК - сопротивление тела коллектора (в указанном случае транзистора T4); IК0 4 - ток в цепи коллектора T4, который втекает в не-

го (рис.4.1,г). Резистор R4 ограничивает ток в момент переходного процесса,

когда открыты оба транзистора Т3 и Т4.

Режимы работы элементов остальных логических схем приведены в таб-

лице 1.

Расчет токов ДТЛ схемы

Рассмотрим схему, изображенную на рис.4.1,а. Если на какой-либо вход подано напряжение Uвх0 , соответствующий диод открыт, и входной ток выте-

кает из схемы. В этом случае транзистор T1 закрыт.

Предположим, что диоды D1 и D2 одинаковы и открыты. Тогда по входам

А и В протекают равные токи

Iвх0 A Iвх0 B |

|

U |

ИП |

U |

D |

U 0 |

|

|||||||

|

|

|

|

|

|

|

|

вх |

, |

|||||

|

|

|

2 R1 R2 |

|

||||||||||

|

|

|

|

|

|

|

|

|||||||

а суммарный ток, протекающий через резисторы R1 и R2, равен |

||||||||||||||

I 0 |

U |

ИП |

U |

D |

U |

0 |

|

|

|

|||||

|

|

|

|

вх |

. |

|

(4.3) |

|||||||

|

|

R1 R2 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|||||||

78

Таблица 4.1

Режимы работы элементов ДТЛ и ТТЛ-схем для двух логических состояний

Элемент |

|

Uвх Uвх0 |

|

|

Uвх Uвх1 |

|

||

|

Рис.1,в |

Рис.1,д |

Рис.1,е |

Рис.1,б |

Рис.1,в |

Рис.1,д |

Рис.1,е |

Рис.1,б |

Т1 |

НАР |

НАР |

ННР |

НАР |

НАР |

ННР |

ИАР |

ННР |

|

c IЭ = 0 |

c IЭ = 0 |

c IК = 0 |

c IЭ = 0 |

|

|

|

|

Т2 |

НАР |

НАР |

НАР |

- |

ННР |

ННР |

ННР |

- |

|

c IЭ = 0 |

c IЭ = 0 |

c IЭ = 0 |

|

|

|

|

|

Т3 |

НАР |

НАР |

- |

- |

НАР |

НАР |

- |

- |

|

|

|

|

|

c IЭ = 0 |

c IЭ = 0 |

|

|

Т4 |

Отсечка |

НАР |

- |

- |

ННР |

НАР |

- |

- |

|

|

|

|

|

|

c IЭ = 0 |

|

|

Т5 |

- |

Отсечка |

- |

- |

- |

ННР |

- |

- |

D3 |

открыт |

закрыт |

- |

закрыт |

закрыт |

закрыт |

- |

открыт |

D4 |

- |

- |

- |

закрыт |

- |

- |

- |

открыт |

Примечание: НАР - нормально-автивный режим, ИАР - инверсно-активный режим, ННР - нормальный насыщенный режим.

79

Этот же ток I 0 протекает во входной цепи, если открыт только один вход-

ной диод. Через все остальные элементы схемы ток практически не протекает.

В случае, когда на все входы схемы подан логический уровень единицы

Uвх1 , диоды D1 и D2 запираются, а транзисторы T1, Т2 и диод D3 открывают-

ся. Во входной цепи токи практически отсутствуют. Реально, входной ток Iвх1

определяется током утечки обратносмещенного диода. Через резистор R1 про-

текает ток, равный току эмиттера T1 ( IЭ = IК + IБ), через R2 - ток базы транзи-

стора T1. Поскольку T1 работает в НАР, то IЭ = ( N + 1)IБ , откуда следует, что

I R2 |

|

U ИП1 U БЭн1 U D U |

БЭн2 |

|

|||||||||||

|

|

R1 N 1 R2 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||

I R1 |

U ИП1 U БЭн1 U D U БЭн2 |

N 1 . |

(4.4) |

||||||||||||

|

R1 N 1 R2 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||

Ток резистора R3 находится из условия, что падение напряжения на рези- |

|||||||||||||||

сторе равно UБЭн2 , то есть |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

R3 |

U БЭн2 . |

|

|

|

|

||||

|

|

|

|

|

|

|

R3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

При отсутствии или малом числе нагрузок ток через резистор R4 можно |

|||||||||||||||

легко определить по формуле |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

I |

R4 |

|

UИП2 UКЭн2 |

|

|

UИП2 |

|

(4.5) |

||||||

|

|

|

|||||||||||||

|

|

|

|

|

R4 |

|

R4 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Однако при подключении к выходу данной схемы большого числа иден-

тичных ключей напряжение Uвых0 может существенно возрасти за счет увели-

чения падения напряжения на сопротивлении тела коллектора T2 от суммар-

ного тока нагрузочных схем Iвых0 (рис.1,а).

80

Статические характеристики ДТЛ-схемы

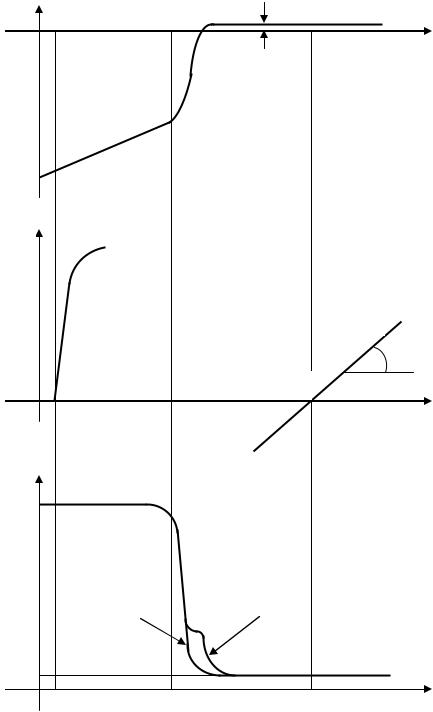

Входная характеристика ДТЛ схемы изображена на рис.4.2,а. Для случая,

когда напряжение увеличивается на входе А, а на входе В UвхB Uвх1

(рис.4.1,а), соотношение (4.3) описывает участок входной характеристики в области значений

0 U вхA U вх.гр ,

где величина Uвх.гр = UБЭгр1 + UD + UБЭгр2 – UD. При этом значении входного напряжения начинает закрываться входной диод и входной ток резко умень-

шается.

Одна из ветвей выходной характеристики (рис.4.2,б) соответствует слу-

чаю, когда на все входы подано напряжение Uвх1 , другая - когда хотя бы на одном входе потенциал равен Uвх0 . Первая соответствует выходной ВАХ транзистора T2 на участке его работы в режиме насыщения. Вторая же (тран-

зистор T2 в этом случае закрыт) - линейная функция с наклоном, соответст-

вующим значению сопротивления резистора R4.

Различают передаточные характеристики нагруженной и ненагруженной ДТЛ-схемы (рис.4.2,в). В первом случае на зависимости Uвых = f(Uвх) наблюдается характерный излом. Этот излом имеет место на участке характеристи-

ки, где транзистор T2 работает в нормальном активном режиме. Изменение наклона передаточной характеристики на изломе означает для исследуемой

(нагруженной) схемы некоторое снижение коэффициента усиления по напря-

жению dU вых  dU вх . Это можно объяснить следующим образом. Нормальнo-

dU вх . Это можно объяснить следующим образом. Нормальнo-

активный режим транзистора T2 характеризуется следующим равенством для токов IК2 = NIБ2. Увеличение тока коллектора T2 за счет резкого увеличения тока нагрузки (рис.4.2,а) требует соответствующего увеличения его тока базы.

На этом участке входные диоды нагруженной схемы D1 и D2 еще не полно-

81

Iвх |

Uвх0 |

Uвх.гр. |

|

|

|

Uвх1 |

U вх |

|

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

Iвх |

|

|

|

|

|

|

|

|

||

а

Iвх0

Iвых

Uвх1

б

Uвх0

Uвых1 UИП

Uвых0 |

|

|

|

U вых |

U вых

Uвых1

|

|

в |

|

Схема |

|

|

|

|

Схема не |

нагружена |

|

|

|

|

нагружена

Uвых0

U вх

Рис.4.2. Статические характеристики ДТЛэлемента:

а - входная; б - выходная; в - передаточная

(ctg( ) = R4)

82