Cборник_ЛР

.pdf4.Обеспечивают ли эмиттерные повторители в ЭСЛ-элементе усиление по напряжению?

5.В каких режимах работают транзисторы Т4 и Т5 ЭСЛ-элемента (рис.2.1)

на различных участках выходной характеристики?

6. Если на одном из входов ЭСЛ-элемента (рис.2.1) напряжение равно опорному, а сопротивление R1 = R2, то равны ли напряжения на базах транзи-

сторов Т4 и Т5? На остальных входах напряжение равно нулю.

7. Если на всех входах ЭСЛ-элемента (рис.2.1) напряжение равно опорно-

му, то будут ли одинаковыми токи резисторов R1 и R2? Все транзисторы в схеме одинаковые.

8.Почему для обеспечения одинаковой величины логического перепада на выходах ЭСЛ-элемента (рис.2.1) сопротивления резисторов R1и R2 различны?

9.Во сколько раз в ЭСЛ-элементе (рис.2.1) изменится ток IR5, протекаю-

щий через резистор R5, при изменении Uвх со значения U0 на U1 ?

10. Какое неравенство и почему должно выполняться для ЭСЛ-элемента

(рис.2.1): R1 > R2 или R1 < R2?

11.В чем состоит необходимость введения эмиттерных повторителей в ЭСЛ-элемент?

12.Если заданы величины напряжения логических уравнений ЭСЛ-эле-

мента, то как выбирается напряжение источника опорного напряжения?

13. Какой величиной ограничено максимальное значение логического пе-

репада в ЭСЛ-схеме (рис.2.1) и почему?

14. Если к выходам ЭСЛ-элемента (рис.2.1) подключить входы таких же элементов, то возникает ли выходной ток (ток нагрузки)? Какое он имеет на-

правление и значение для Uвых0 и Uвых1 ?

15. Уменьшение величины какого логического уровня Uвх0 или Uвх1 ЭСЛ-

элемента нарушает его правильное функционирование, если величины напря-

жения источника питания и опорного напряжения остаются неизменными?

53

16. Вывести формулу расчета средней мощности, потребляемой ЭСЛ-эле-

ментом (рис.2.1) от источника питания UИП.

17. Ток нагрузки какого направления для ЭСЛ-элемента (рис.2.1) может привести: к насыщению транзисторов T1, T2? к запиранию транзисторов Т4,

Т5?

18. Как изменится передаточная характеристика ЭСЛ-элемента (рис.2.1),

если резистор R5 заменить идеальным генератором тока, задающим ток I0,

равный по величине току, протекавшему через R5 при Uвх = U0?

19. Как путем введения дополнительных эмиттерных повторителей в ЭСЛ-элемент (рис.2.1) можно увеличить максимально допустимую величину логического перепада?

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

1.Алексенко А.Г. Основы микросхемотехники. Лаборатория знаний. М.

Бином 2009.

2.Шишина Л.Ю. Основные устройства цифровой микросхемотехники.

Часть 1. Учебное пособие. Москва 2013, РИО МИЭТ.

3.Хоровиц П., Хилл У. Проектирование цифровых устройств [Текст] :

Пер. с англ. Т.1 / Д. Ф. Уэйкерли. - М. : - 544 с. - (Библиотека современ-

ной электроники. Постмаркет, 2002.

54

Лабораторная работа № 3

ИССЛЕДОВАНИЕ СТАТИЧЕСКОГО ЭЛЕМЕНТА ПАМЯТИ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ

Цель работы: изучение принципа работы, основных переключательных характеристик и методов определения функциональных параметров элемента памяти (ЭП).

Теоретические сведения.

Введение

С развитием интегральной технологии произошел существенный скачок в объеме производства запоминающих устройств (ЗУ). Постепенное снижение их удельной стоимости и габаритов послужило причиной вытеснения других типов ЗУ на рынке современной вычислительной техники.

Внастоящее время для интегральной технологии не является предельной информационная емкость в миллиард бит на один кристалл. В таких схемах наиболее ярко проявляется нетрадиционность схемотехники микроэлектронных устройств.

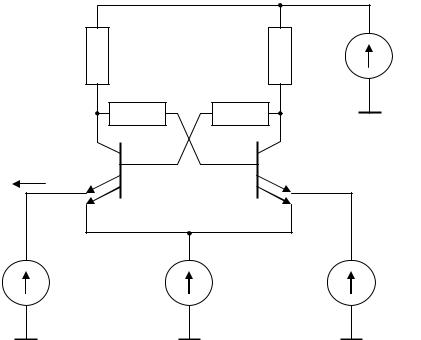

Внастоящей работе исследуется элемент памяти (ЭП) (рис.3.1), построенный на биполярных двухэмиттерных транзисторах, аналогичный используе-

мым в интегральных схемах памяти с произвольной выборкой.

55

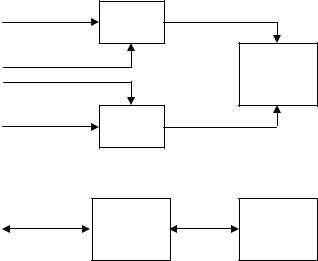

Функциональная схема ЭП.

На рис.3.2,а приведена функциональная схема ЭП ЗУ с произвольной вы-

боркой (ТТЛ-типа). В нее входят:

-бистабильная ячейка (БЯ);

-цепи управления бистабильной ячейкой при записи информации (ЦЗ);

-цепи управления бистабильной ячейкой при считывании информации

(ЦС).

R1 |

|

R3 |

UИП |

|

|

|

|

R2 |

R4 |

|

|

UК1 |

|

UК2 |

|

IД |

|

|

|

Э2 |

|

Э2 |

|

Э1 |

|

Э1 |

|

UД |

UA |

|

Uоп |

Рис.3.1. Схема элемента памяти

БЯ обеспечивает хранение информации, записанной в нее через ЦЗ. Вхо-

ды Азап и Асч необходимы, во-первых, для выбора из множества ЭП в ЗУ толь-

ко одного и, во-вторых, для определения режима работы ЭП. При соответст-

вующем значении логического уровня на входе Асч происходит считывание

56

информации и на выходе ЭП Dсч появляется логический уровень, соответст-

вующий той информации, которая была предварительно записана в БЯ.

Dзап

ЦЗ

Aзап

БЯ |

а |

|

|

Aсч

ЦЗ

Dсч

D |

|

|

|

б |

ЦУ |

|

БЯ |

||

|

|

|||

|

|

|

||

|

|

|

|

|

A

A

Рис.3.2. Функциональная схема ЭП ЗУ с произвольной выборкой (а)

и вариант совмещения входных и выходных данных (б)

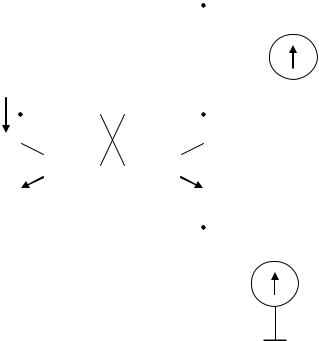

При наличии напряжения питания БЯ статического ЭП находится в одном из двух устойчивых логических состояний, либо в состоянии “0”, либо - “1”. В

ЭП (рис.3.1) используется БЯ на биполярных транзисторах, которую можно представить в виде, приведенном на рис.3.3.

При конкретной реализации информационный вход Dвх и выход Dсч ЭП могут быть совмещены. Аналогично объединяются и управляющие режимом работы ЭП входы Азап и Асч. В результате функциональная схема ЭП принима-

ет вид, показанный на рис.3.2,б. Оба входа: информационный D и адресный А через цепи управления (ЦУ) задают режим работы ЭП, т.е. “хранение”, “счи-

тывание” или “запись” и то состояние, в которое он переводится при записи.

Элемент памяти (рис.3.1) представляет собой конкретную реализацию функциональной схемы (рис.3.2,б). Он управляется по двум входам, на кото-

57

рые подано напряжение UД и UA (рис.3.1). На третьем входе ЭП напряжение

Uoп поддерживается постоянным независимо от режима работы ЭП. В качест-

ве цепей управления (ЦУ) ЭП (рис.3.1) используются первые и вторые эмит-

теры транзисторов Т1 и Т2.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R3 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UИП |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2 |

|

|

|

R4 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

IК1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

T1 |

|

|

|

|

|

|

|

|

|

|

T2 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Э1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Э1 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UА

Рис.3.3. Бистабильная ячейка

Режимы работы ЭП.

Элемент памяти, используемый в интегральных схемах памяти с произ-

вольной выборкой, работает в трех режимах:

1.Режим хранения.

2.Режим выборки/считывания.

3.Режим выборки/записи.

ЭП (рис.3.1) является симметричным, т.е. R1 = R3, R2 = R4, а параметры транзисторов Т1 и Т2 идентичны, причем площади их эмиттеров одинаковы.

Режим хранения задается тем, что UA UA0 , где

58

U 0 |

U |

Д |

, U |

оп |

, |

|

(3.1) |

||

|

A |

|

|

|

|

|

|||

Это самый низкий потенциал в схеме. |

|

|

|

|

|

|

|

||

При этом должно выполняться условие |

|

|

|

|

|||||

U |

ИП |

U 0 |

U |

БЭн |

, |

(3.2) |

|||

|

A |

|

|

|

|

||||

что позволит одному из транзисторов быть открытым и ЭП - в устойчивом со-

стоянии.

При выполнении условия (3.1) вторые эмиттеры транзисторов ЭП

(рис.3.1) оказываются под (более положительным) меньшим напряжением по сравнению с первым эмиттером открытого транзистора, что может привести к отрицательному напряжению смещения. Следовательно, вторые эмиттеры за-

крыты. В этом случае, изменение напряжения на информационном входе D не вызовет переключения ЭП, который в этом случае можно рассматривать как БЯ вида рис.3.3.

Предположим, что открыт транзистор Т1 и это состояние ЭП будем назы-

вать “0”. Определим режим работы открытого транзистора, который может

быть либо нормально-активным, либо насыщенным.

По закону Ома для схемы (рис.3.3) можно записать выражения для макси-

мального тока транзистора:

|

|

|

|

|

|

|

U |

ИП |

U |

0 |

U |

КЭ1 |

|

|

|

|

|

|

|||||||

|

|

|

IК1 |

|

|

|

|

|

A |

|

|

, |

|

|

|

(3.3) |

|||||||||

|

|

|

|

|

|

|

|

|

|

R1 |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

U |

ИП |

U 0 |

U |

БЭн |

|

|

|

|

|

|||||||||

|

|

|

|

IБ1 |

|

|

|

|

|

A |

|

|

. |

|

|

|

(3.4) |

||||||||

|

|

|

|

|

|

|

|

|

R3 R4 |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Известно, что если для открытого транзистора выполняется неравенство |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

IК |

|

IБ β N , |

|

|

|

|

|

|

|

(3.5) |

|||||||

то он работает в режиме насыщения. На основании (3.3) и (3.4) имеем |

|

||||||||||||||||||||||||

|

I |

|

|

|

|

|

|

U |

|

|

|

U |

|

|

|

|

|

R4 |

|

||||||

|

К1 |

|

|

|

|

|

БЭ1 |

КЭ1 |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3.6) |

|||||||||

|

|

|

1 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

1 |

|

. |

||||||

|

I Б1 |

|

|

U |

|

|

|

U |

U |

|

|

|

|

R1 |

|

||||||||||

|

|

|

ИП |

A |

БЭ1 |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

59

Исходя из требования (3.2) и того, что R4 < R1, следует, что каждое из вы-

ражений в скобках (3.6) по величине не превышает двух, а IК1/IБ1 < 4. Коэффи-

циент усиления транзисторов N интегральных схем памяти больше 20. Сле-

довательно, условие (3.5) выполняется в широком интервале значений UИП и

U A0 , а транзистор Т1 работает в режиме насыщения. В результате UКЭ1 = UКЭн,

UБЭ1 = UБЭн, a UБЭ2 = UКЭ1 = UКЭн. Так как UКЭн < UБЭгр, то у транзистора Т2 р-n переход база-эмиттер закрыт, закрыт и транзистор Т2.

Таким образом, показано, что в БЯ статического типа (рис.3.3) всегда один из биполярных транзисторов открыт и насыщен, а другой - закрыт.

Выборка. Режим считывания. В отличие от режима хранения, когда ток открытого транзистора протекает по цепи источника напряжения UA, теперь необходимо создать условия, когда по наличию или отсутствию тока в цепи

UД можно было бы судить о состоянии ЭП. Для этого необходимо закрыть первые эмиттеры ЭП (рис.3.1), что достигается при условии

U A U A1 , |

|

|

||||

где |

|

|

|

|

|

|

U1 |

U |

Д |

, U |

оп |

. |

(3.7) |

A |

|

|

|

|

||

Причем необходимо исключить возможность переключения ЭП в другое

состояние, для чего на выходе D устанавливается напряжение |

|

U Д U оп |

(3.8) |

Аналогично требованию (3.2) должно выполняться условие |

|

UИП Uоп UБЭн |

(3.9) |

Выполнение условий (3.7) и (3.8) позволяет ЭП (рис.3.1) рассматривать в виде (рис.3.4). Если транзистор T1 закрыт (состояние “1” ЭП), то в цепи UД

ток будет практически отсутствовать, а когда Т1 открыт (состояние “0” ЭП),

то будет протекать ток считывания “0”.

60

I |

|

|

|

UИП Uоп UБЭн |

|

UИП Uоп UКЭн |

. |

(3.10) |

|

Д |

сч |

|

|

||||||

|

|

R3 |

R4 |

|

R1 |

|

|||

|

|

|

|

|

|

|

|

|

|

По окончании считывания напряжение UA понижается до значения U A0 и

ЭП переходит в режим хранения информации.

R1 |

R3 |

|

|

UИП |

|||

|

|

||

|

|

|

R2 R4

IК2

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

T1 |

|

|

|

|

|

T2 |

|

||||

|

|

|||||||||||

Iсч |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Э2 |

|

|

|

|

|

Э2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uоп |

||

|

|

UD |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.3.4. Активный режим (считывания/записи) в бистабильной ячейке

|

|

Выборка. |

Режим записи осуществляется, когда U |

A |

U1 . |

При этом на- |

||||||||

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

пряжение |

на входе D должно быть либо U |

Д |

U |

оп |

U |

Д |

U1 , либо |

|||||||

|

|

|

|

|

|

|

|

|

|

|

Д |

|||

U |

Д |

U |

оп |

U |

Д |

U 0 , в зависимости от характера записываемой в ЭП инфор- |

||||||||

|

|

|

Д |

|

|

|

|

|

|

|

|

|||

мации. Так как в режиме записи первые эмиттеры закрыты, как и при считы-

вании, то ЭП (рис.3.1) можно представить в виде рис.3.4. Рассмотрим процесс записи, начиная с исходного состояния, когда UД = Uoп, и открыт транзистор

Т1. В результате ток базы второго транзистора IБ2 = 0 и

UБЭ2 UД UКЭн Uоп |

|

U Д U oп UКЭн , |

(3.11) |

|

61

т.е. Т2 закрыт. При увеличении потенциала UД напряжение UБЭ2 также будет расти, что при достижении величины UБЭ2 = UБЭгр приведет к отпиранию тран-

зистора Т2. Это произойдет, когда

U Д U оп U БЭгр U КЭн . |

(3.12) |

В результате протекания через резистор R3 тока IК2 (рис.3.4) потенциал |

|

базы транзистора T1 уменьшится, напряжение UБЭ1 |

станет меньше величины |

UБЭгр и T1 закроется. ЭП переключится в состояние “1”. Если теперь понизить потенциал UA до величины U A0 , которое меньше чем Uoп, то ЭП перейдет в режим хранения, находясь в этом новом состоянии.

Рассмотрение процесса переключения ЭП из состояния “1” в состояние

“0” начнем с исходного состояния, когда UA UA1 , UД Uоп и открыт транзи-

стор Т2. В этом случае UБ1 = UК2 = Uoп + UКЭн, т.к. IБ1 = 0. Напряжение на р-n переходе база-эмиттер транзистора T1.

UБЭ1 UБ1 UД Uоп UКЭн UД U Д U oп UКЭн ,

т.е. T1 закрыт.

Для отпирания транзистора T1 напряжение на входе D необходимо умень-

шить до величины.

U Д U оп U БЭгр U КЭн , |

(3.13) |

что откроет его р-n переход база-эмиттер. Потечет ток эмиттера и коллектора

T1 (рис.3.4). В результате потенциал его коллектора уменьшится. Транзистор

Т2 закроется, a T1 перейдет в режим насыщения. Для того, чтобы зафиксиро-

вать это логическое состояние ЭП и предотвратить в дальнейшем его пере-

ключение при изменении UД, необходимо уменьшить потенциал UA до величины U A0 .

На основании проведенного анализа режимов работы ЭП (рис.3.1) можно сделать следующие выводы:

62