Cборник_ЛР

.pdf

минать” состояние на выходе в течение неограниченного времени (без отклю-

чения питания) позволяют использовать их в качестве элементов памяти.

Переключение триггеров под действием запускающего сигнала происхо-

дит скачкообразно, лавинообразно, формируется выходной сигнал с крутыми фронтами, поэтому их часто называют защелками (latch), спусковыми устрой-

ствами.

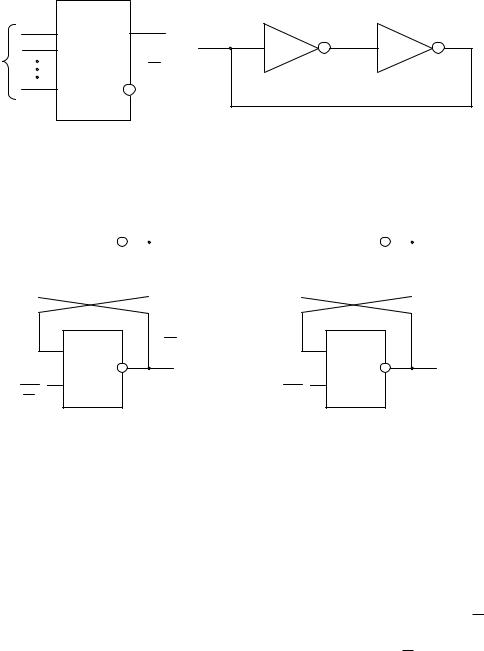

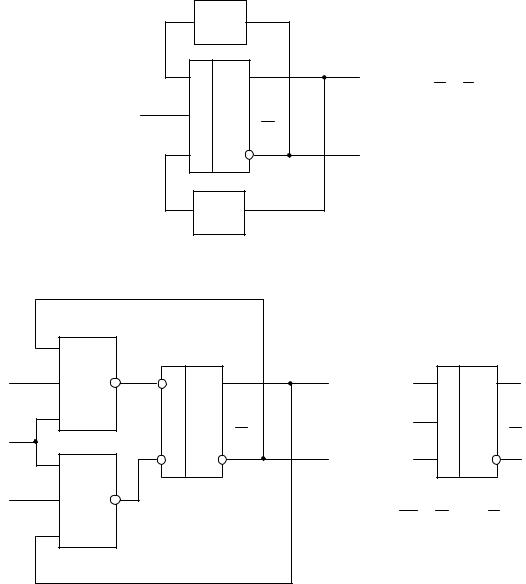

В общем случае триггерное устройство состоит из входной комбинацион-

ной логической схемы, формирующей команду управления триггером, и соб-

ственно триггерного элемента памяти.

Простейший триггер можно реализовать на вентилях, охваченных поло-

жительной обратной связью (ПОС), например, на элементах И-НЕ или ИЛИ-

НЕ, у которых, в соответствии с передаточной характеристикой, выполняются функции усиления и инверсии. На рис.7.1. показаны обобщенный триггерный элемент (а), реализация бистабильной ячейки на усилителях-инверторах (б),

схемы ячейки памяти (простейшие триггеры) на элементах 2И-НЕ (в) и 2ИЛИ-

НЕ (г).

Выходные переменные принято обозначать буквами Q и Q , можно запи-

сать постулат триггера [1]:

Q 1, Q 0,

Q 0, Q 1.

Входные логические переменные (в общем случае хi) обозначаются следу-

ющими символами:

S (set) - установка триггера (Q = 1),

R (reset) - сброс триггера (Q = 0),

J (jet) - вход установки универсального триггера (Q = 1),

K (key cancel) - вход сброса универсального триггера (Q = 0),

D (data) - информационный вход, данные,

T (takt) - счетный вход,

133

C (clock) - управляющий тактовый сигнал, синхросигнал,

Pr (precharge) - сигнал выборки, предзаряда, активизации триггера,

Cl (cleare) - сброс, очистка, стирание, установка в “0”-состояние,

V - сигнал блокирования работы триггера, сохранение ранее записанной информации.

|

Q |

xi |

Q |

|

|

|

|

|

|

|

а |

|

|

|

|

|

б |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

& |

|

|

Q |

1 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

Q |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

Q |

1 |

Q |

R |

|

R |

|

в |

|

г |

|

Рис.7.1. Обобщенный триггер (а), реализация триггерной ячейки памяти на усилителях-инверторах, охваченных ПОС (б), триггер на элементах

2И-НЕ (в), триггер на элементах 2ИЛИ-НЕ (г).

Триггер считается установленным (в состояние “1”), если Q = 1, Q = 0.

Триггер считается сброшенным (в состояние “0”), если Q = 0, Q = 1.

134

Комбинация возможных сочетаний входных логических переменных и выходных значений функции лежит в основе классификации типов триггеров по реализуемой логической функции. Некоторые сочетания переключающих сигналов и выходных состояний из всех возможных переборов (для конечного числа входов) никогда не используются, а некоторые применяются очень ши-

роко.

Наиболее широко применяются в микроэлектронике триггеры RS-,

RST(С)-, JK-, JKT- T-, TV-, D-, DC(Т)-, DV-типов.

Различают асинхронные и синхронные триггеры.

Асинхронные триггеры переключаются при изменении сигналов на ин-

формационных входах.

Синхронные триггеры переключаются только под действием определен-

ного активизирующего синхронизирующего сигнала (тактового сигнала, син-

хроимпульса, синхросигнала и т.д.).

Синхронизируемые триггеры могут быть:

статическими, они меняют состояние под действием либо высокого

(“1”), либо низкого (“0”) уровня синхросигнала. В течение разрешающего значения одного синхросигнала триггер может переключаться несколько раз под действием информационных сигналов в соответствии с логической функ-

цией.

динамическими, они переключаются при поступлении положитель-

ного (фронт) или отрицательного (срез) перепада синхронизирующего напря-

жения. За время действия одного синхроимпульса триггер может переклю-

читься только один раз.

Частота работы асинхронного триггера определяется только собственны-

ми задержками в логических элементах, на которых реализован данный триг-

гер. Частота изменения входных сигналов определяется временем завершения процесса переключения на выходах триггера.

135

Частота работы синхронного триггера определяется частотой синхросиг-

нала. Суммарные задержки логических элементов, на которых реализован триггер, должны обеспечить возможность реализации логической функции за время действия одного синхросигнала.

Работу конкретного триггера определяет логическая функция (характери-

стическое уравнение) или таблица состояний (переходов).

Входы триггера могут быть прямыми или инверсными, то есть действую-

щий переключающий сигнал может быть высоким (“1”) или низким (“0”).

Чаще всего это связано с элементной базой, в которой реализован триггер:

для элемента ИЛИ-НЕ сигнал “0” является пассивным, его появление не из-

меняет состояние триггера, а сигнал “1” - это активный сигнал, при его появ-

лении на выходе триггера будет состояние “0”. На схеме рис.7.1,г показан простейший триггер на ИЛИ-НЕ элементах. Входу S поставлен в соответствие выход Q . Для элементов И-НЕ сигнал “0” будет активным, так как при его появлении на входе элемента, на выходе появится “1”, триггер переключается

(рис.7.1,в).

Базовая триггерная ячейка RS-типа, показанная на рис.7.1,в,г, имеет вход S

установки в “1” и вход R установки в “0”. Сочетание значений входных пере-

менных S = “1”, R = “1” запрещено, поскольку на обоих выходах должны ус-

тановиться логические “0” и после окончания действия входных сигналов со-

стояние триггера будет неопределенным: в схеме с глубокой ПОС одинаковые состояния невозможны, а в какую сторону перебросится триггер - не известно.

Опишем работу RS-триггера при помощи логической функции и таблицы истинности:

Qn 1 S Qn R

Для схемы с инверсными информационными входами:

Qn 1 S Qn R

136

В таблице истинности (таблице переходов) демонстрируется, как исход-

ное состояние Qn триггера (n-ный такт работы) под действием входных пере-

менных меняется на Qn+1 состояние в (n+1)-такте работы в соответствии с ло-

гической функцией.

Таблица 7.1

Таблица состояний RS-триггера.

Таблица переходов RS-триггера

Qn |

S |

R |

Qn+1 |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

0 |

0 |

1 |

0 |

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

0 |

1 |

1 |

Неопределенность |

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

1 |

1 |

1 |

Неопределенность |

|

|

|

|

На рис.7.2 показана карта Карно для RS-триггера.

|

|

Qn |

|

|

|

|

|

S |

|

|

х |

|

х |

|

1 |

1 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

|

0 |

|

|

|

|

|

|

|

|

R

Рис.7.2. Карта Карно для RS-триггера

137

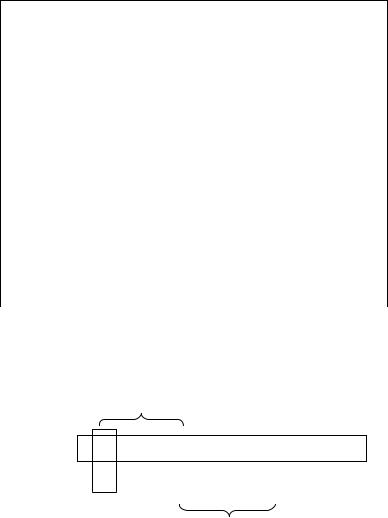

На рис.7.3 показана идеализированная тактовая диаграмма работы рас-

смотренного асинхронного RS-триггера с прямыми входами (ИЛИ-НЕ базо-

вые элементы).

S

t

R

t

Qn+1

t

Рис.7.3. Тактовая диаграмма работы идеализированного асинхронного RS-триггера

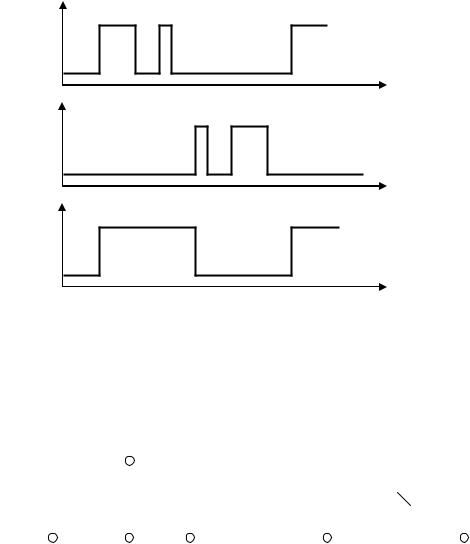

На рис.7.4 представлены виды условных обозначений RS-триггеров.

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

Q |

||||||||||||||

|

S |

T |

|

|

|

|

|

|

|

S |

T |

|

|

|

S |

T |

|

S |

T |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

Q |

||||||||||||||

|

R |

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

б |

|

|

|

|

в |

|

|

|

|

|

г |

||||||||||||||||||||||||||||

Рис.7.4. Условные обозначения RS-триггеров: асинхронный

с прямыми входами (а), асинхронный с инверсными входами (б),

синхронный с прямыми статическими входами (в), синхронный с прямыми динамическими входами, управляемый срезом (г)

138

RS- и RSТ-триггеры редко используют в качестве отдельного схемного уз-

ла из-за наличия неопределенных состояний на выходах схемы при одновре-

менных единицах на управляющих входах, но они являются базовыми эле-

ментами для построения других типов триггеров.

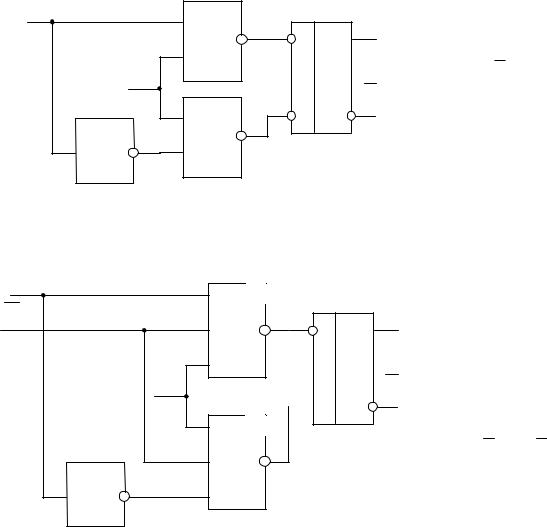

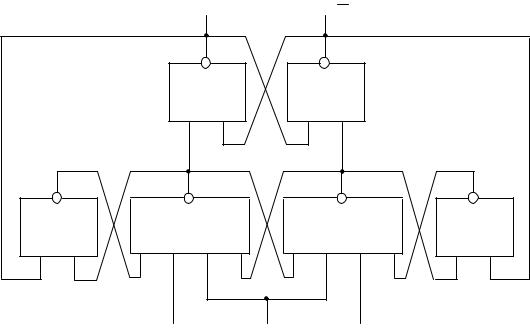

На рис.7.5, 7.6, 7.7, 7.8 показаны структурные схемы наиболее распро-

страненных типов триггерных схем: D-триггер, DV-триггер, Т-триггер, JK-

триггер соответственно. |

|

|

|

D |

& |

|

|

|

|

Q |

|

|

|

|

|

|

|

S |

T |

C |

|

|

Qn+1 = CD + C Qn |

|

& |

|

Q |

|

R |

|

|

1 |

|

|

|

|

|

|

Рис.7.5. Триггер D-типа (задержки, хранения), статический

на RS-триггере

D |

|

& |

|

V |

Q |

S |

T |

C |

Q |

|

R

R

&

Qn+1 = V(CD + C Qn)+V Qn

1

Рис.7.6 Триггер DV-типа с блокировкой на RS-триггере

139

зд

Q

S T

Qn+1 = ТQn+TQn

C≡T

Q

R

зд

Рис.7.7. Схема Т-триггера (счетного) на RS-триггере

J |

& |

Q |

|

Q |

|

S |

T |

J |

J T |

C |

|

Q |

= C |

Q |

|

|

|

||

|

R |

|

K |

K |

K |

& |

|

|

|

|

|

|

|

Qn 1 C J Qn KQn CQn

Рис.7.8. Структурная схема универсального статического

JK-триггера на RS-триггере

JK-ТРИГГЕР.

На рис.7.8 показано обозначение схемы JK-триггера и простейшая струк-

турная схема этого элемента. Показан вариант синхронизируемой схемы со статическим управлением (уровнем синхросигнала). Широкое применение

140

схемы JK-триггера обусловлено тем, что в его работе нет запрещенных со-

стояний на входах: таблица состояний показана в табл.7.2.

Таблица 7.2

Полная таблица переходов (состояний) в JK-триггере.

J |

K |

Qn |

Qn+1 |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

0 |

0 |

1 |

1 |

|

|

|

|

0 |

1 |

0 |

0 |

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

В рассматриваемой схеме J - сигнал установки, K - сигнал сброса тригге-

ра. При поступлении на оба информационных входа единичных сигналов со-

стояние на выходах инвертируется, т.е. триггер работает как счетный (Т-типа).

|

На |

основе |

|

JK-триггера |

можно |

|

построить |

основные |

типы |

триггеров |

||||||||||||||||||||||||||||||||||||

(рис.7.9), поэтому он называется универсальным. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

S |

|

|

|

|

Q |

|

D |

|

|

|

|

Q “1” |

|

|

|

Q |

V |

|

|

|

|

Q |

||||||||||||||||||||||||

J |

|

TT |

|

J |

TT |

|

|

J |

TT |

J |

TT |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

C |

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

T |

|

|

|

|

|

||||||||||||||||||||

C |

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

R |

|

|

Q |

|

|

|

|

Q |

|

|

Q |

|

|

|

Q |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

|

|

|

г |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

Рис.7.9. Построение триггеров на основе JK-триггера:

а - синхронный RS-триггер; б - DC-триггер; в - синхронный

Т-триггер; г - синхронный ТV-триггер

141

Триггеры с динамическим управлением характеризуются более устойчи- |

||||

вой работой, потому что переключаются только в промежуток времени фрон- |

||||

та или среза синхросигнала. Чаще всего динамические триггеры строят либо |

||||

по схеме |

трех триггеров, |

работающие по |

фронту, |

либо по схеме “M-S” |

(Master - Slave): основной - вспомогательный, ведущий - ведомый. |

||||

Входной каскад динамического триггера (трехтриггерного или “по фрон- |

||||

ту”) состоит из входного синхронного триггера, на который поступают управ- |

||||

ляющие сигналы, и двух асинхронных триггеров (коммутирующие биста- |

||||

бильные ячейки, БЯ), в которых запоминаются сигналы, действовавшие на |

||||

входе в момент изменения синхросигнала. На рис.7.10 показана структурная |

||||

схема динамического JK-триггера с переключением по фронту. |

||||

|

Q |

|

Q |

|

|

& |

& |

|

|

& |

& |

& |

|

& |

|

J |

C |

K |

|

|

|

|

|

|

|

Рис.7.10. JK-триггер с динамическим управлением |

|||

|

с коммутирующими БЯ |

|

||

Триггеры “М-S”-типа нашли широкое применение в схемотехнике ЦИС,

по такой схеме строятся многотактные триггерные устройства. Основной триггер (Мaster) принимает информацию, вспомогательный (Slave) - фиксиру-

142